Untitled

Syllabus

Catalog Description

CS 150. Components and Design Techniques for

Digital

Systems. (5)

Three hours of lecture, one hour of discussion, and three

hours of

laboratory per week. Prerequisites: 61C, Electrical Engineering 40 or

42. Basic

building blocks and design methods to contruct synchronous digital

systems.

Alternative representations for digital systems. Bipolar TTL vs. MOS

implementation technologies. Standard logic (SSI, MSI) vs. programmable

logic

(PLD, PGA). Finite state machine design. Digital computer building

blocks as

case studies. Introduction to computer-aided design software. Formal

hardware

laboratories and substantial design project. Informal software

laboratory

periodically throughout semester. (F,SP) Katz, Newton, Pister.

Course Goals

- Understand digital

logic at the gate and switch level including both combinational and

sequential logic elements.

- Understand

clocking methodologies to manage information flow and preservation of

circuit state.

- Appreciate digital

logic specification methods and the compilation process that transforms

these into logic networks.

- Gain experience

with computer-aided design tools for implementation with programmable

logic devices.

- Appreciate the

advantages/disadvantages between hardware and software implementations

of a function.

Course Textbook

R. H. Katz, G.

Borriello, Contemporary Logic Design, 2nd Ed., Pearson Prentice-Hall, Upper

Saddle

River, NJ, 2005.

Contemporary

Logic Design, Second Edition

Course Grading

Homework: 10%

Quizzes: 5%

Labs 1-5: 15%

Midterms (2): 20%

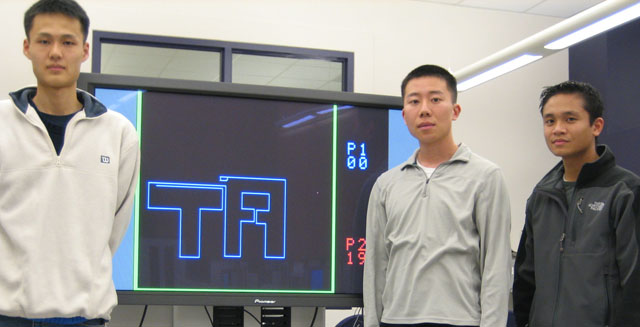

Final Project (including project Checkpoints 1, 2, 3): 30%

Final Exam: 20%

Project Breakdown

TBA

Homework and Quiz Policy

Homework will be graded

on effort. They will be due in the homework box outside of 125 Cory before lab

lecture at 2:10P each Friday.

Quizzes based on homework

will be given each Thursday in lecture. No make-up quizzes!

Public Discussion

Post/receive announcements, questions, and discussions on UseNet news group ucb.class.cs150. The

staff will be using Google Groups to view the newsgroup, so we recommend that

you do the same.

| UC Berkeley |

http://www-inst.eecs.berkeley.edu/~cs150/ |

EECS 150 Fall 2006 |