Untitled

| ||||||

Project

The project will be a wireless, 2-player game. It will be separated into 4 checkpoints.

- Checkpoint 1: N64 Controller

- 1 Week

- Checkpoint 2: Video Encoder

- 1 Week

- Checkpoint 3: Chipcon Wireless Tranceiver

- 2 Weeks

- Checkpoint 4: Game Engine

- Due at Time of Project Check-off

Project Schedule and Grading Summary

Final Check-off Instructions

Project Report Guidelines and Partner Evaluation

Sheets

Project Files

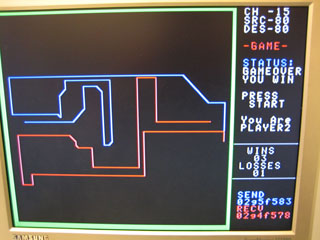

Tron Demo - This is the TA solution for CP4, which will be tested against your own solution for final checkoff. Read the included readme file for details. The zip file includes 2 versions, one with speed=10 and one with speed=40 (only speed 10 is required for checkoff).

Game Tester - This contains black boxes for checkpoints 2, 3, and 4. Follow the instructions in the included DOC file to run wireless tron with your Checkpoint 1 N64.v module. We will use this tester to verify that your CP1, CP2, and CP3 modules work!

Wireless Tron Demo - Demo BIT file for the Game Tester project files. Follow the included instructions to set it up.

New Transceiver Blackbox

The following transceiver blackbox contains the updated SPI that supports passing SClk, SI, SO, and CS_ through IO registers: Transceiver.edn.

New SPI Blackbox and IO Register Information

Use this new SPI.edn blackbox if you are encounterting unexplainable logic glitches while coding up checkpoint 4. This version of SPI supports the delays introduced by passing SClk, SI, SO, and CS_ through IO registers. An example of a glitch is if an FSM transitions to state x (e.g. 0) from another state, although no transition edge connects the states, and remains in state x even when a condition to transition out of it occurs.

Most importantly, pass RF_SCLK, RF_SI, RF_SO, and RF_CS_ through IO registers. Other code is unchanged. For example:

wire sClkTemp, siTemp, cs_Temp, soDelay;

IORegister sClkDelay(.Clock(Clock), .Reset(Reset),

.Set(1'b0), .Enable(1'b1),

.In(sClkTemp), .Out(RF_SCLK)),

siDelay(.Clock(Clock), .Reset(Reset),

.Set(1'b0), .Enable(1'b1),

.In(siTemp), .Out(RF_SI)),

soDelay(.Clock(Clock), .Reset(Reset),

.Set(1'b0), .Enable(1'b1),

.In(RF_SO), .Out(soDelay)),

cs_Delay(.Clock(Clock), .Reset(Reset),

.Set(1'b0), .Enable(1'b1),

.In(cs_Temp), .Out(RF_CS_));

defparam sClkDelay.width = 1,

siDelay.width = 1,

soDelay.width = 1,

cs_Delay.width = 1;

Tranceiver chipcon(.In(), .Start(), .REn(), .Channel(),

.SrcAddr(), .DestAddr(),

.Out(), .NewData(), .Ready(),

.FIFO(), .FIFOP(), .SFD(), .CCA(),

.SClk(sClkTemp), .CS_(cs_Temp), .SI(siTemp),

.SO(soDelay),

.VReg_En(), .Rf_Reset_(),

.Clock(), .Reset());

If this does not solve the problem, try passing VREG_EN and RF_RESET_ through IO registers. Also try replacing your Transceiver module with the blackbox provided in Gametester. If the blackbox solves your glitching problem, send David an e-mail.

N64 Controller Rumble Pack

Issue the following commands to cause the N64 controller to "rumble." Only the clear blue controllers have the rumble pack built in.

Initialization: 8'h03, 8'h80, 8'h01, {32{8'h80}}, [stop bit]

Turn on rumble pack: 8'h03, 8'hC0, 8'h1B, {32{8'h01}}, [stop bit]

Turn off rumble pack: 8'h03, 8'hC0, 8'h1B, {32{8'h00}},

The first byte initiates writes to the controller pack. The second byte is the memory address. The 4th to 35th bytes are the data written to memory.

Credit for finding the command sequence for activating the rumble pack goes to Fall 2005 CS150 students!

| UC Berkeley | http://www-inst.eecs.berkeley.edu/~cs150/ | EECS 150 Fall 2006 |