# EECS 151/251A Homework 1

Due Monday, Jan 30<sup>th</sup>, 2023

## Problem 1: Pareto Optimal Frontier

John did a design space exploration for his design of a digital widget and came up with the following table of results for frequency (number of operations per sec) in GHz, energy in nanoJoules per operation, and cost as chip area in mm<sup>2</sup>. List those rows that represent design points that lie on the Pareto optimal frontier.

(Update (1/26): Changed "energy efficiency" to "energy" in the text. It doesn't affect the answer of this problem since the unit is already shown. This change intends to remove the ambiguity of the term "energy efficiency".)

| Frequency | Energy | Cost |

|-----------|--------|------|

| 3         | 30     | 4    |

| 3         | 20     | 3    |

| 3         | 15     | 3    |

| 2         | 20     | 3    |

| 2         | 20     | 2    |

| 2         | 10     | 1    |

| 1         | 10     | 2    |

| 1         | 10     | 1    |

## Solution:

Rows on the optimal frontier:

| Frequency | Energy | Cost |

|-----------|--------|------|

| 3         | 15     | 3    |

| 2         | 10     | 1    |

(3, 15, 3) is better than (3, 30, 4) in energy and cost, better than (3, 20, 3) in energy, and better than (2, 20, 3) in frequency and energy. Among the rest of designs, (2, 10, 1) is better than (2, 20, 2) in cost, better than (1, 10, 2) in frequency and cost, and better than (1, 10, 1) in frequency.

# Problem 2: Dennard Scaling

Imagine the world where Dennard scaling works completely. You were asked to add some features to a processor that originally works at 100MHz with 10W, and the modification you made

did not change the frequency but increased the power 20%. If you fabricate this design with a new technology, which has been scaled by a factor of 0.5, what will be the frequency and power consumption?

## Solution:

200MHz and 3W. According to Dennard scaling, the frequency will increase 2x with the same power density. The power has been increased to 12W by your modification, but in the new technology each transistor is 4x smaller and so is the die area. Therefore, the power consumption is a quarter of 12W, that is 3W.

## Problem 3: Die Cost

You are fabricating  $150\,\mathrm{mm}^2$  dies on  $300\,\mathrm{mm}$  wafers with  $\alpha=3$  and a defect per unit area  $0.005\,/\mathrm{mm}^2$ . Each wafer costs \$20k. How much does each die cost?

Solution: Die Yield =

$$\left(1 + \frac{0.005 / \text{mm}^2 \cdot 150 \, \text{mm}^2}{3}\right)^{-3} = 0.512$$

Dies per wafer =  $\frac{\pi \cdot (300 \, \text{mm}/2)^2}{150 \, \text{mm}^2} - \frac{\pi \cdot 300 \, \text{mm}}{\sqrt{2 \cdot 150 \, \text{mm}^2}} \approx 417$

Die Cost =

$$\frac{\$20,000}{417 \cdot 0.512} \approx \$94$$

## Problem 4. Boolean Functions

All functions in this problem are single-output Boolean functions.

- (a) How many unique single-input functions exist?

- (b) In general, any (k+1)-input function can be decomposed into a pair of k-input functions. For example, a function  $x(i_0, \ldots, i_k)$  can be decomposed into  $y(i_0, \ldots, i_{k-1})$  and  $z(i_0, \ldots, i_{k-1})$ , where

$$x(i_0, \dots, i_k) = \begin{cases} y(i_0, \dots, i_{k-1}) & \text{if } i_k = 0 \\ z(i_0, \dots, i_{k-1}) & \text{if } i_k = 1 \end{cases}$$

Assume that there are n unique functions with k inputs. How many unique function are there with k+1 inputs? Do not use k in your answer. (Hint: Consider how many 2-input functions you can compose from unique single-input functions.)

#### Solution:

- (a) 4 (constant 0, constant 1, a, and  $\bar{a}$  for input a).

- (b)  $n^2$ . For each pair of y and z chosen from k-input functions (you may choose the same function for y and z), the composed x is different. Since there are  $n \times n$  pairs, we derive

$n^2$  different (k+1)-input functions. As stated, there are no (k+1)-input functions that cannot be composed in this way. Therefore, there are  $n^2$  unique (k+1)-input functions and no more.

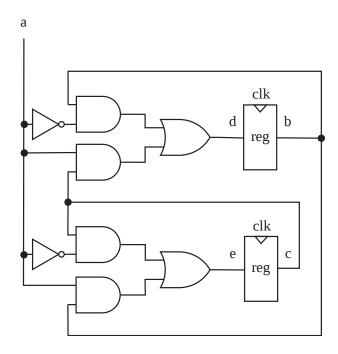

# Problem 5. Sequential Logic Circuit

For the sequential logic circuit with input a and output f shown below,

- (a) Show the truth table of the combinational part (use a, b, and c as input, and d and e as output).

- (b) Complete the following table.

| cycle | 0 | 1 | 2 | 3 | 4 |

|-------|---|---|---|---|---|

| a     | 0 | 1 | 1 | 0 | 1 |

| b     | 1 | 1 | 0 |   |   |

| c     | 0 | 0 | 1 |   |   |

| d     | 1 | 0 |   |   |   |

| e     | 0 | 1 |   |   |   |

Solution:

|     |     | a        | b | $\mathbf{c}$ | d | e |   |

|-----|-----|----------|---|--------------|---|---|---|

|     |     | 0        | 0 | 0            | 0 | 0 |   |

|     |     | 0        | 0 | 1            | 0 | 1 |   |

|     |     | 0        | 1 | 0            | 1 | 0 |   |

|     | (a) | 0        | 1 | 1            | 1 | 1 |   |

|     |     | 1        | 0 | 0            | 0 | 0 |   |

|     |     | 1        | 0 | 1            | 1 | 0 |   |

|     |     | 1        | 1 | 0            | 0 | 1 |   |

|     |     | 1        | 1 | 1            | 1 | 1 |   |

|     |     |          |   | -            | 0 | 0 |   |

|     | cy  | cle      | 0 | 1            | 2 | 3 | 4 |

|     | (   | $a \mid$ | 0 | 1            | 1 | 0 | 1 |

| (b) | l   | b        | 1 | 1            | 0 | 1 | 1 |

| (6) | (   | c        | 0 | 0            | 1 | 0 | 0 |

|     | (   | d        | 1 | 0            | 1 | 1 | 0 |

|     | (   | 9        | 0 | 1            | 0 | 0 | 1 |

# Problem 6: Rank order for NRE, Recurring Costs, Flexibilty, Performance

Imagine you are designing a product with embedded processing. Your job is to choose the appropriate implementation approach for the processing part of your product. You are given the following choices. Rank order the following design alternatives by filling in the table with 1,2,3,4 representing the relative ranking (1 being the lowest and 4 being the highest). Rank based on the best-case design in each category. If there is a tie, use the lower number (e.g. if tied for 2 or 3, use 2). Flexibility means flexibility after fabrication. Per-die cost of Processor is not required.

|                   | Full-Custom | Std Cell ASIC | FPGA | Processor |

|-------------------|-------------|---------------|------|-----------|

| NRE Cost          |             |               |      |           |

| Performance       |             |               |      |           |

| Energy Efficiency |             |               |      |           |

| Per Die Cost      |             |               |      | _         |

| Flexibility       |             |               |      |           |

| Solution: |                   |             |               |      |           |  |

|-----------|-------------------|-------------|---------------|------|-----------|--|

|           |                   | Full-Custom | Std Cell ASIC | FPGA | Processor |  |

|           | NRE Cost          | 4           | 3             | 2    | 1         |  |

|           | Performance       | 4           | 3             | 2    | 1         |  |

|           | Energy Efficiency | 4           | 3             | 2    | 1         |  |

|           | Per Die Cost      | 1           | 2             | 3    | -         |  |

|           | Flexibility       | 1           | 1             | 2    | 2 (or 3)  |  |

## Problem 7: Processor vs. FPGA vs. ASIC

You are the Chief Technical Officer of a new startup, the Orange Scooter Company. As the chief design lead of your (admittedly small) team of engineers, it is up to you to adopt which one from Processors, FPGAs, or ASICs for your upcoming line of scooters. After getting quotes from several foundries and having a chat with the Head of HR about the estimated number of work hours needed for each choice, you arrive at the following conclusions for the NRE and per-unit cost associated with each approach.

|           | NRE Cost | Per Unit Cost |

|-----------|----------|---------------|

| Processor | \$5K     | \$200         |

| FPGA      | \$20K    | \$100         |

| ASIC      | \$1M     | \$2           |

- (a) As a small startup, you don't anticipate your first deployment to be too large, and the Head of Marketing (who also happens to be Head of HR) estimates that you will deploy about 100 units in the first quarter. Which type of design would you choose? Why?

- (b) In what range of units to deploy would FPGA be the best option?

#### Solution:

(a) Processor.

$$ProcessorCost = 5,000 + 200 \times 100 = 25,000$$

$$FPGACost = 20,000 + 100 \times 100 = 30,000$$

$$ASICCost = 1,000,000 + 2 \times 100 = 1,000,200$$

(b) 150 < N < 10,000

The number of deployed units when Processor and FPGA have the same cost:

$$5,000 + 200 \cdot N = 20,000 + 100 \cdot N \tag{1}$$

$$100 \cdot N = 15,000 \tag{2}$$

$$N = 150 \tag{3}$$

Same between FPGA and ASIC:

$$20,000 + 100 \cdot N = 1,000,000 + 2 \cdot N \tag{4}$$

$$98 \cdot N = 980,000 \tag{5}$$

$$N = 10,000 (6)$$

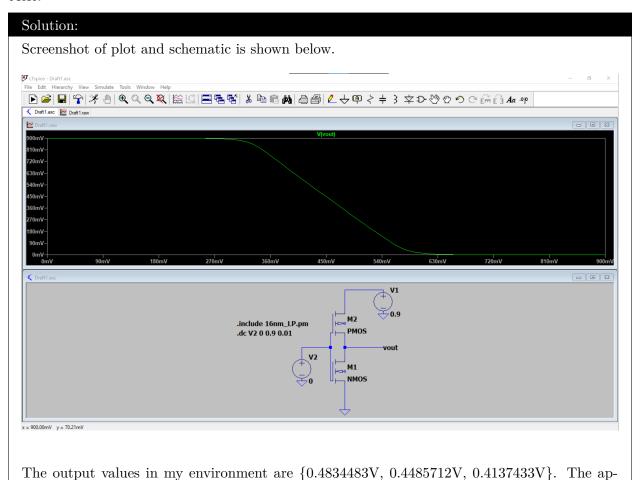

# Problem 8: Voltage Transfer Curve (VTC) of Inverter in SPICE

Using SPICE DC Analysis, plot the VTC of an inverter using the 16nm process technology provided on http://ptm.asu.edu/modelcard/LP/16nm\_LP.pm. The nominal supply voltage for this process

is 0.9 V. Use a length of 16 nm for both devices and a width of 300 nm for PMOS and 80 nm for NMOS. Don't forget to connect the body of the devices to the correct voltages - NMOS body to GND and PMOS body to VDD!

Report the value of output (vout) when the input is {0.44V, 0.45V, 0.46V}. What is the approximate slope in the range (0.44V, 0.46V)? For help setting up the simulation, follow the LTspice tutorial on the class website. https://inst.eecs.berkeley.edu/~eecs151/sp20/files/spice\_tutorial.pdf. You can export the values of datapoints in the plot by File > Export data as text.

proximate slope of the range is (0.4137433 - 0.4834483) / 0.02 = -3.48525.