EECS 151/251A Spring 2019 Digital Design and Integrated Circuits

Instructor: John Wawrzynek

Lecture 6

# Outline

#### Three representations for combinational logic:

- truth tables,

- graphical (logic gates), and

- algebraic equations

- Boolean Algebra

- Boolean Simplification

- Multi-level Logic, NAND/NOR, XOR

### **Representations of Combinational Logic**

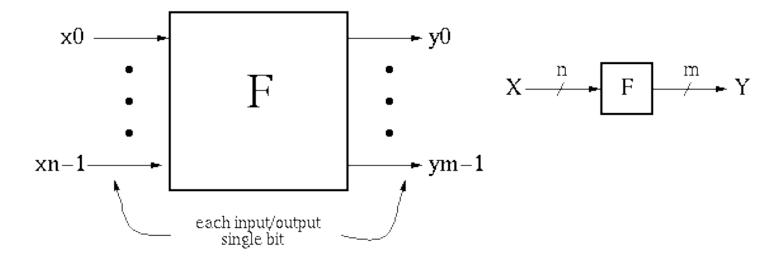

# **Combinational Logic (CL) Defined**

$y_i = f_i(x0, ..., xn-1)$ , where x, y are {0,1}. Y is a function of only X.

If we change X, Y will change immediately (well almost!).

There is an *implementation dependent* delay from X to Y.

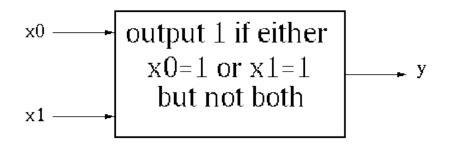

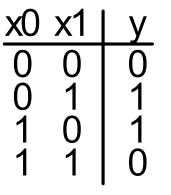

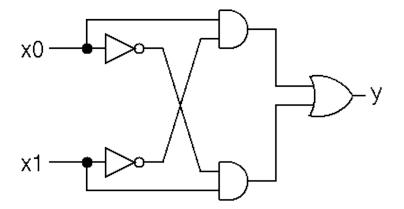

# CL Block Example #1

Boolean Equation:  $y_0 = (x_0 \text{ AND not}(x_1))$ OR (not(x\_0) AND x\_1)  $y_0 = x_0x_1' + x_0'x_1$

Truth Table Description:

Gate Representation:

How would we prove that all three representations are equivalent?

### **Boolean Algebra/Logic Circuits**

### Why are they called "logic circuits"?

- □ Logic: The study of the principles of reasoning.

- The 19th Century Mathematician, George Boole, developed a math. system (algebra) involving logic, Boolean Algebra.

- □ His variables took on TRUE, FALSE

- Later Claude Shannon (father of information theory) showed (in his Master's thesis!) how to map Boolean Algebra to digital circuits:

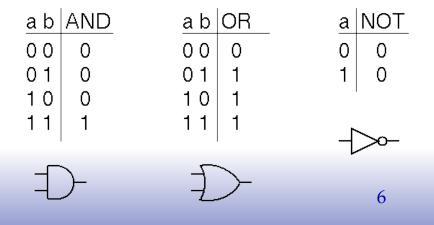

- Primitive functions of Boolean Algebra:

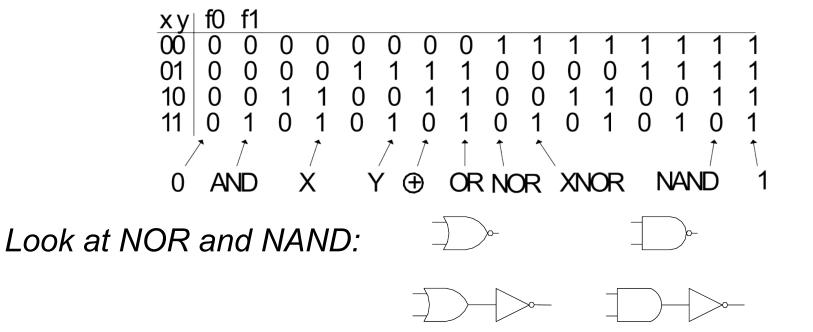

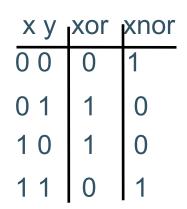

#### Other logic functions of 2 variables (x,y)

- Theorem: Any Boolean function that can be expressed as a truth table can be expressed using NAND and NOR.

- Proof sketch:

$$- = NOT \qquad = - = AND$$

$$= - = OR$$

How would you show that either NAND or NOR is sufficient?

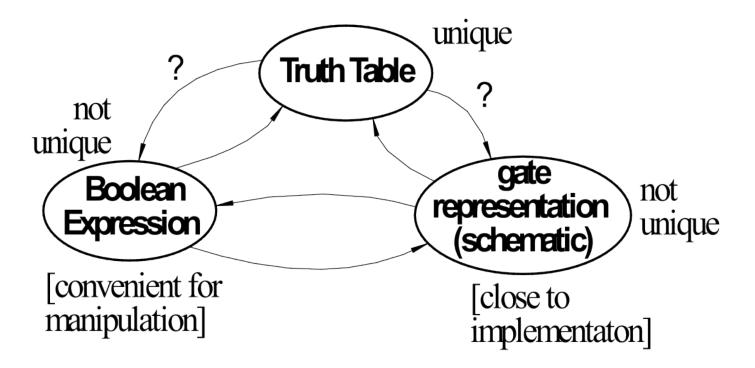

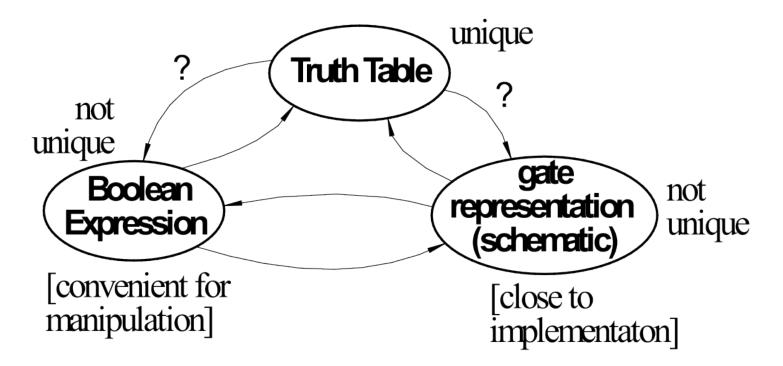

# **Relationship Among Representations**

\* Theorem: Any Boolean function that can be expressed as a truth table can be written as an expression in Boolean Algebra using AND, OR, NOT.

How do we convert from one to the other?

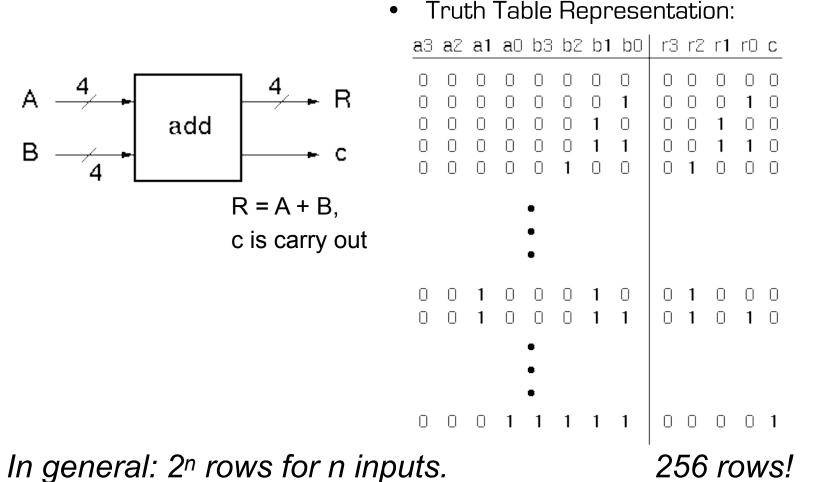

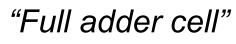

# CL Block Example – 4 Bit Adder

Is there a more efficient (compact) way to specify this function?

#### **4-bit Adder Example**

Motivate the adder circuit design by hand addition:

□ Add a0 and b0 as follows:

| a b                      |           |

|--------------------------|-----------|

| 0 0<br>0 1<br>1 0<br>1 1 | 0 0 stage |

| 01                       | 1 0       |

| 1 0                      | 1 0       |

| 1 1                      | 01        |

| r = a                    | XOR       |

• Add a1 and b1 as follows:

|   | сі    | а          | b          | l r              | СО              |

|---|-------|------------|------------|------------------|-----------------|

|   | 0     | 0          | 0          | 0                | 0               |

|   | 0     | 0          | 1          | 1                | 0               |

|   | 0     | 1          | 0          | 1                | 0               |

|   | 0     | 1          | 1          | 0                | 1               |

|   | 1     | 0          | 0          | 1                | 0               |

|   | 1     | 0          | 1          | 0                | 1               |

|   | 1     | 1          | 0          | 0                | 1               |

|   | 1     | 1          | 1          | 1                | 1               |

| ľ | r = ; | <b>a</b> ⊕ | <b>b</b> ⊕ | ) C <sub>i</sub> |                 |

| ( | CO =  | = at       | ) + (      | $aC_i +$         | bc <sub>i</sub> |

### **4-bit Adder Example** □ In general: $r_i = a_i \oplus b_i \oplus c_{in}$ $c_{out} = a_i c_{in} + a_i b_i + b_i c_{in} = c_{in}(a_i + b_i) + a_i b_i$

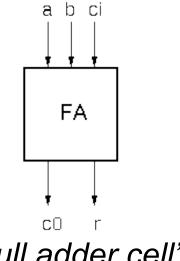

□ Now, the 4-bit adder:

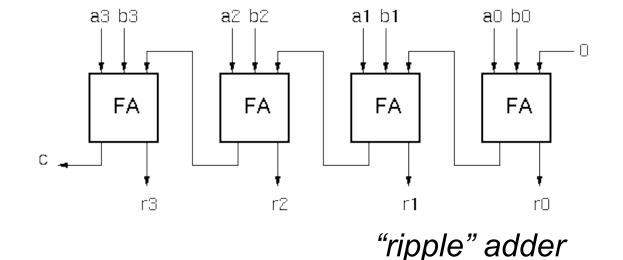

### 4-bit Adder Example

□ Graphical Representation of FA-cell  $r_i = a_i \oplus b_i \oplus c_{in}$  $c_{out} = a_i c_{in} + a_i b_i + b_i c_{in}$

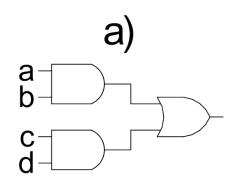

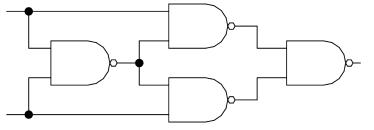

• Alternative Implementation (with only 2-input gates):

$$\mathbf{r_i} = (\mathbf{a_i} \oplus \mathbf{b_i}) \oplus \mathbf{c_{in}}$$

$$c_{out} = c_{in}(a_i + b_i) + a_i b_i$$

### **Boolean Algebra**

#### **Boolean Algebra**

Set of elements *B*, binary operators  $\{+, \bullet\}$ , unary operation  $\{'\}$ , such that the following axioms hold :

- 1. *B* contains at least two elements *a*, *b* such that  $a \neq b$ .

- 2. Closure : a, b in B,

a + b in B,  $a \bullet b$  in B, a' in B.

3. Communitive laws :

$$a+b=b+a, a \bullet b=b \bullet a.$$

4. Identities : 0, 1 in B

$a + 0 = a, \quad a \bullet 1 = a.$

5. Distributive laws :

$$a + (b \bullet c) = (a + b) \bullet (a + c), \ a \bullet (b + c) = a \bullet b + a \bullet c.$$

6. Complement :

$$a + a' = 1, \ a \bullet a' = 0$$

$B = \{0,1\}, + = OR, \bullet = AND, ' = NOT$ is a valid Boolean Algebra.  $D = 00|0 \qquad 00|0 \qquad 0|1 \\ 01|1 \qquad 01|0 \qquad 1|0 \\ 10|1 \qquad 10|0 \\ 11|1 \qquad 11|1 \qquad 01|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11|0 \\ 11$

# Some Laws of Boolean Algebra

Duality: A dual of a Boolean expression is derived by interchanging OR and AND operations, and 0s and 1s (literals are left unchanged).

$$\{F(x_1, x_2, ..., x_n, 0, 1, +, \bullet)\}^D = \{F(x_1, x_2, ..., x_n, 1, 0, \bullet, +)\}$$

Any law that is true for an expression is also true for its dual.

Operations with 0 and 1: x + 0 = x x \* 1 = x x + 1 = 1 x \* 0 = 0Idempotent Law: x + x = x x = xInvolution Law: (x')' = xLaws of Complementarity: x + x' = 1 x = x' = 0Commutative Law: x + y = y + x x = y = y = x

# Some Laws of Boolean Algebra (cont.)

Associative Laws: (x + y) + z = x + (y + z)

Distributive Laws: x (y + z) = (x y) + (x z)

"Simplification" Theorems: x y + x y' = x x + x y = x x y z = x (y z)

x + (y z) = (x + y)(x + z)

(x + y) (x + y') = xx (x + y) = x

DeMorgan's Law: (x + y + z + ...)' = x'y'z'

(x y z ...)' = x' + y' +z'

Theorem for Multiplying and Factoring: (x + y) (x' + z) = x z + x' yConsensus Theorem: x y + y z + x' z = (x + y) (y + z) (x' + z)x y + x' z = (x + y) (x' + z)

# **DeMorgan's Law**

| (x + y)' = x' y' | Exhaustive<br>Proof | x y x' y'<br>0 0 1 1<br>0 1 1 0<br>1 0 0 1<br>1 1 0 0            | $ \begin{array}{cccc} (x + y)' & x'y' \\ 1 & 1 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \end{array} $ |

|------------------|---------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| (x y)' = x' + y' | Exhaustive<br>Proof | x y x' y'<br>0 0 1 1<br>0 1 1 0<br>1 0 0 1<br>1 0 0 1<br>1 1 0 0 | (x y)' x' + y'  1 1  1 1  1 1  1 0 0                                                    |

# **Relationship Among Representations**

\* Theorem: Any Boolean function that can be expressed as a truth table can be written as an expression in Boolean Algebra using AND, OR, NOT.

How do we convert from one to the other?

# **Canonical Forms**

Standard form for a Boolean expression - unique algebraic expression directly from a true table (TT) description.

Two Types:

- \* Sum of Products (SOP)

- \* Product of Sums (POS)

- <u>Sum of Products</u> (disjunctive normal form, <u>minterm</u> expansion). Example:

| Minterms | a b c | ff' |                                         |

|----------|-------|-----|-----------------------------------------|

| a'b'c'   | 0 0 0 | 01  |                                         |

| a'b'c'   | 0 0 1 | 01  | One product (and) term for each 1 in f: |

| a'bc'    | 0 1 0 | 01  | f = a'bc + ab'c' + ab'c + abc' + abc    |

| a'bc     | 0 1 1 | 10  | f' = a'b'c' + a'b'c + a'bc'             |

| ab'c'    | 1 0 0 | 10  |                                         |

| ab'c     | 101   | 10  |                                         |

| abc'     | 1 1 0 | 10  | What is the cost?                       |

| abc      | 111   | 10  |                                         |

|          |       |     |                                         |

# Sum of Products (cont.)

Canonical Forms are usually not minimal:

Our Example:

f = a'bc + ab'c' + ab'c + abc' + abc (xy' + xy = x)= a'bc + ab' + ab = a'bc + a (x'y + x = y + x) = a + bc

```

f' = a'b'c' + a'b'c + a'bc'

= a'b' + a'bc'

= a' (b' + bc')

= a' (b' + c')

= a'b' + a'c'

```

# **Canonical Forms**

• <u>Product of Sums</u> (conjunctive normal form, <u>maxterm</u> expansion). Example:

| maxterms    | a b_c_ | f f'                                                           |

|-------------|--------|----------------------------------------------------------------|

| a+b+c       | 0 0 0  | 01                                                             |

| a+b+c′      | 0 0 1  | 0 1 One sum ( <b>or</b> ) term for each <b>0</b> in f:         |

| a+b '+c     | 0 1 0  | 0 1 $f = (a+b+c)(a+b+c')(a+b'+c)$                              |

| a+b '+c '   | 0 1 1  | $1 0 \qquad f' = (a+b'+c')(a'+b+c)(a'+b+c') (a'+b'+c)(a+b+c')$ |

| a '+b+c     | 1 0 0  | 1 0                                                            |

| a '+b+c '   | 1 0 1  | 1 0                                                            |

| a '+b '+c   | 1 1 0  | 1 0                                                            |

| a '+b '+c ' | 1 1 1  | 1 0                                                            |

|             |        | I                                                              |

### Boolean Simplification

# **Algebraic Simplification Example**

- Ex: full adder (FA) carry out function (in canonical form):

- Cout = a'bc + ab'c + abc' + abc

# **Algebraic Simplification**

Cout = a'bc + ab'c + abc' + abc

- = a'bc + ab'c + abc' + abc + abc

- = a'bc + abc + ab'c + abc' + abc

- = (a' + a)bc + ab'c + abc' + abc

- = **[1]**bc + ab'c + abc' + abc

- = bc + ab'c + abc' + abc + abc

- = bc + ab'c + abc + abc' + abc

- = bc + a(b' +b)c + abc' +abc

- = bc + a[1]c + abc' + abc

- = bc + ac + ab[c' + c]

- = bc + ac + ab[1]

- = bc + ac + ab

# **Outline for remaining CL Topics**

- K-map method of two-level logic simplification

- Multi-level Logic

- NAND/NOR networks

- EXOR revisited

### Algorithmic Two-level Logic Simplication Key tool: <u>The Uniting Theorem</u>:

$$xy' + xy = x(y' + y) = x(1) = x$$

| ab | f                 | f = ab' + ab = a(b'+b) = a             |

|----|-------------------|----------------------------------------|

| 00 | 0                 | b values change within the on-set rows |

| 01 | 0                 | a values don't change                  |

| 10 | 1                 |                                        |

| 11 | 1                 | b is eliminated, a remains             |

| ab | a                 | g = a'b'+ab' = (a'+a)b' =b'            |

| 00 | <del>3</del><br>1 |                                        |

|    |                   | b values stay the same                 |

| 01 | 0                 |                                        |

| 10 | 1                 | a values changes                       |

b' remains, a is eliminated

11 0

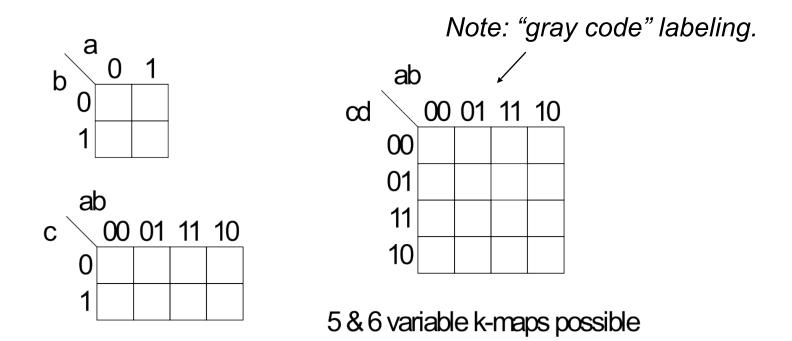

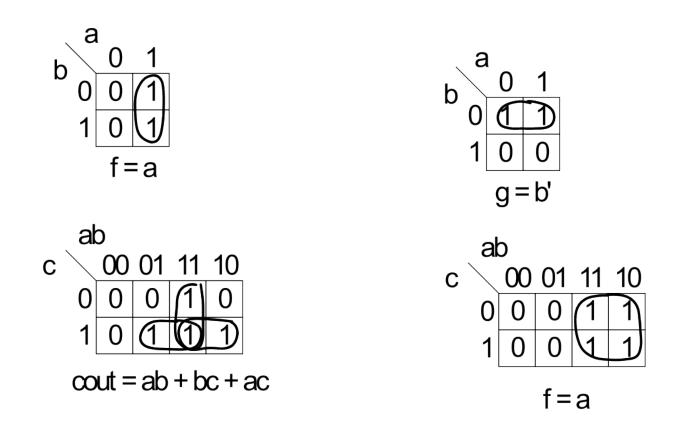

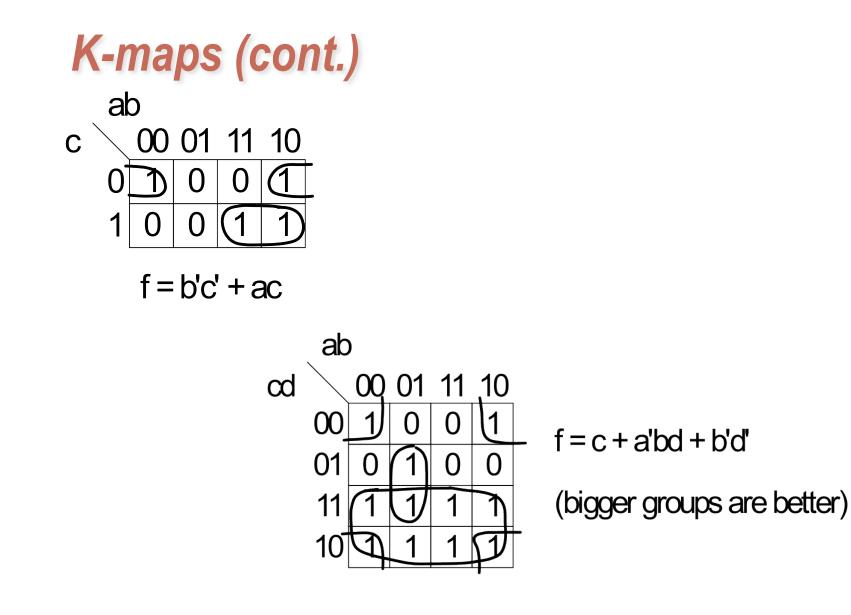

### Karnaugh Map Method

K-map is an alternative method of representing the TT and to help visual the adjacencies.

# Karnaugh Map Method

Adjacent groups of 1's represent product terms

### K-map Simplification

- 1. Draw K-map of the appropriate number of variables (between 2 and 6)

- 2. Fill in map with function values from truth table.

- 3. Form groups of 1's.

- ✓ Dimensions of groups must be even powers of two (1x1, 1x2, 1x4, ..., 2x2, 2x4, ...)

- ✓ Form as large as possible groups and as few groups as possible.

- ✓ Groups can overlap (this helps make larger groups)

- ✓ Remember K-map is periodical in all dimensions (groups can cross over edges of map and continue on other side)

- 4. For each group write a product term.

- the term includes the "constant" variables (use the uncomplemented variable for a constant 1 and complemented variable for constant 0)

- 5. Form Boolean expression as sum-of-products.

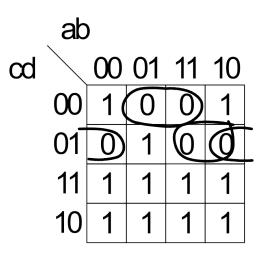

#### **Product-of-Sums Version**

- 1. Form groups of 0's instead of 1's.

- 2. For each group write a sum term.

- the term includes the "constant" variables (use the uncomplemented variable for a constant 0 and complemented variable for constant 1)

- 3. Form Boolean expression as product-of-sums.

f = (b' + c + d)(a' + c + d')(b + c + d')

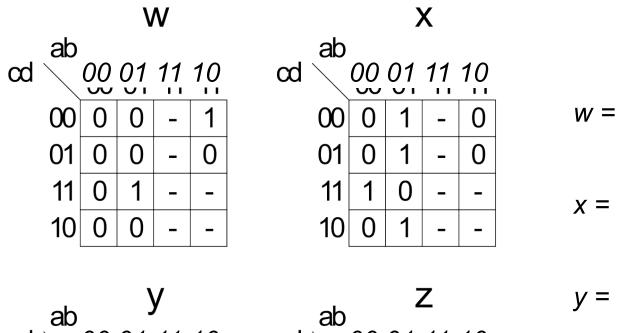

### **BCD** incrementer example

#### **Binary Coded Decimal**

| 1111 | 1 1 0 0 | 1011 |  | 9 1001 0000 | 8 1000 1001 | 7 0111 1000 | <u>6</u> 0110 0111 | 0101 0110 | 4 0100 0101 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 2 0010 0011 | 1 0001 0010 | 0 0000 0001 | abcd wxyz |

|------|---------|------|--|-------------|-------------|-------------|--------------------|-----------|-------------|------------------------------------------------------|-------------|-------------|-------------|-----------|

|------|---------|------|--|-------------|-------------|-------------|--------------------|-----------|-------------|------------------------------------------------------|-------------|-------------|-------------|-----------|

{a,b,c,d} 4 +1 4 { w,x,y,z}

### **BCD** Incrementer Example

- □ Note one map for each output variable.

- Function includes "don't cares" (shown as "-" in the table).

- These correspond to places in the function where we don't care about its value, because we don't expect some particular input patterns.

- We are free to assign either 0 or 1 to each don't care in the function, as a means to increase group sizes.

- In general, you might choose to write product-ofsums or sum-of-products according to which one leads to a simpler expression.

# **BCD** incrementer example

00 01  $\infty$ 10 11  $\mathbf{v}\mathbf{v}$ νı . . 11 00 1 1 \_ 01 0 0 0 \_ 11 0 0 \_ -10 1 --

V =

Z =

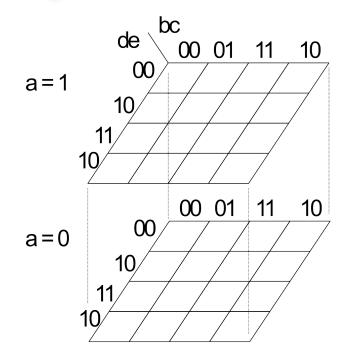

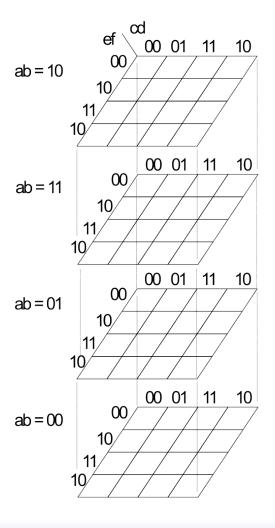

# **Higher Dimensional K-maps**

#### **Boolean Simplification** – Multi-level Logic

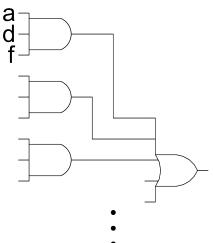

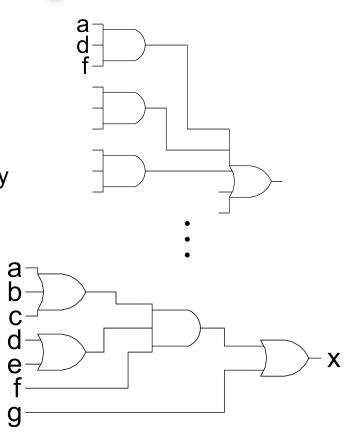

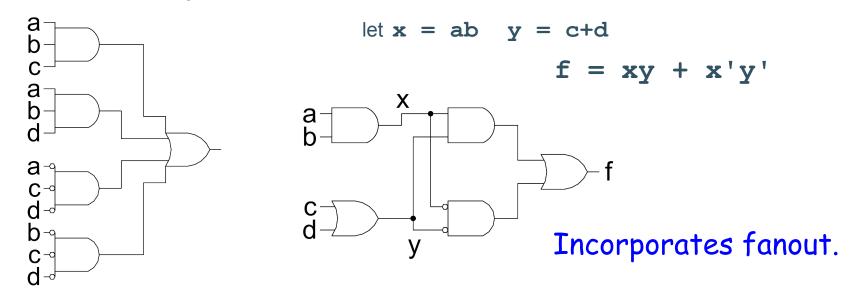

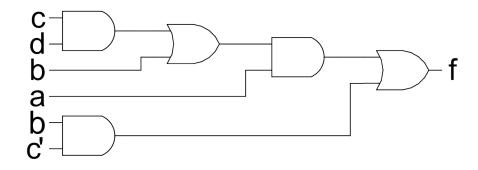

Example: reduced sum-of-products form

x = adf + aef + bdf + bef + cdf + cef + g

Implementation in 2-levels with gates:

<u>cost:</u> 1 7-input OR, 6 3-input AND

=> 50 transistors

<u>delay:</u> 3-input OR gate delay + 7-input AND gate delay

□ Factored form:

x = (a + b +c) (d + e) f + g cost: 1 3-input OR, 2 2-input OR, 1 3-input AND => 20 transistors delay: 3-input OR + 3-input AND + 2-input OR

Footnote: NAND would be used in place of all ANDs and ORs.

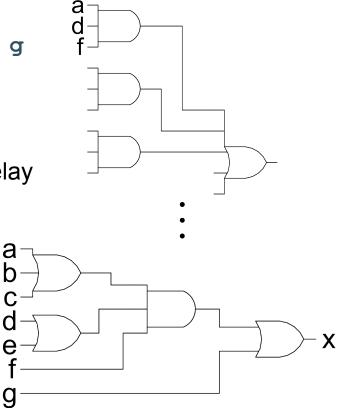

Example: reduced sum-of-products form

x = adf + aef + bdf + bef + cdf + cef + g

Implementation in 2-levels with gates:

<u>cost:</u> 1 7-input OR, 6 3-input AND

=> 50 transistors

<u>delay:</u> 3-input OR gate delay + 7-input AND gate delay

Factored form: x = (a + b +c) (d + e) f + g <u>cost:</u> 1 3-input OR, 2 2-input OR, 1 3-input AND => 20 transistors <u>delay:</u> 3-input OR + 3-input AND + 2-input OR

Footnote: NAND would be used in place of all ANDs and ORs.

#### Which is faster?

In general: Using multiple levels (more than 2) will reduce the cost. Sometimes also delay. Sometimes a tradeoff between cost and delay.

Another Example: F = abc + abd + a'c'd' + b'c'd'

No convenient hand methods exist for multi-level logic simplification:

a) CAD Tools use sophisticated algorithms and heuristics

Guess what? These problems tend to be NP-complete

b) Humans and tools often exploit some special structure (example adder)

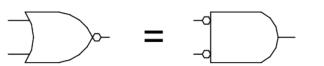

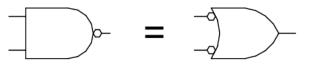

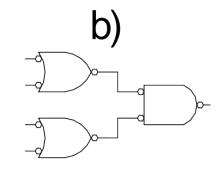

### NAND-NAND & NOR-NOR Networks

DeMorgan's Law Review: (a + b)' = a' b'

(a b)' = a' + b' (a b) = (a' + b')'

a + b = (a' b')'

push bubbles or introduce in pairs or remove pairs: (x')' = x.

# NAND-NAND & NOR-NOR Networks Mapping from AND/OR to NAND/NAND

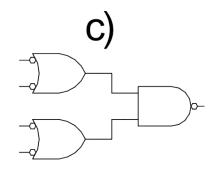

# **Multi-level Networks**

#### Convert to NANDs: F = a(b + cd) + bc'

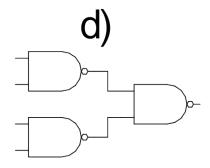

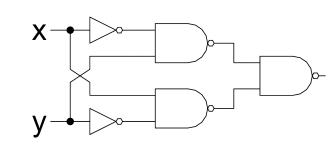

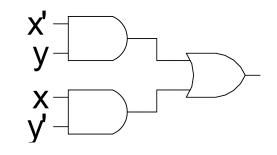

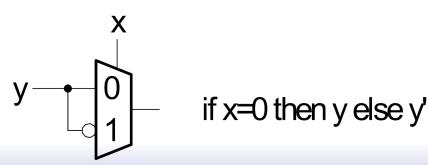

## **EXOR Function Implementations**

Parity, addition mod 2  $x \oplus y = x'y + xy'$

Another approach:

44