EECS151/251A Spring 2019 Digital Design and Integrated Circuits

Instructors: John Wawrzynek

Lecture 25

# Types of Faults in Digital Designs

- <u>Design Bugs</u> (function, timing, power draw)

- detected and corrected at design time through testing and verification (simulation, static checks)

- <u>Manufacturing Defects</u> (violation of design rules, impurities in processing, statistical variations)

- post production testing for sorting

- spare on-chip resources for repair

- <u>Runtime Failures (physical effects and environmental</u> conditions)

- assuming design is correct and no manufacturing defects

# **Dealing with Manufacturing Faults**

- Designers provide "test vectors"

ATPG (Automatic Test Pattern Generation)

- Completed ICs are tested and "binned" for correct operation, and speed grade.

Special circuits help speed the testing process

– BIST (built in self test), Scan-chains

Spring 2019

EECS150 - Lec25-faults

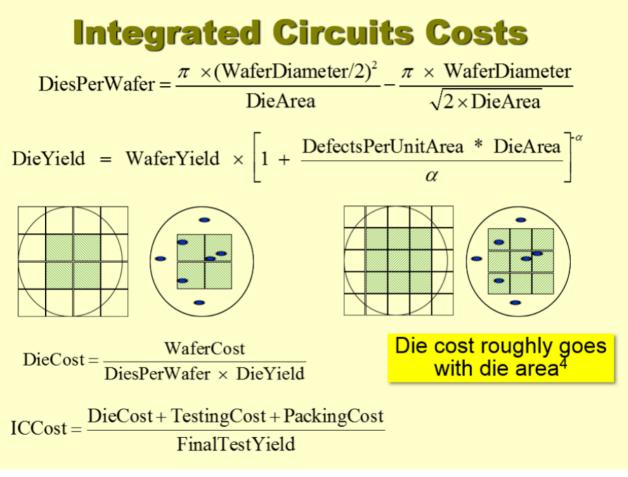

# Chip Yield and Costs

• Faulty chips are discarded which effectively raises the cost of good die.

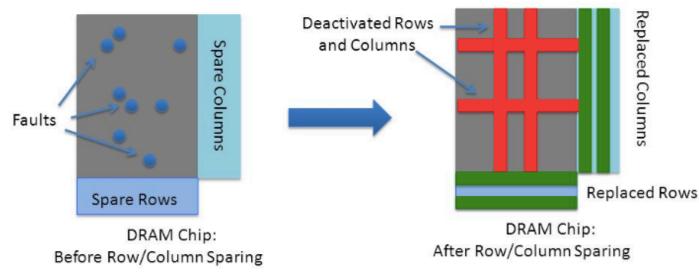

# "Sparing" Helps increase Yield

- Extra on-chip circuits wired in to replace faulty sections after manufacturing:

- DRAM, Flash, FPGAs, multi-core processors, mag disks

- DRAM chip (organized into rows and columns) have spares

- Laser fuses enable spare rows/columns

- Entire row/column needs to be sacrificed for a few faulty cells

## Runtime Faults

- All digital systems suffer occasional runtime faults.

- Fault tolerant design methodologies are employed to tolerate faults in critical applications (avionics, space exploration, medical, ...)

- Error detection and correction is commonly used in memory systems and communication networks.

- Deeply scaled CMOS devices will suffer <u>reliability</u> <u>problems</u> due to a variety of physical effects (processing, aging, environmental susceptibility)

- Lower supply voltage for energy efficiency makes matters worse.

# Physical Fault Mechanisms

- IC Faults can be classified as <u>permanent</u>, <u>transient</u>, and <u>intermittent</u>:

- Permanent faults reflect irreversible physical changes (*like fused* wire or shorted transistor)

- Transients are induced by temporary environmental conditions (*like* cosmic rays and electromagnetic interference)

- Intermittent faults occur due to unstable or marginal hardware (temporary  $\Delta V_t$  resulting in timing error)

- Intermittent faults often occurs repeatedly at the same location while transients affect random locations.

- Intermittent faults track changes in voltage and temperature, and may become permanent.

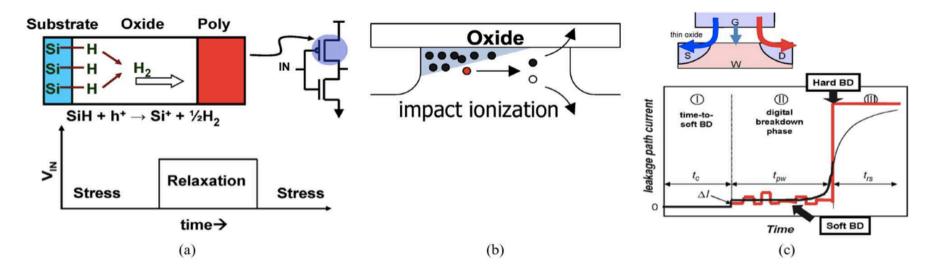

# Physical Fault Mechanisms

- Intermittent: Aging, Voltage/Temperature Dependent

- NBTI (negative bias temperature instability) & PBTI

- HCI (hot carrier injection)

- TDDB (time-dependent dielectric breakdown)

- Electromigration

**Fig. 5.** Temporal variations: (a) NBTI degradation process in PMOS. Breaking of hydrogen bonds creates dangling Si that acts as a defect trap near Si-SiO<sub>2</sub> interface—increasing  $V_{TH}$  of the transistor.  $V_{TH}$  degradation and recovery mechanism under NBTI stress is also shown. (b) Impact ionization due to HCI. (c) Percolation path due to TDDB. The behavior of leakage current after soft and hard breakdown is also plotted.

# Physical Fault Mechanisms

- NBTI, PBTI, & HCI increase Vt and decrease mobility

- Leads to decreased performance, lower noise margins, mismatching (in SRAM), ...

- TDDB causes soft or hard gate shorts resulting in degraded transistor performance and can lead to complete transistor failure

- Electromigration reduces interconnect conductivity and can lead to open circuit.

[Ghosh and Roy: Parameter Variation Tolerance and Error Resiliency: New Design Paradigm for the Nanoscale Era, Proceedings of the IEEE | Vol. 98, No. 10, October 2010 ]

### **Transient Fault Mechanisms**

### Single Event Effects on digital integrated circuits: Origins and Mitigation Techniques

Dr. Raoul Velazco TIMA Laboratory ARIS (Reliable Architectures of Integrated Systems) Grenoble – France http://tima.imag.fr raoul.velazco@imag.fr

Ecole de Microélectronique et Microsystèmes Fréjus, 19/5/2011

### 2. A Description of SEE's

### <u>What you always wanted to know about</u> <u>Single Event Effects (SEE's)</u>

- What are they?: One of the result of the interaction between the radiation and the electronic devices

- How do they act?:

Creating free charge in the silicon bulk that, in practical, behaves as a short-life but intense current pulse

Which are the ultimate consequences?

From simple bitflips or noise-like signals until the physical destruction of the device

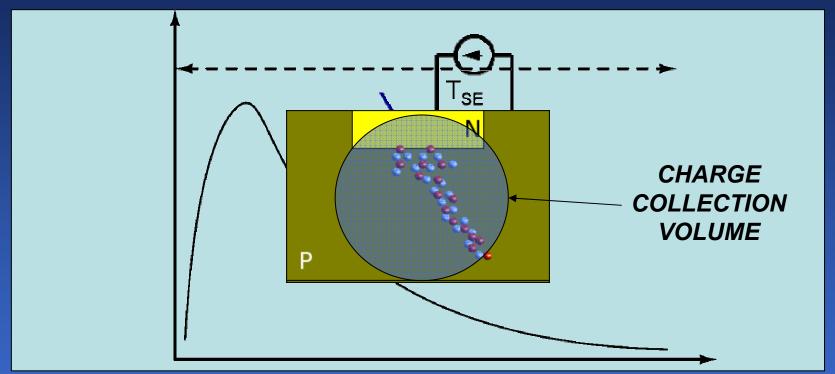

#### **The Physical Mechanism**

The incident particle generates a dense track of electron hole pairs and this ionization cause a transient current pulse if the strike occurs near a sensitive volume.

#### The Classification of SEE's

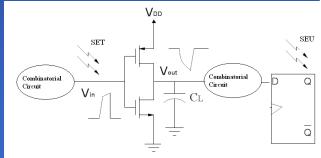

SINGLE EVENT UPSET (SEU): CHANGE OF DATA OF MEMORY CELLS MULTIPLE BIT UPSET (MBU): SEVERAL SIMULTANEOUS SEU'S SINGLE EVENT TRANSIENT (SET): PEAKS IN COMBINATIONAL IC's FUNCTIONAL INTERRUPTION (SEFI): PHENOMENA IN CRITICAL PARTS

SINGLE EVENT LATCH-UP (SEL): PARASITIC THYRISTOR TRIGGER

AND OTHERS...

#### HARD ERRORS vs SOFT ERRORS

### **3. Sources of SEE's**

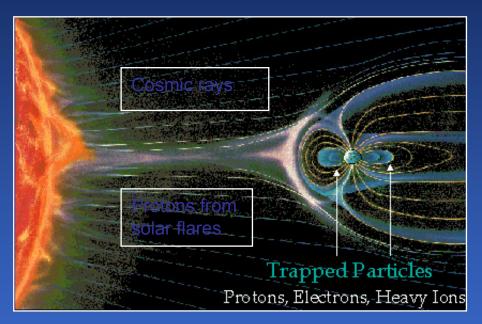

Usually, SEE's have been associated with space missions because of the absence of the atmospheric shield...

Unfortunately, our quiet oasis seems to be vanishing since the enemy is knocking on the door...

Alpha particle from vestigial U or Th traces

Atmospheric neutrons and other cosmic rays

- Sometimes, they appeared without a warning and, after some months and spending a lot of money, the source is detected\*.

- In 1978, Intel had to stop a factory because water was extracted from a nearby river that, upstream, is too close to an old uranium mine.

\* J. F. Ziegler and H. Puchner, "SER – History, Trends and Challenges. A guide for Designing with Memory ICs", Cypress Semiconductor, USA, 2004.

- Sometimes, they appeared without a warning and, after some months and spending a lot of money, the source is detected\*.

- In 1986, IBM detected a high rate of useless devices and related it to the phosphoric acid, the bottles of which were cleaned with a <sup>210</sup>P deionizer gadget...hundreds of kms far.

\* J. F. Ziegler and H. Puchner, "SER – History, Trends and Challenges. A guide for Designing with Memory IOs", Cypress Semiconductor, USA, 2004.

- Sometimes, they appeared without a warning and, after some months and spending a lot of money, the source is detected\*.

- In 1992, the problem came from the use of bat droppings living in cavern with traces of Th and U to obtain phosphorus.

\* J. F. Ziegler and H. Puchner, "SER – History, Trends and Challenges. A guide for Designing with Memory ICs", Cypress Semiconductor, USA, 2004.

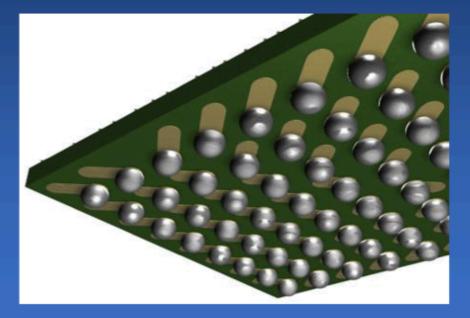

- But sometimes, we are a little naive...

- Solder balls are usually made from Sn and Pb, which come from minerals where there may be uranium and thorium traces.

Nevertheless, the designer forgets this detail and places the solder balls too close to critical nodes!

#### Cosmic Rays

Usually, they had been a headache for the designers of electronics boarded in space missions...

Here you are some of their practical jokes\*...

- <u>Cassini Mission</u> (1997).- Some information was lost because of MBUs.

- <u>Deep Space 1</u>.- An SEU caused a solar panel to stop opening out.

• <u>Mars Odyssey</u> (2001).- Two weeks after the launch, alarms went off because some errors lately attributed to an SEU.

• <u>GPS satellite network</u>.- One of the satellites is out of work, probably because of a latch-up.

### **3. Sources of SEE's**

### Cosmic Rays at Ground Level

- The highest fluence is reached between 15-20 km of altitude.

- Less than 1% of this particle rain reaches the sea level.

- The composition has also changed...

- Basically, neutrons and some pions

# Usually, the neutron flux is referenced to that of New York City, its value been of (in appearance) only 15 n/cm<sup>2</sup>/h

- This value depends on the altitude (approximately, x10 each 3 km until saturation at 15-20 km).

- And also on latitude, since the nearer the Poles, the higher rate.

- South America Anomaly (SAA), close to Argentina

- 1.5 m of concrete reduces the flux to a half.

What a weak foe, really should be we afraid of?

#### **Cosmics Rays at Ground Level**

Perhaps, we may believe that we are in a safe shelter but...

1992.- The PERFORM system, used by airplanes to manage the taking-off manoeuvre had to be suddenly replaced because of the SEUs in their SRAMs\*.

1998.- A study reported that, every day, the 1 out of 10000 SRAMs attached to pacemakers underwent bitflips\*\*.

This factor being 300 times higher if the patient had taken an transoceanic aircraft.

\* J. Olsen, IEEE Trans. Nucl. Sci., 1993, 40, 74-77 \*\* P. D. Bradley, IEEE Trans. Nucl. Sci., 45 (6), 2829-2940

#### Cosmic Rays at Ground Level

- The call of the Thousand (2000).- Sun Unix server systems crashed in dozens of places all over the USA because of SEU's happening in their cache memory, costing several millions of dollars\*.

- 2005.- After 102 days, the ASC Q Cluster supercomputer showed 7170 errors in its 81-Gb cache memory, 243 of which led to a crash of the programs or the operating system\*\*.

\* FORBES, 2000

\*\* K. W. Harris, IEEE Trans. Dev. Mat. Reliab., 2005, 5, 336-342

## 4. Mitigation of SEE's

#### First of all, Where must we expect SEEs?

- All the combinational stages are supposed to be affected by SETs.

- Everything having SRAM cells is a candidate to show SEUs, MBU's:

- SRAM's, Microprocessors, FPGAs, ASICs, etc.

- Other devices seem to be quite SEE-tolerant because of their way of building:

- DRAMs, PSRAMs, NAND memories, etc.

#### Which are the strategies to mitigate SEE's?

- 1. Technological

- 2. Design

3. Software and Hardware Redundancy

# Fault Models

- Low-level Fault Models:

- For logic circuit nodes

- 1. Permanent stuck at 0 or 1

- 2. Glitches

- 3. Slow transitions

- For memory blocks

(and flip-flops, registers)

- 1. Permanent stuck at 0 or 1

- 2. Hold failure

- 3. Read upset

- 4. Slow read

- 5. Write failure

$\Rightarrow$

=>

OR

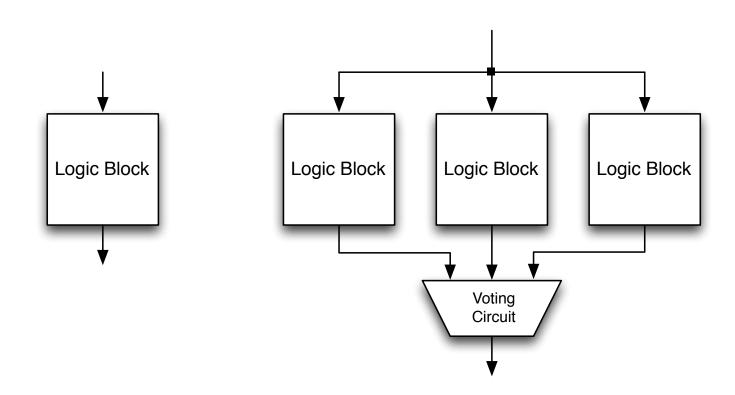

# A Fault-Tolerant Design Methodology

- Triple-Modular Redundancy

- relies on small / reliable voting circuit

- Most popular in space applications

### Error Correction Codes (ECC)

- Memory systems exhibit errors (accidentally flipped-bits)

- Large concentration of sensitive nodes

- "Soft" errors occur occasionally when cells are struck by alpha particles or other environmental upsets.

- Less frequently, "hard" errors can occur when chips permanently fail.

- Where "perfect" memory is required

- servers, spacecraft/military computers, ...

- Memories are protected against failures with ECCs

- Extra bits are added to each data-word

- extra bits are used to detect and/or correct faults in the memory system

- in general, each possible data word value is mapped to a unique "code word". A fault changes a valid code word to an invalid one which can be detected.

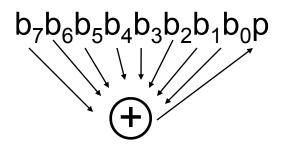

### Simple Error Detection Coding Parity Bit

Each data value, before it is written to memory is "tagged" with an extra bit to force the stored word to have even parity:

Each word, as it is read from memory is "checked" by finding its parity (including the parity bit).

- A non-zero parity indicates an error occurred:

- two errors (on different bits) is not detected (nor any even number of errors)

- odd numbers of errors are detected.

### Hamming Error Correcting Code

- Use more parity bits to pinpoint bit(s) in error, so they can be corrected.

- Example: Single error correction (SEC) on 4-bit data

- use 3 parity bits, with 4-data bits results in 7-bit code word

- 3 parity bits sufficient to identify any one of 7 code word bits

- overlap the assignment of parity bits so that a single error in the 7-bit word can be corrected

- **Procedure**: group parity bits so they correspond to subsets of the 7 bits:

- p<sub>1</sub> protects bits 1,3,5,7

- p<sub>2</sub> protects bits 2,3,6,7

- p<sub>3</sub> protects bits 4,5,6,7

1 2 3 4 5  $p_1 p_2 d_1 p_3 d_2 d_3 d_4$ Note: Bit position number number bits  $001 = 1_{10}$ from left to right.  $011 = 3_{10}$  $p_1$  $101 = 5_{10}$  $111 = 7_{10}$  $010 = 2_{10}$  $011 = 3_{10}$  $p_2$  $110 = 6_{10}$  $111 = 7_{10}$  $100 = 4_{10}$  $101 = 5_{10}$ · p<sub>3</sub>  $110 = 6_{10}$  $111 = 7_{10}$

Spring 2019

EECS150 – Lec25-fault

### Hamming Code Example

- 1 2 3 4 5 6 7

- $p_1 p_2 d_1 p_3 d_2 d_3 d_4$

- Note: parity bits occupy power-oftwo bit positions in code-word.

- On writing to memory:

- parity bits are assigned to force even parity over their respective groups.

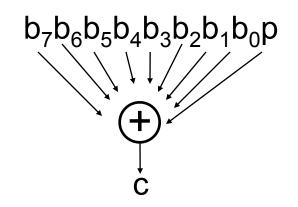

- On reading from memory:

- check bits (c<sub>3</sub>,c<sub>2</sub>,c<sub>1</sub>) are generated by finding the parity of the group and its parity bit. If an error occurred in a group, the corresponding check bit will be 1, if no error the check bit will be 0.

- check bits  $(c_3, c_2, c_1)$  form the position of the bit in error.

- Example:  $c = c_3 c_2 c_1 = 101$

- error in 4,5,6, or 7 (by  $c_3=1$ )

- error in 1,3,5, or 7 (by  $c_1=1$ )

- no error in 2, 3, 6, or 7 (by  $c_2=0$ )

- Therefore error must be in bit 5.

- Note the check bits point to 5

- By our clever positioning and assignment of parity bits, the check bits always address the position of the error!

- c=000 indicates no error

### Hamming Error Correcting Code

- Overhead involved in single error correction code:

- let p be the total number of parity bits and d the number of data bits in a p + d bit word.

- If p error correction bits are to point to the error bit (*p* + *d* cases) plus indicate that no error exists (1 case), we need:

$2^p >= p + d + 1$ ,

thus  $p \ge \log(p + d + 1)$

for large d, p approaches log(d)

Adding on extra parity bit covering the entire word can provide double error detection

| 1              | 2                     | 3     | 4              | 5     | 6     | 7     | 8                     |

|----------------|-----------------------|-------|----------------|-------|-------|-------|-----------------------|

| p <sub>1</sub> | <b>p</b> <sub>2</sub> | $d_1$ | p <sub>3</sub> | $d_2$ | $d_3$ | $d_4$ | <b>p</b> <sub>4</sub> |

On reading the C bits are computed (as usual) plus the parity over the entire word, P:

C=0 P=0, no error

C!=0 P=1, correctable single error

C!=0 P=0, a double error occurred

C=0 P=1, an error occurred in  $p_4$  bit

Typical modern codes in DRAM memory systems: 64-bit data blocks (8 bytes) with 72-bit code words (9 bytes), results in SEC, DED. Spring 2019 EECS150 – Lec25-fault

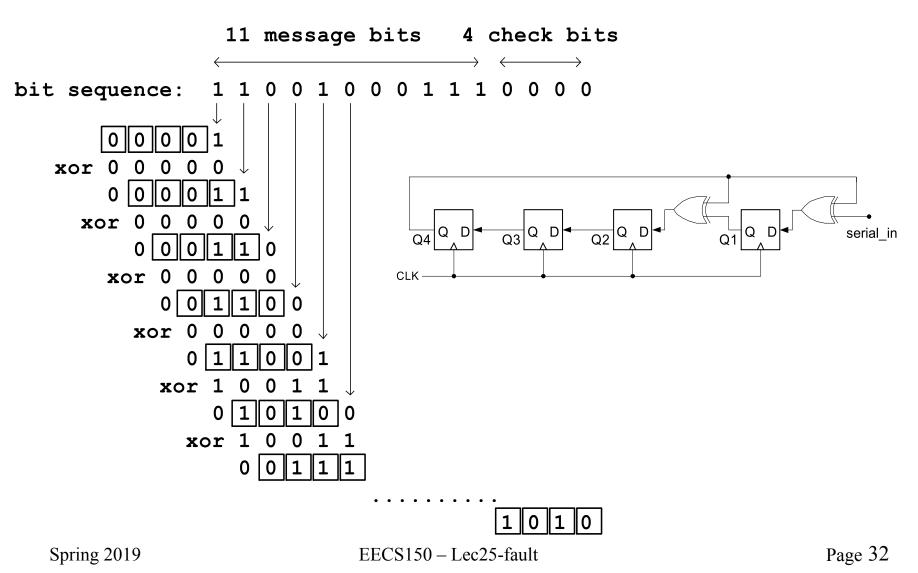

### Error Correction with LFSRs - Cyclic Redundancy Code (CRC)

### Error Correction with LFSRs (CRC)

- XOR Q4 with incoming bit sequence. Now values of shift-register don't follow a fixed pattern. Dependent on input sequence.

- Look at the value of the register after 15 cycles: "1010"

- Note the length of the input sequence is 2<sup>4</sup>-1 = 15 (same as the number of different nonzero patters for the original LFSR)

- Binary message occupies only 11 bits, the remaining 4 bits are "0000".

- They would be replaced by the final result of our LFSR: "1010"

- If we run the sequence back through the LFSR with the replaced bits, we would get "0000" for the final result.

- 4 parity bits "neutralize" the sequence with respect to the LFSR.

$11001000111 0000 \Rightarrow 1010$

$1100100011111010 \Rightarrow 0000$

- If parity bits not all zero, an error occurred in transmission.

- If number of parity bits = log total number of bits, then single bit errors can be corrected.

- Using more parity bits allows more errors to be detected.

- Ethernet uses 32 parity bits per frame (packet) with 16-bit LFSR.