## **Homework #5 Solutions**

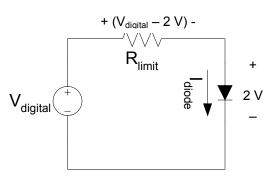

## Problem 1:

For there to be between 20 mA and 100 mA of current flowing, the diode must be forward biased. The diode will take 2 V of  $V_{digital}$ , and the resistor will take the rest of  $V_{digital}$ .

The current flowing through the circuit will thus be

$I_{diode} = (V_{digital} - 2 V)/R_{limit}$

$R_{\text{limit}}$  must be small enough so that  $I_{\text{diode}}$  is at least 20 mA when  $V_{\text{digital}}$  is at its smallest, 4 V.

$(4 V - 2 V)/R_{\text{limit}} \ge 20 \text{ mA}$   $R_{\text{limit}} \le 100 \Omega$

$R_{limit}$  must be big enough so that  $I_{diode}$  is less than 100 mA when  $V_{digital}$  is at its biggest, 5 V.

$(5 \text{ V} - 2 \text{ V})/\text{R}_{\text{limit}} \le 100 \text{ mA}$   $\text{R}_{\text{limit}} \ge 30 \Omega$

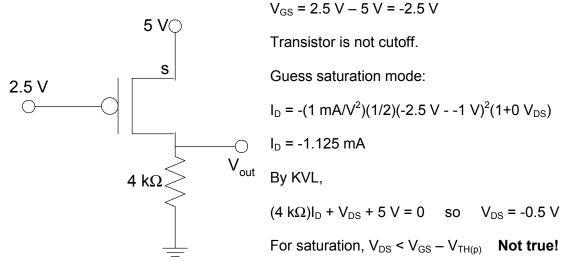

Problem 2:

So transistor must be in triode mode.

$I_D = -(1 \text{ mA/V}^2)(-2.5 \text{ V} - -1 \text{ V} - (V_{DS}/2))(V_{DS})$

It's still true that  $(4 \text{ k}\Omega)I_D + V_{DS} + 5 \text{ V} = 0$  so substitute to get

$$-(5 \text{ V} + \text{V}_{\text{DS}})/4 \text{ k}\Omega = -(1 \text{ mA/V}^2)(-2.5 \text{ V} - -1 \text{ V} - (\text{V}_{\text{DS}}/2))(\text{V}_{\text{DS}})$$

Solutions:  $V_{DS} = \{-1 V, -2.5 V\}$

$V_{DS}$  = -2.5 V not possible for triode mode (need  $V_{DS} > V_{GS} - V_{TH(p)}$ ) so  $V_{DS}$  = -1 V

$$I_D = -(1 \text{ mA/V}^2)(-2.5 \text{ V} - -1 \text{ V} - (-1 \text{ V/2}))(-1 \text{ V}) = -1 \text{ mA}$$

$V_{out} = V_{DS} + 5 V = 4 V$

(Typically, the numbers do not work out this nicely!)

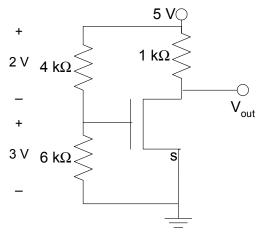

## Problem 3:

Notice that no current goes into or out of the gate. So the 4 k and 6 k transistors have the same current.

Voltage division or Ohm's law tells us that the 4 k resistor has 2 V and the 6 k resistor has 3 V as shown.

So  $V_{GS}$  = 3 V (over the 6 k resistor).

The transistor is not cutoff.

Guess saturation mode:

$I_D = (1 \text{ mA/V}^2)(1/2)(3 \text{ V} -1 \text{ V})^2(1+0 \text{ V}_{DS})$   $I_D = 2 \text{ mA}$

By KVL,  $(1 \text{ k}\Omega)I_D + V_{DS} - 5 \text{ V} = 0$  so  $V_{DS} = 3 \text{ V}$

For saturation,  $V_{DS} > V_{GS} - V_{TH(n)}$  Yes! Saturation was the right guess.  $V_{out} = V_{DS} = 3 V$

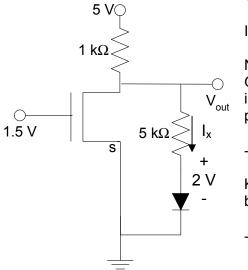

Problem 4:

V<sub>GS</sub> = 1.5 V Transistor is not cutoff. Guess saturation:

$I_D = (1 \text{ mA/V}^2)(1/2)(1.5 \text{ V} -1 \text{ V})^2(1+0 \text{ V}_{DS})$   $I_D = 125 \,\mu\text{A}$

Now we must find  $V_{DS}$ . The only way to do this is by KVL. Guess that the diode is forward biased (small Vin means big Vout for our inverter). For large-signal model, this means diode has  $V_F$  = 2 V and some positive current. Now starting KVL at ground and going clockwise,

$-V_{DS} + 5 k\Omega I_x + 2 V = 0$  Need to find  $I_x$ .

KVL again, starting at ground, going up diode branch and 1k resistor branch, dropping back to ground over 5 V source:

- 2 V - 5 kW

$$I_x$$

– 1 k $\Omega$  ( $I_x$  + 125  $\mu$ A) + 5 V = 0

$V_{DS} = 5 k\Omega I_x + 2 V$  (by previous KVL)  $V_{DS} = 4.395 V$

For saturation,  $V_{DS} > V_{GS} - V_{TH(n)}$  Yes! Saturation was the right guess.  $V_{out} = V_{DS} = 4.395 V$