# Lecture 26

Last time: NMOS Transistor (NMOS = n-channel Metal Oxide Semiconductor Transistor) NMOS I-V Characteristics and empirical model (equations)

Today:

•NMOS Switch Model

•PMOS transistor and Switch Model

•CMOS!

# **NMOS** Review

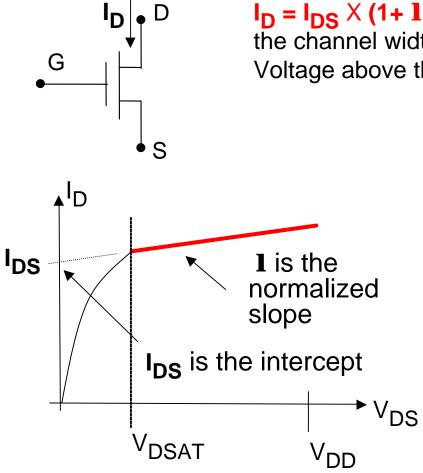

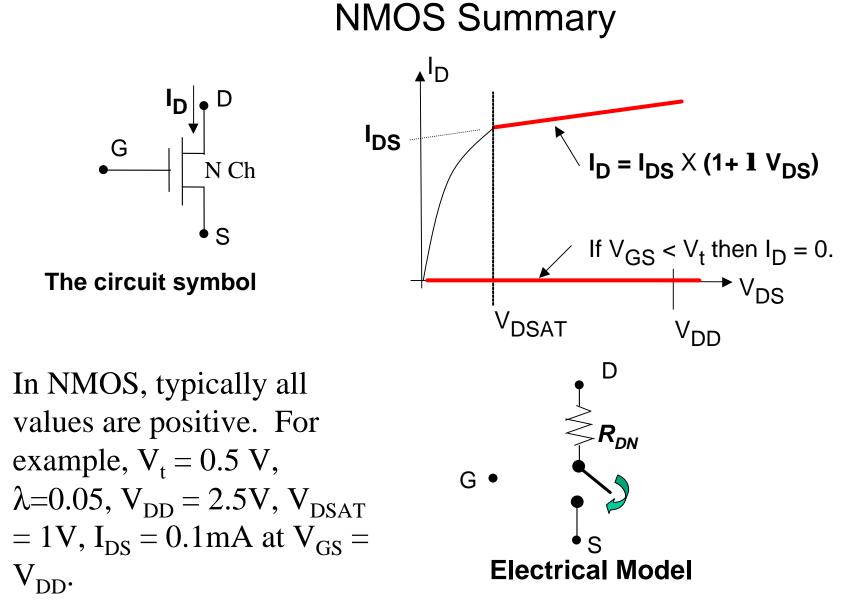

#### The variation of $I_D$ with $V_{DS}$ in the saturation region is given by:

$I_D = I_{DS} \times (1 + 1 V_{DS})$  in which  $I_{DS}$  is proportional to the channel width W and depends on the Gate Voltage above threshold. If  $V_{GS} < V_t$  then  $I_D = 0$ .

Thus for our hand calculations we need only to have the following MOS properties specified:

1) Saturation Current IDS

2) The slope 1. This is the fractional increase of current for one volt increase in  $\rm V_{\rm DS}.$

3) We may not need to know  $V_{DSAT}$  because we will be typically interested in the current in the range  $V_{DS} > V_{DD}$  /2.

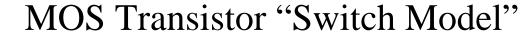

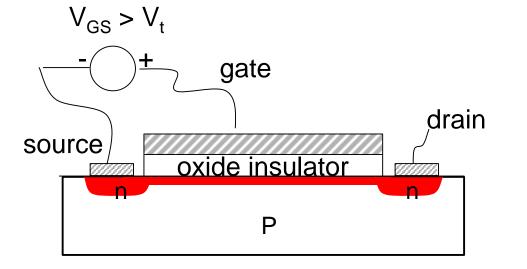

**Physical NMOS Device**

- No current flows through the gate terminal of a MOS Device

- But the Gate voltage controls the resistance from drain to source

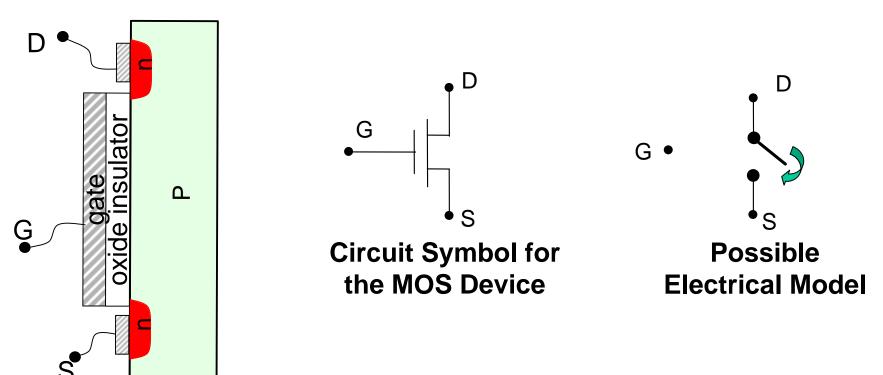

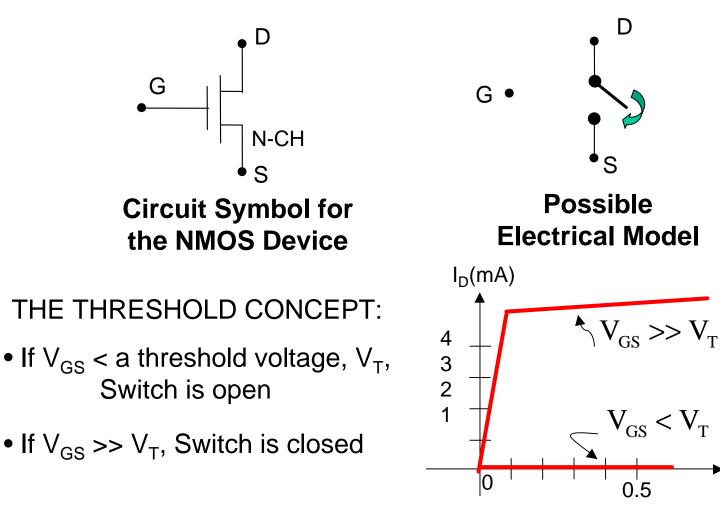

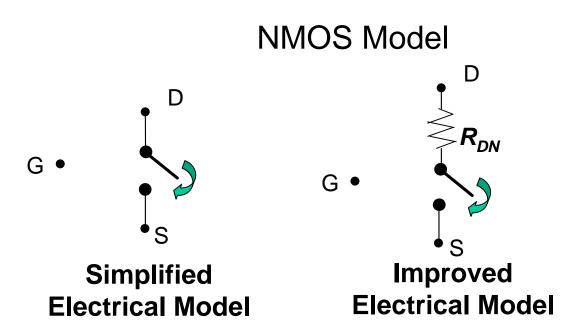

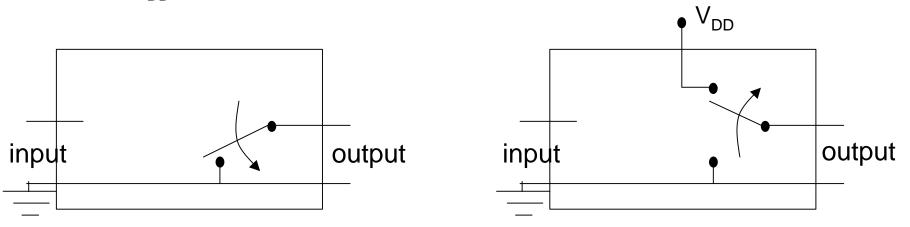

## NMOS Transistor "Switch Model"

But  $I_D$  vs  $V_{DS}$  is too complex to be represented by open/short

4

#### NMOS Model Refinement **Closed NMOS transistor is not a perfect conductor** $\rightarrow$ add an equivalent resistor $R_{DN}$ that reflects this phenomenon Note: $R_{DN}$ is NOT the simple source drain resistance near the origin. I<sub>D</sub>(mA) D **R**<sub>DN</sub> $V_{\rm GS} >> V_{\rm T}$ 4 G 3 G 2 Possible Improved ►V<sub>DS</sub> 0 **Electrical Model Electrical Model** 0.5

$R_{DN}$  depends on 1) Gate voltage , and 2) Device geometry Why? We will use  $V_{GS} = 0$  for open switch and  $V_{GS} = V_{DD}$  for closed switch. Thus there is only one "on" gate voltage.

$R_{DN}$  will be inversely proportional to the gate width W.

Note:  $R_{DN}$  is NOT the simple (low V<sub>DS</sub>) source drain resistance

- If  $V_{GS} = 0$  we have open switch (or  $R_{DN} = 8$ ).

- If  $V_{GS} = V_{DD}$  we have closed switch.  $R_{DN}$  is only an effective resistor value. We need to choose the value of  $R_{DN}$  that gives the correct answer for timing calculations.

- Before finding  $R_{DN}$  we need to consider the actual device structure. (next lecture)

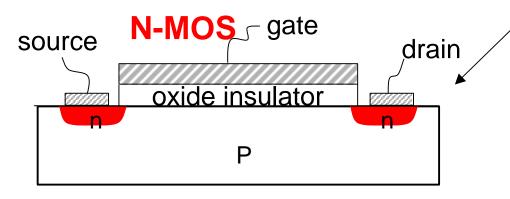

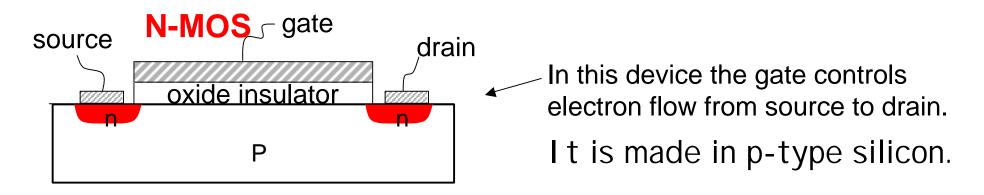

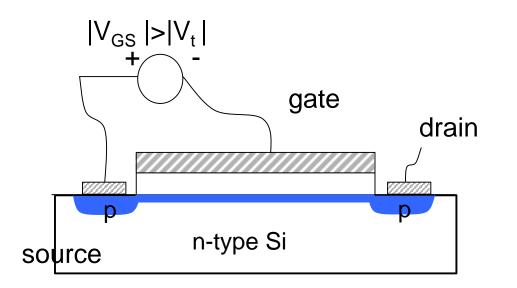

# NMOS =device which carrier current using electrons but on the surface of a p-type substrate

In this device the gate controls electron flow from source to drain.

(in the absence of gate voltage, current is blocked)

If we increase gate voltage to a value greater than V<sub>t</sub> then a conducting channel forms between source and drain. ("Closed switch")

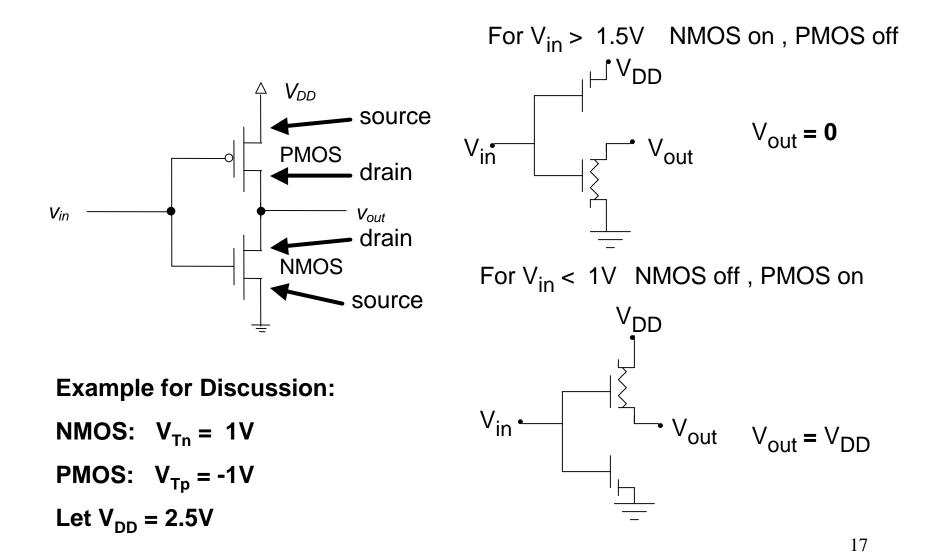

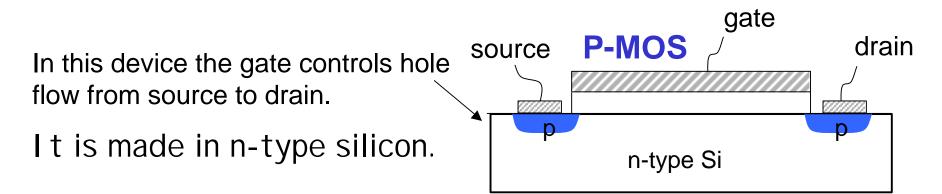

# CMOS = Complementary MOS (PMOS is a second Flavor)

The NEW FLAVOR! P-MOS

## PMOS

What if we apply a big negative voltage on the gate?

If  $|V_{GS}| > |V_t|$  (both negative)

then we induce a + charge on the surface (holes)

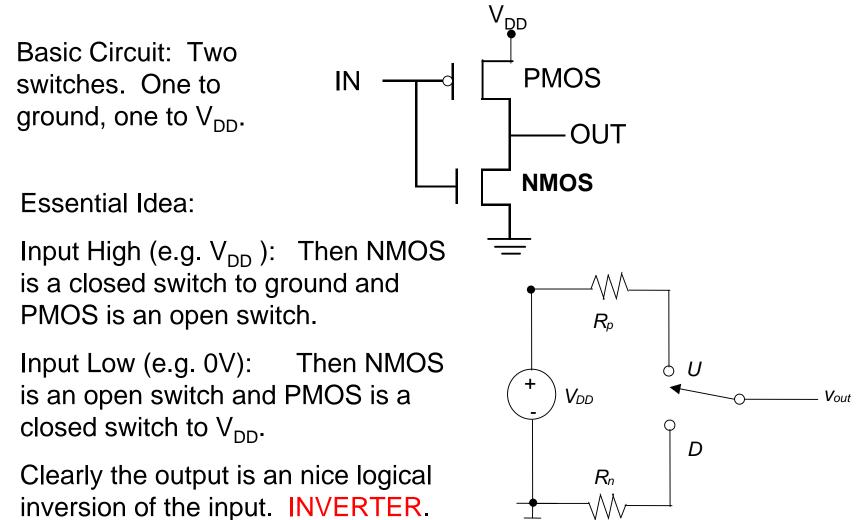

## Why do we want PMOS?

We already have the ideal switch to connect any node to ground.

An NMOS transistor with gate held high has a very low resistance and essentially switches a node to ground (logic low).

We also need a switch to switch nodes to whatever voltage is chosen as logic high (typically  $V_{DD}$ ).

• A PMOS transistor is just the ticket. It is precisely as ideal a switch for connections to high as NMOS transistors are for connections to low.

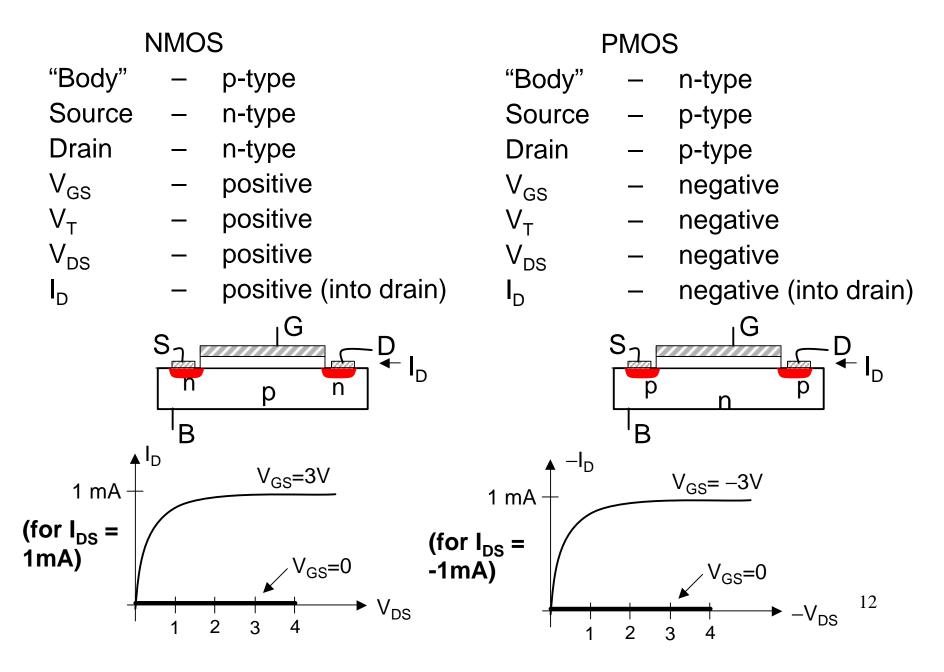

• What's cool is that there is little more to learn about PMOS. These devices are essentially the same as NMOS except *all signs on V and I are reversed.*

## NMOS and PMOS Compared

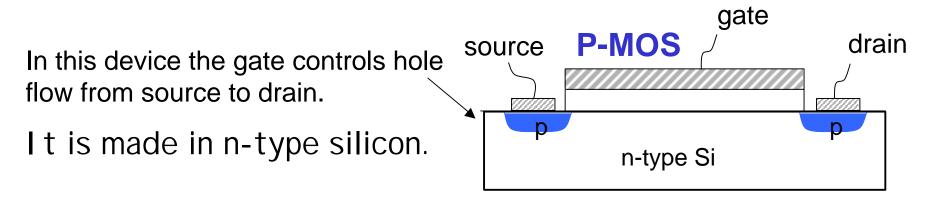

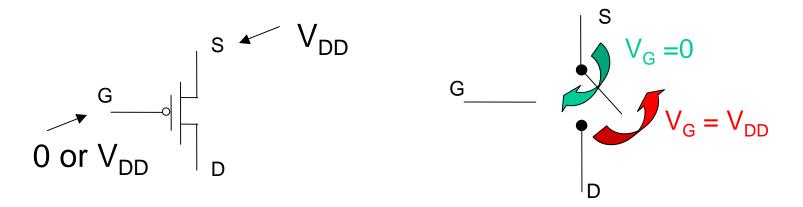

# PMOS Transistor Switch Model "Complementary" operation compared to NMOS

Switching thresholds for PMOS for "default" digital circuit connection Connect S to VDD (The function of the device is a "pull up")

Switch is *closed:* Drain (D) is shorted to Source (S) when  $V_G = 0$

Switch is open : Drain (D) is disconnected from Source (S) when  $V_G = V_{DD}$

# **PMOS Model Refinement**

### **PMOS** transistor has an equivalent resistance $R_{DP}$ when closed

The Switch model

15

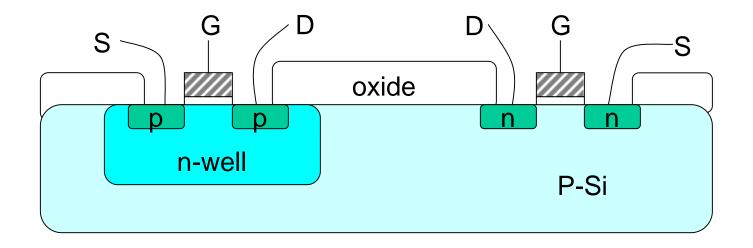

## CMOS

#### Challenge: build both NMOS and PMOS on a single silicon chip

#### NMOS needs a p-type substrate

#### PMOS needs an n-type substrate

**Requires extra process steps**

## THE BASIC STATIC CMOS INVERTER