EE40 Lecture 7 Josh Hug

7/7/2010

#### **Blackboard Stuff**

- HW3 concerns

- Any general questions people might have

#### **General Info**

- No lab today

- Midterm on Friday in class

- 12:10-1:30 [be on time!]

- No electronic devices

- One 8.5"x11" (or A4) sheet of paper

- Handwritten anything you want, both sides

- HW4 due next Friday (will be posted Friday)

- No positive feedback circuits on the midterm (but there might be on the final)

# Project 2

- Project 2 spec to be posted over the weekend

- If you'd like to do something other than the official project, you can submit a specification for your Project 2:

- Team members (up to 3)

- Parts list

- Schematic

- Must have substantial hardware component

- Microcontrollers are OK, but your project shouldn't be about assembly programming

- MyDAQ is also OK, but your project shouldn't be about LabVIEW programming

- Custom project proposals due WEDNESDAY by 5 PM

#### **Guest Mini-Lecture Today**

- Jeff Jansen from National Instruments will be talking today for the last half hour

- MyDAQ data acquisition device

- USB device that lets you use your computer in lieu of big bulky specialized test equipment

- Can use this device to do labs from home or anywhere else a laptop functions

- If anyone wants to use these in labs, we will have 10 of them available

- Could be handy for Project 2

- Must have substantial hardware component (can't just be LabVIEW software written for MyDAQ)

## **Course Website**

- I am assured that the rest of the calendar and the other 5 labs will be posted shortly. Most likely schedule is:

- -7/13: Project 1 (buzzer)

- 7/14: Sound synthesizer

- 7/20: Power supply

- 7/21: Active filter lab

- 7/27-8/11: Project 2

- Future reading assignments will be posted 3 days before they're due

- Micro-deadlines are needed for me, too!

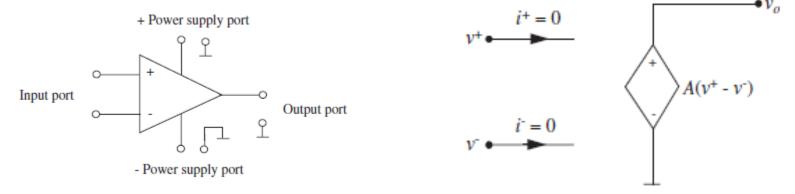

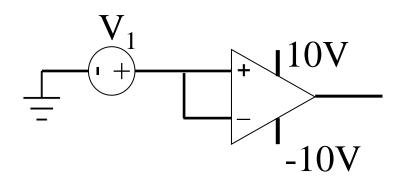

# **Op-Amp Saturation**

Remember those power ports we've been ignoring?

• They specify the maximum and minimum voltage that our op-amp can deliver

$$- \text{ If } v_{\min} < A(v^+ - v^-) < v_{max}$$

• Op-Amp output is  $A(v^+ - v^-)$

- $\text{ If } A > v_{max}, \qquad \text{ If } A < v_{min},$

- Op-Amp output is v<sub>max</sub>

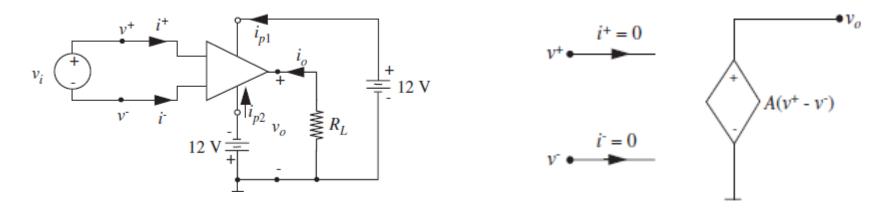

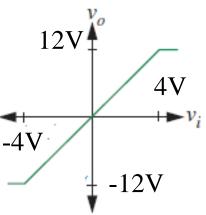

#### **Op-Amp Saturation Example**

•

$$v_{max} = 12V$$

,  $v_{min} = -12V$

• If A=3:  $V_{in}$   $V_{o}$ -5 V -12V -1V -3V 2V 6V 1,512,312V 12V

#### **Positive Feedback**

#### On the board

# **Another Op-Amp Model Revision**

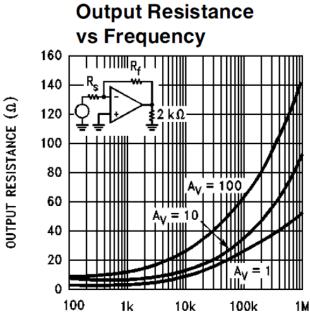

- Real amplifiers deviate from the ideal

Input resistance between V<sup>+</sup> and V<sup>-</sup>

- Output resistance at the output of the dependent source

- Another significant problem is "common mode signal amplification"

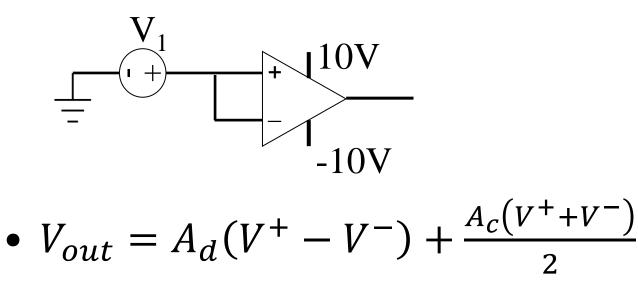

# **Common Mode Signal**

- In theory, the above amplifier would have an output voltage of 0V

- In practice, even an equal signal will leak through a little

•

$$V_{out} = A_d (V^+ - V^-) + \frac{A_c (V^+ + V^-)}{2}$$

New Term

# **Common Mode Signal**

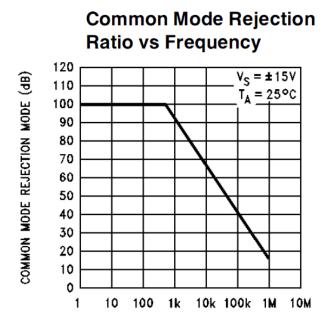

- A<sub>d</sub> and A<sub>c</sub> are typically not explicitly considered

- Instead, we consider the "Common Mode Rejection Ratio"  $CMRR = \frac{A_d}{A_c}$

- Big is good, less common mode signal

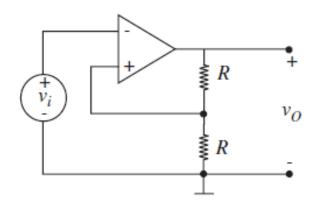

#### **Example of using CMRR**

• Find  $V_o$  as a function of  $R_s$ ,  $R_f$ , CMRR

• (On board)

# **One of many Op-Amp parameters**

- Typical CMRR is 35,000 (~90 dB)

- Usually measured in db

- CMRR<sub>db</sub>=20\*log<sub>10</sub>(CMRR)

- In real life, Op-Amps come with multipage data sheets (as do everything else)

FREQUENCY (Hz)

Hug

- How are you feeling about Node Voltage and solving basic circuits?

- A. Completely lost

- B. A little behind

- C. Alright

- D. Pretty good

- E. Feel like I've attained mastery

- How are you feeling about I-V characteristics and Thevenin and Norton equivalents?

- A. Completely lost

- B. A little behind

- C. Alright

- D. Pretty good

- E. Feel like I've attained mastery

- How are you feeling about Op-Amp circuits?

- A. Completely lost

- B. A little behind

- C. Alright

- D. Pretty good

- E. Feel like I've attained mastery

- How are you feeling about the midterm?

- A. Terrified

- B. A little scared

- C. Neutralish

- D. Feel prepared

- E. Feel like I will do excellently

#### Make up Labs

- Do you need a make up lab?

- A. Yes

- B. No

This is where we stopped

## Elements with Memory a.k.a. Energy Storage Elements

# **Preview of Unit 2**

- In the next major unit of the class, starting next Monday, we'll be discussing elements with memory

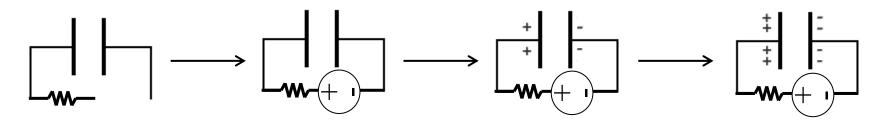

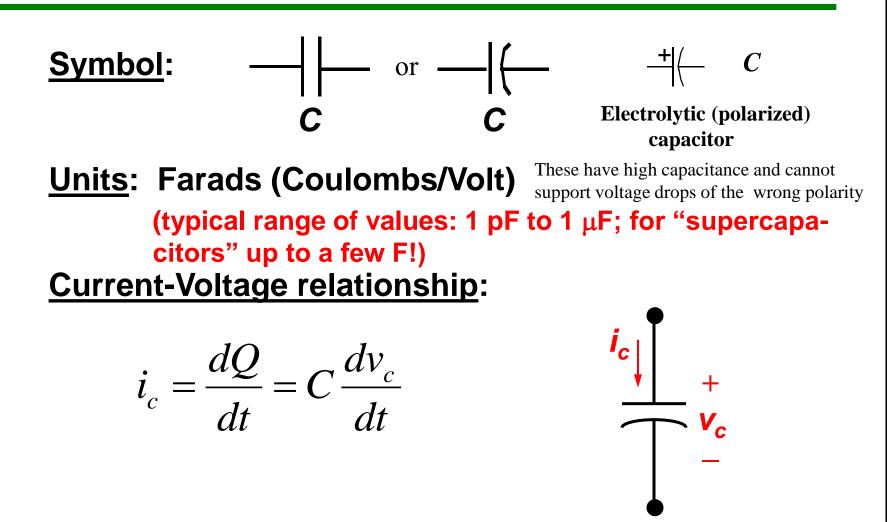

- Capacitor: Gives relationship between I and  $\frac{dv}{dt}$

- Inductor: Gives relationship between V and  $\frac{di}{dt}$

- Fundamental mathematical difference is that their *IV* relationship changes with time

- Fundamental physical difference is that they can store energy

- For the rest of today, we'll give a sneak preview of this material

#### **RC Circuits**

Taking the Live Demo risk, let's check out a quick qualitative circuit simulation

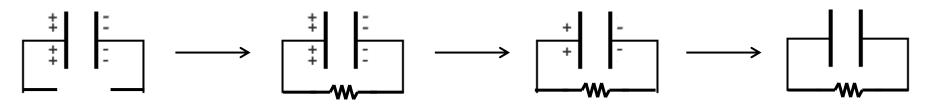

- The basic idea is pretty simple

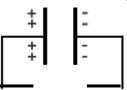

- Imagine you have two parallel metal plates, both of which have equal and opposite excess charges

- Plates are separated by an insulating layer (air, glass, wood, etc)

- The charges would love to balance out

- Insulator blocks them (just as the ground blocks you from falling into the center of the earth)

# **The Capacitor**

- If you were to connect a resistive wire to the plates

- Charges would flow through the wire

- Charge flow is current

- $P = I^2 R$

- Energy has been released as heat

Remember that a voltage is the electrical potential between two points in space

- Here, we have an imbalance of charge, and thus an electric field, and thus a voltage V = EL

- Field strength is dependent on number and distribution of charges as well as material properties

- Field length is dependent on size of capacitor

- Capacitor size and material properties lumped into single "capacitance" C

•

$$V = QC$$

# **The Capacitor**

- Thus, if you connect a voltage source to the plates

- Like charges will move to get away from the source

- Charge flow is current

- Current will stop once charges reach equilibrium with voltage source, i.e.  $V_c = V_s$

- Energy has been stored

#### **The Capacitor**

# Capacitor

<u>Note</u>:  $v_c$  must be a continuous function of time since the charge stored on each plate cannot change suddenly

#### **Node Voltage with Capacitors**

$i_c = \frac{dQ}{dt} = C \frac{dv_c}{dt}$

On board

# **Ordinary Differential Equations**

- Inductors, too, give us a simple 1<sup>st</sup> order relationship between voltage and current

- Node Voltage with memoryless circuits gave us algebraic equations

- Node voltage with elements with memory will give us Ordinary Differential Equations (ODEs)

- Next week will be a bunch of setting up and solving 1<sup>st</sup> and 2<sup>nd</sup> order linear ODEs

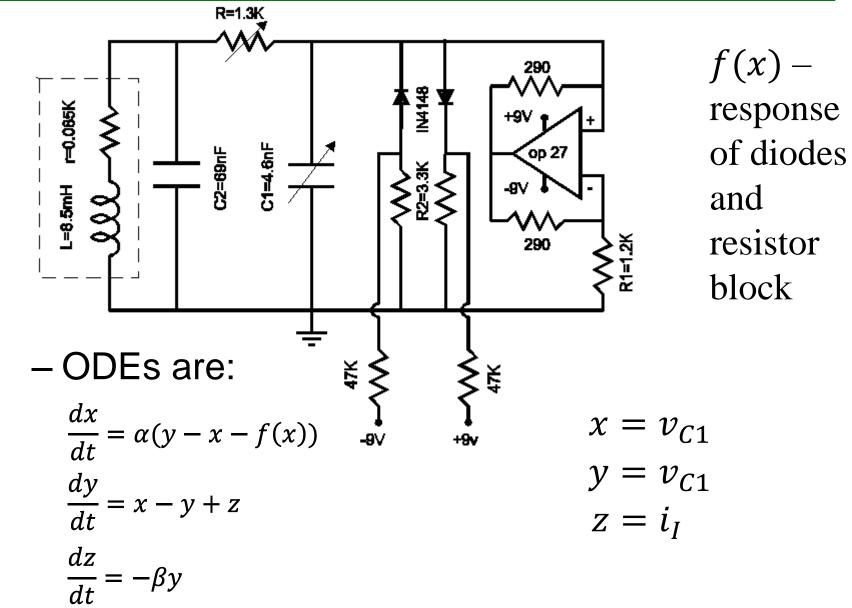

- Higher order and especially nonlinear ODEs are tough to solve. For example...

#### **Chua's Circuit**

EE40 Summer 2010

# **Chua's Circuit**

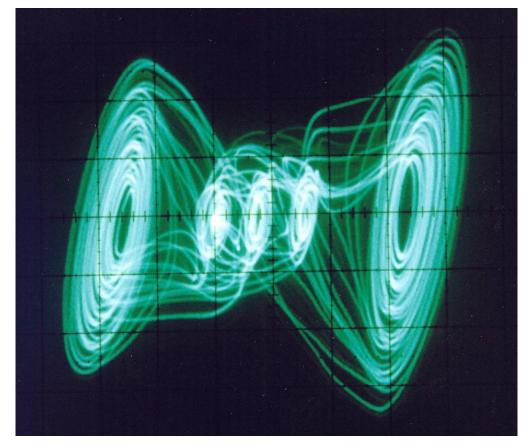

• Despite simplicity of ODEs

$$\frac{dx}{dt} = \alpha(y - x - f(x))$$

$$\frac{dy}{dt} = x - y + z$$

$$\frac{dz}{dt} = -\beta y$$

• Exhibits chaos!

Invented by current UC Berkeley EECS professor Leon Chua in 1983

#### **Capacitors**

- Useful for

- Storing Energy

- Filtering

- Modeling unwanted capacitive effects, particularly delay

#### **Good luck on your midterm!**

• Now on to Jeff's presentation