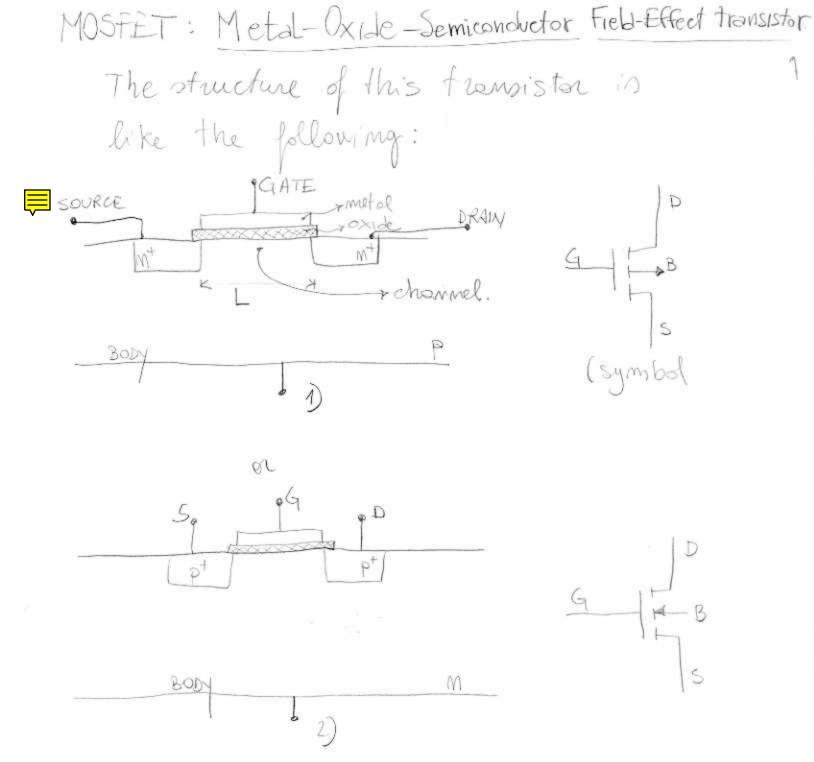

The device in 1) is called m-channel MOSFET and is built on a p substrate. The device in 2) is called p-channel MOSFET and is built on an m substrate. Usually source and body are commected together and this will be the configuration that we will consider.

MOS is of course referred to the transistor z structure while FET is referred to the way it works. We use the electric field effect generated by a voltage across gate and books (or gate and source when books and source are connected together) to allow current to flow betwee source and ohoin.

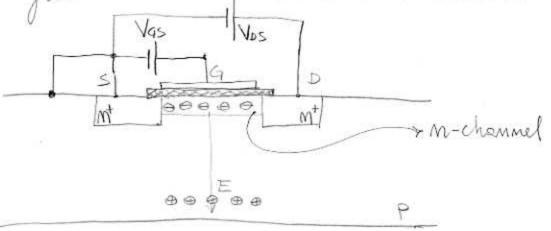

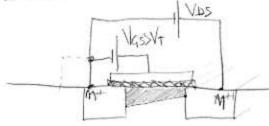

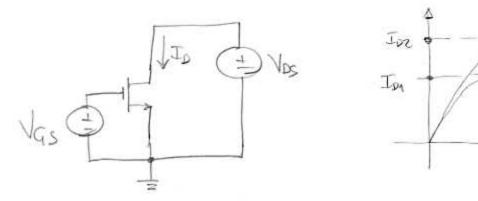

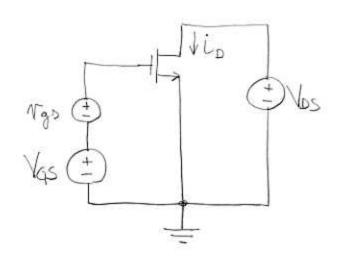

Consider an m-channel Mos where a voltage source is connected between gate and source and drain an source.

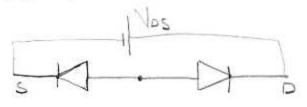

If Vas=0 then the electric field in the "copacitor" gate-body is zero and there is no effect on the changes that are present in the substrate. The device can be modeled as two diodes:

This circuit commot conduct current mo matter what is Vos becouse one of the two chiodes will always be OFF.

If Vas>0 then E +0 and it's directed from the gate to the body.

Positive changes then move down in the substrate and negative changes move up towards the channel. This is because a change is subject to a force f = gE.

Notice that in the p substrate there are much more positive charges (holes) than electrons but the electron density is not zero.

If E is too small, meaning that Vas is too small, the number of electrons in the channel, or equivalently the negative charge density, is very small. The density then would not be sufficient to allow a significant current between source and drain: cut off REGION.

For a certain value of Vas, the number of electrons in the channel becomes sufficient to allow conduction of current between sand D.

The value of Vas that allow conduction is called M+ Vas>Vr Nos ZVr threshold voltage and denoted by VT.

Consider the case where Vas>V+ (hence the channel is formed) and

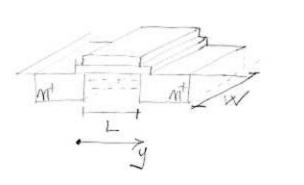

Vos small. If we establish a xiy coordinate system than the potential in the channel is a function of (x,y) and we shall demote it V(xy). We are interested in the y exes so we will consider only V(y). If Vos is very small, then we can consider My) almost constant otherwise V(y) will change with y and the situation will be like the following:

The reason is that

the total potential

difference across the channel in Vos so

the electric field changes depending on y and hence the change density changes.

for small Vos we can analyze the MOSFET as follows.

The current depends on the charge density and on their speed (because it is the number of charges in the unit time).

ID(4)=WQ(y) V(y)

This is the linear density of the ament at position y.

Qm(y) is the electrons density at a position y while v(y) is their velocity. Velocity of charges is proportional to the electric field:  $v(y) = -\mu_m E(y) = \mu_m \frac{\partial V(y)}{\partial y}$

So Is (9) = W Qm (y) µm 2V(y)/34

We can express  $Q_m(y)$  as a function of Voltage by following a simple reasoning. The structure M-0-si is a capacitar whose capacity can be denoted by cox. The voltage across this capacitor is the excess gate voltage with respect to  $V_T$

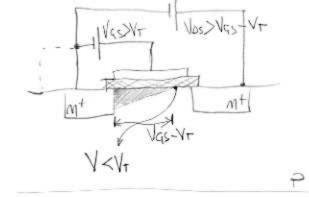

In triode region, the MOSFET behaves like a veriable resistor whose resistence Vaszan value (Vas-VT) which is the excess voltage v. 2. t. VT. The resistance of course depends on the phisical properties of the transistor. Whe said that in order to be able to conduct current, the voltage of forence between the gate and the substrate must be greater than Vr. at the shoin, this voltage obifference is VgD = Vgs - VDS > VT > VDS < Vgs - VT. What happens if Vos > Vas-VT? Consider the case Vos= Vgs-VT=> VgD=VT So it like the voltage is just enough to guarantee continuity of the channel, If Vos is a little bit greater than Vas-Vthen there will be a point in the channel where Y<V+

on one side and V(y) on the other side. So:

the total current is then the integral of the linear density current along the entire channel:

$$I_{D} = \int_{0}^{L} I_{0} y_{0} y_{0} = \mu_{m} W Cox \int_{0}^{V_{0}} \left[ V_{0} - V_{T} - V(y) I_{0} V \right] =$$

$$= \mu_{m} Cox \frac{W}{L} \left[ \left( V_{0} - V_{T} - \frac{1}{2} V_{0} \right) V_{0} \right] =$$

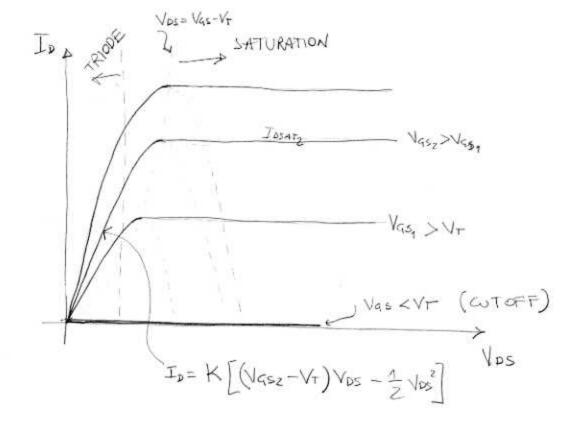

If Vos is very small & Io × K [(Vas-Vr)Vos].

The MOSFET then looks like a resistant between source and chain, whose resistance is equal to 1/K(Vas-Vr). When the MOSFET aperates in this conditions, we shall say that it greates in TRIODE REGION

This phenomenon is called pinch-off. The current cannot increase anymore even if Vos increases. because the voltage

between the source and the pinch-off point is constant and equal to Vas-VT. This region of operation is called

SATURATION .

Saturation hoppens for Vos=Vas-V+ after which the airent remains constant to I DSAT = K (VGS-VT) (VG-VT) - 1/2 (VGS-VT)2 =

$=\frac{K}{2}(V_{qs}-V_{T})^{2}$ Substituting VDS = VGS - VT

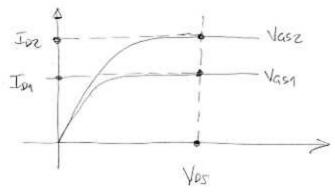

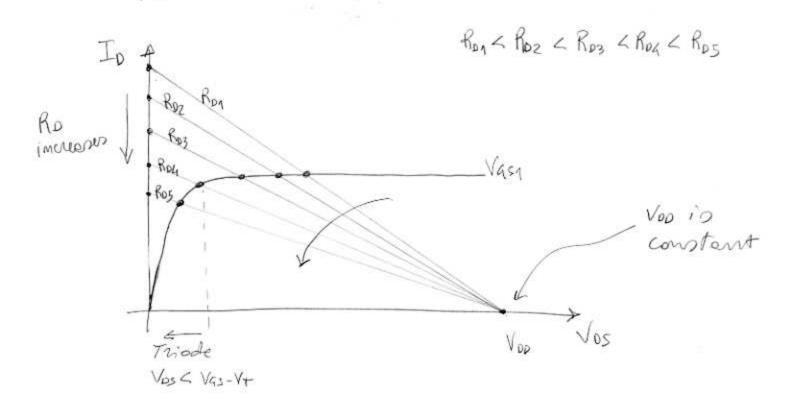

Putting everything together we can plot the I-v characteristic of the mosfet:

There few things that on important to mote. Befor saturation, the arrent equation is quadratic and if Vos is small then it can be approximated by a line (which is a resistor between phaim an source).

In staturation the current doesn't depend on Vos. The saturation current is a function of Vqs.

If the trensistor is in returnation 11 and we change vas a little bit, then the the drain arrent is going to change:

Vos is constat in this example (it is a voltage source). If we change Vas then ID is going to change and in particular:

$$I_{D1} = \frac{k}{2} \left( V_{QSI} - V_T \right)^2$$

$$I_{D2} = \frac{k}{2} \left( V_{QSZ} - V_T \right)^2$$

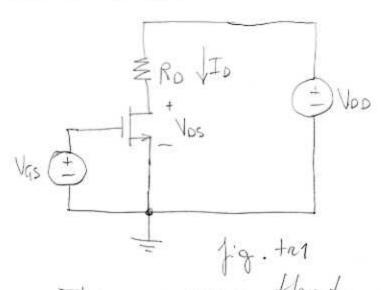

What we can do is to use a resister in order to transform a change in current in a change in voltage.

Now using KVL Voo-Vos-RoIp=0 ⇒ Vos= Voo-RoIp (\*)

This means that more if Vas changes, I is going to change and also Vos is going to change (it is not constant anymore because it's equat to Voo minus the voltage chop on Ro).

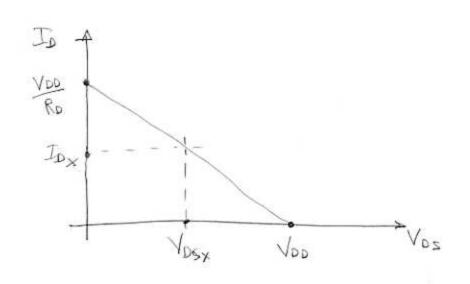

Equation (\*) relate Vos and ID in the following way:

$$I_{D} = \frac{V_{0D} - V_{0S}}{R_{D}} = -\frac{V_{0S}}{R_{D}} + \frac{V_{0O}}{R_{D}}$$

this equation is a line in the Vos-Io plane. This line has a negative anguel coefficient an intersect the Vos axis for Vos= Voo an the Io axis for Io = Voo/Ro

This is called the "bad line". It gives Vos once we fix Io.

The transistor Vos, To characteristic is going to provide another equation. The intersection of the load line with transistor characteristic gives us the aurent Io and the voltage Viss. So besically if we fix a certain Vasi then we select a curve for the transistor in

John Vasy

Vosy

Vosy

Vosy

Vosy

Vosy

Vosy

Vosy

It say

In = \( \frac{1}{2} \left( \frac{1}{2} \right)^2 \)

in saturation.

Now using the

intersection with the load line we can know Vosa

what hoppens if we increase Ro and mentein Vas = Vasa?

The transistor characteristic is going to stay the same. Since the transistor was an gimally in saturation, I o doesn't change. So the voltage shop Ro I o will increase and Vas will decrease. When Vos becomes less than Vas, - V+ the transistor switches from saturation to triode. Using the load line, this is easy to verify:

## SMALL SIGNAL APPROXIMATION

We want to study the behaviour of a transistor im saturation in the case that the voltage between gate and source is the superposition of two voltage: a DC voltage which is constant with time and an AC voltage which is mot constant.

I will use the following motation: Vas upper case letters with upper case subscript for DC quantities

Ngs lover case letters with lower case subscript for AC quantities

V qs = Vqs + Ng, lower case 'letters with upper cose subscript for the sum of both

the gate to source voltage in:

Consider Ngs=0, so only the DC voltage sources are present. also assume that Vgs>VT and Nos≥ Ngs-Vr so the transistor is in saturation

Then:

$$I_0 = \frac{K}{2} \left( V_{qs} - V_T \right)^2$$

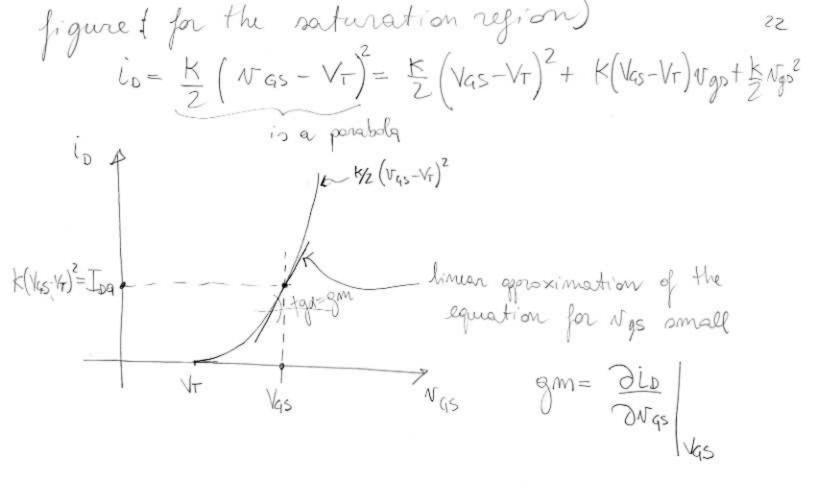

Now let  $Ng_0 \neq 0$  then we have  $i_0 = \frac{K}{Z} \left( N_{qs} - V_T \right)^2 = \frac{k}{Z} \left( V_{qs} - V_T + N_{go} \right)^2 =$   $= \frac{K}{Z} \left[ \left( V_{qs} - V_T \right)^2 + 2 \left( V_{qs} - V_T \right) N_{gs} + N_{gs}^2 \right] =$   $= I_0 + K \left( V_{qs} - V_T \right) N_{gs} + N_{gs}^2 = I_0 + i_d$

The figure represents to an function of vas when the transistor is in saturation

Nas= Vastngs and the two components (Vas and Nas) are represented in figure. Vas is a big signal while vasz is small. You can see the effect on id. id, is the drain current when the imput is big (Vasa) whereas id is the drain current when vas is small (vasa) you can see how id, is not a simulated but is "I distorted" by the guesdratic term.

id is besically a simulation of proportional to vasz.

for small signal we can neglect  $V_{gs}^{2}$  meaning 19  $\frac{1}{1}$   $\frac{1}{1}$

gm = K(VGS-VT) is called transconductance So basically we have neglected the square term and we obtained a linear model:

$N_{GS} = V_{GS} + N_{gS}$   $i_D = I_D + gmN_{gS}$

The behavior of the circuit can the be described as superposition of a OC circuit where all AC sources are set to zero, and on AC circuit where all DC sources are set to zero.

The general analysis then can be divided into two stops:

-DC (consider AC sorces quelzero)

-AC (consider DC sorces equal zero)

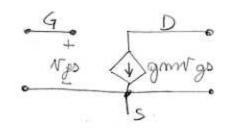

When all DC sources one zero we have

il = gm vgs

then the transistor is behaving like a voltage controlled current source.

We can built then the equivalent small signal model for a tronsistors:

This model is of course linear (runniber that we have neglected vgs? on purpose) and is valid for AC signals only. When dealing with transistor then we always distinguish two phoses:

-DC analysis ( load line)

-AC emplyer's ( use the equivalent Gircuit and then Node-Voltage emplysis) In the first phon we set all AC sources to o and using the lood line analysis (or alternatively workingout the mon linear equations) we compute Vas, Vos and ID. We call this point the quiescent greating point and denote the quantic with a subscript q: Vasa, Vosa, Ioq.

In the second phose we set all DC sources to \$\phi\$, we substitute the transistor with the linear equivalent circuit, and we apply standard tech mignes for solving linear circuits, marnely mode-voltage analysis or mesh-current analysis.

Note that parameters of the small signal equivalent circuit depend on the quiexcent point.

This procedure corresponds to the following.

The graph io= f(ras) is shown in