# EE 40

### Homework #6

# Due Tuesday, April 22, 2003, 3:30 PM

### 40 Total Points Possible

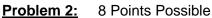

#### Problem 1: 10 Points Possible

For the CMOS logic circuit at left, assume that  $\varepsilon$  is a small positive number, such that an NMOS transistor with  $V_{\text{GS}(\text{N})}$  =  $V_{\text{TH}(\text{N})}$  +  $\epsilon~$  (or PMOS transistor with  $V_{GS(P)} = V_{TH(P)} - \epsilon$ ) would be "barely" turned on.

An NMOS transistor with  $V_{GS(N)} = V_{DD} - (V_{TH(N)} + \epsilon)$  (or PMOS transistor with  $V_{GS(P)} = -V_{DD} - (V_{TH(P)} - \epsilon))$  would be "fully" turned on.

Make an "educated guess" for the mode of operation of each transistor in the circuit at left. Assume  $V_{TH(N)} \approx -V_{TH(P)}$ .

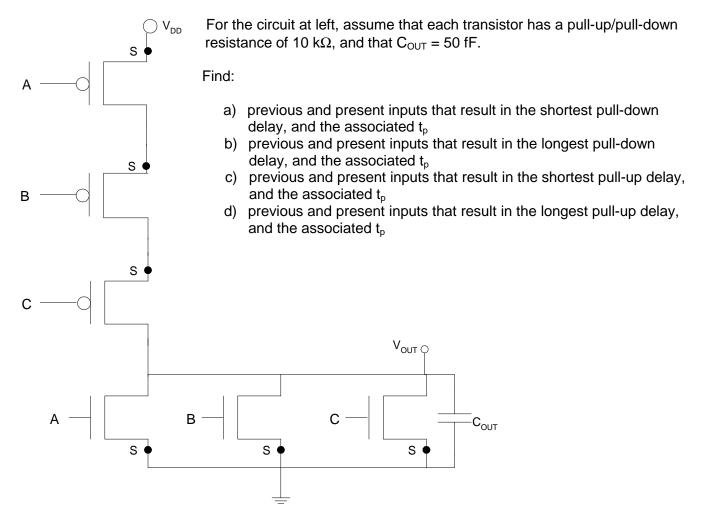

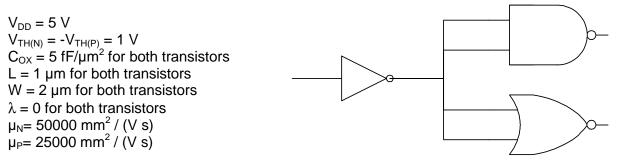

# **Problem 3:** 12 Points Possible

Consider the logic circuit below. Each logic gate is constructed using the appropriate CMOS circuit given in lecture. With

- a) Find the low-to-high and high-to-low propagation delays t<sub>p</sub> for the inverter in the circuit as shown. Take into account the pull-up and pull-down resistances of the transistors (which you must calculate here), as well as the gate capacitances of the attached gates (calculate also).

- b) Suppose I require that the maximum propagation delay through the inverter is 2 ns. Determine the maximum fan-out: the maximum number of NAND or NOR gates that can be attached to the inverter output if the propagation delay through the inverter is to be 2 ns maximum.