## Supplementary Reader II

# EECS 40 Introduction to Microelectronic Circuits

Prof. C. Chang-Hasnain Fall 2006

## **Table of Contents**

| Chapter 2. | Diode Circuits                           | 1 |

|------------|------------------------------------------|---|

| 2.1        | Physical Behavior of Diodes              | 1 |

| 2.2        | Solving Diode Circuits                   | 2 |

| 2.2.1      | Proof by Contradiction Approach          | 2 |

| 2.3        | Load Line Analysis                       | 2 |

| 2.4        | Zener Diodes                             | 3 |

| 2.5        | Applications for Diodes                  | 4 |

| 2.5.1      | Clipper Circuit (a.k.a. Limiter Circuit) | 4 |

| 2.5.2      | Level Shift Circuit                      | 6 |

| 2.5.3      | Clamping Circuit (a.k.a. DC Restorer)    | 7 |

| 2.5.4      | Rectifier Circuit                        | 7 |

| 2.5.5      | Peak Detector1                           | 1 |

| 2.5.6      | Voltage Doubler Circuit 1                | 2 |

| 2.5.7      | Diode Logic Gates 1                      | 3 |

#### Acknowledgements

We thank the writing assistance of Abhinav Gupta, Kevin Wang, Henry Wang, and Wendy Xiao-Xue Zhao, and detailed editing by Isaac Seetho, Yu Ben, Timothy C Loo, Jia Zou, and Michael Krishnan.

## **Chapter 2. Diode Circuits**

#### 2.1 Physical Behavior of Diodes

A diode is a simple two terminal device. The two terminals are labeled anode (positive side) and cathode (negative side). The diode symbol used in a circuit is shown in Fig. 1a, with the definition of the plus and minus directions of voltage and current. A positive voltage applied to the diode is referred as a forward bias and negative, a reverse bias. In this part of the course, we will introduce three models to describe the current-voltage (I-V) characteristics of a diode: the ideal diode model, a simple piecewise model and the Shockley equation.

An ideal diode has only two modes of operation: off and on, as shown in Fig. 1b. When the diode is "off", it passes through no current but the voltage can be any value less than zero. It behaves like an open circuit. When the diode is "on", the voltage is clamped at zero while its current can be any positive value. Hence, it acts like a short circuit.

| Anode $\bigcirc \qquad \qquad \stackrel{i_D}{\longrightarrow} \bigcirc$ Cathode + $v_D$ -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $i_D$ Diode on<br>Diode off $V_D$                                                          | $- \xrightarrow{i_D} V_{ih} V_D$                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Fig. 1a circuit symbol of a diode (same as<br>Hambley 10.1a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Fig. 1b Ideal diode current-<br>voltage characteristics (on<br>and off states are labeled) | Fig. 1c Simple piecewise<br>model (threshold voltage<br>labeled) |

| $ \begin{array}{c c}  & i_D \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & & \\  & &$ | V <sub>BD</sub>                                                                            | $i_D$<br>$I_S$ $v_D$                                             |

| Fig. 1d Schockley equation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Fig. 1e real diode wi                                                                      | th breakdown voltage                                             |

The simple piecewise model is similar to the ideal diode model with "off" and "on" states being open and short circuit, respectively. The only difference is the inclusion of a threshold voltage. As shown in Fig. 1c, when the diode is biased below a certain threshold voltage, it is "off", i.e. the current passing through the diode is zero. When the diode is "on", voltage is clamped at this threshold voltage while current can be any positive value depending on the rest of the circuit. In EE 40, this threshold voltage is set to be 0.7 V. Note, this number is just a matter of convention and not based on fundamental physical laws. In this set of notes, this simple piecewise model is slightly different from the model used in section 10.5 of Hambley. This model is a simpler version of the piecewise-linear model described in 10.5, hence the name "simple piecewise model."

Shockley Equation model, shown by Fig. 1d, is more accurate than the first two. With forward bias, the current increases exponentially with voltage. For reverse bias, the current is negative and saturates at a saturation current. Since it is difficult to use this model to reach analytical solutions, for the circuits in this chapter, we use the ideal and simple piecewise model.

None of the models describe what happens when the voltage bias becomes a large but negative value, which is known as reserve bias breakdown voltage, for example, as in Zener diodes (Hambley 10.3). In the circuit analysis part of this course, we will simply add a reverse voltage as in 10.3. The physics behind the

reverse breakdown phenomenon and the Shockley equation will be briefly discussed in the next Chapter. However, you will not see more detailed discussion until EE 105 and EE130, which I hope you will take next year.

Note, no matter which model you use, a diode has its I-V curve passes through the origin, i.e. with zero voltage there should be no current flow. The only exception is when unless there is an external source to generate electrons, e.g. in the case of sun light or laser beam shinning on a photodiode. In general, if we did not specifically mention photo-generation of electrons, zero voltage bias across a diode leads to zero current. Do not lose this "common sense" when dealing with diode problems.

$$I = 0 \iff V = 0$$

#### 2.2 Solving Diode Circuits

#### 2.2.1 Proof by Contradiction Approach

The proof by contradiction method uses guess-and-check, also discussed in the text book.

- For each diode in the circuit, "guess" an "on" or "off" state and replace it with the corresponding model (open circuit for "off", and 0.7 volt source for "on")

- If diode is assumed on, the current should flow into the positive terminal of the diode. If diode is assumed off, the voltage should be negative across the diode, i.e. reverse biased.

We apply the contra-positive of the second bullet above to contradict our guess. (If  $A \rightarrow B$ , then Not  $B \rightarrow$ Not A) In other words, if we solve the circuit and find a negative current through an "on" diode or a voltage greater than 0.7V across an "off" diode, we guessed the wrong states.

#### 2.3 Load Line Analysis

Load line analysis is simply about finding the intersection point based on the physical characteristics of a device (the load), the physical characteristics of a driving circuit, based on fundamental laws such as KCL and KVL. For our present discussion, the diode is our load, but this powerful technique can be applied to other loads as well.

From the physical behavior of a diode, we know that a diode behaves in a certain way. This presents an I-V characteristic based on the model we choose. When this diode is placed in a simple circuit, the circuit will also want to dictate the way it behaves. In particular, by KVL, the driving circuit and the load must see the same voltage at their interface. In addition, the current out of the driving circuit must match the current into the load.. For the circuit to be consistent, both of these constraints must be satisfied. Therefore, we find the intersection of the curves representing the physical characteristic of a diode and the curve representing the manner in which the diode will behave when placed in a circuit (the load's IV curve, or "load line"). We call this intersection point, the "operating point", because it is the point at which the device will operate.

The physical characteristic of a diode (or other device) is sometimes represented by a set of family curves at different operating conditions. For example, in photodiode, two curves typically exhibit for the conditions with and without light illumination. In the case of MOSFET, characteristics are represented by  $I_{ds}$ - $V_{ds}$  at different gate voltage ( $V_g$ ) levels. But no matter how many curves are used to represent the physical characteristic of the diode, you are simply intersecting this characteristic with the behavior you obtain from analyzing the load in a circuit. Each intersection point of the characteristic and the load line indicates the Q-point in that particular condition.

The circuit may become more complicated than a simple source, diode, and resister in series. But even in a more complicated circuit, we can simplify the problem by first finding the Thevenin equivalent circuit of the linear portion of the circuit. Then, we can resort to the fundamental KVL principle to obtain the equation for the load line.

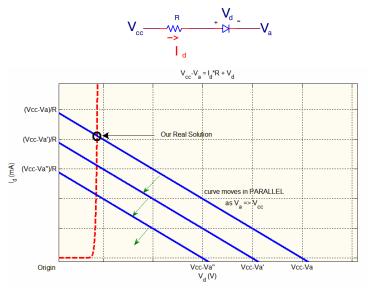

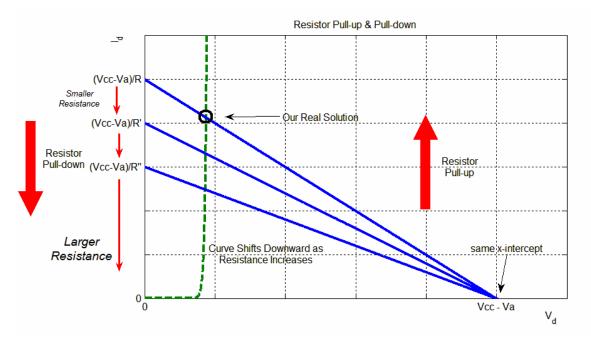

Once we find the load line equation using KVL, we can graph its I-V characteristic and find the solution from the intersection point. As shown in Fig. 2, as the source voltage is increased while keeping the resistance constant, the load line is moved upwards in parallel to the original curve. The intersection point is changed accordingly. If, however, the value of the resistance is changed, the y-intercept of the load line is changed accordingly. When the resistance is decreased, the y-intercept increases, and the curve is pulled up with the same x-intercept. The official terminology for this upward shift due to a decrease in resistance is "resistor pull-up." Fig. 3 shows how the curve shifts downward as we increase the resistance. Because the x-intercept remains the same, the curve does not shift in parallel.

It is important to familiarize yourself with the various graphical representations of the load line because we sometimes may simply read off the values by examining the x and the y intercepts. For example, in Fig. 2, if we assume  $V_a$  is zero, then we instantly find the value of  $V_{cc}$  and R numerically by examining the x-intercept and the y-intercept, respectively.

Fig. 2. The load line is shifted in parallel, indicated by the arrow, when the parameter  $V_a$  approaches  $V_{cc}$ , assuming that the resistance is kept at a constant value. The circuit for the particular load line is shown above.

Fig. 3. The load line shifts as we vary the resistance, assuming Vcc and Va as constant. The curve does not shift in parallel because the x-intercept remains the same.

#### 2.4 Zener Diodes

In a normal diode, the "activities" occurs in the first quadrant of the I-V characteristic. In Zener diode, the "activities" occurs in the third quadrant. In Zener diode, we assume that upon a certain negative voltage, named the breakdown voltage, the magnitude of the current increases dramatically. We are not so much interested in the positive voltage regime, but rather more in how the diode will behave in the realm of negative voltage. We still apply the same technique to obtain the load line equation from the circuit.

Example 10.3 in Hambley shows the graph of a Zener diode characteristic and its load line for two different supply voltages. The motivation for using a Zener diode rather than a regular diode is the high voltage switching applications. While a regular diode provides switching behavior, the voltage involved is fairly small. With Zerner diode, voltage switching occurs on the order of magnitude of 100 V. Moreover, a very small change in the voltage induces a large change in current; therefore, the resistance is very small by Ohm's Law, as the slope of the Zener diode characteristic is fairly large.

#### 2.5 Applications for Diodes

The widespread applications for diode include, but are not limited, to the following:

- AND/OR gate

- Half & full wave rectifier

- Clamping circuit

- Clipper circuit

- Peak detector

- Level shift

- Voltage doubler

In the following section, I will discuss each application separately and briefly.

#### 2.5.1 Clipper Circuit (a.k.a. Limiter Circuit)

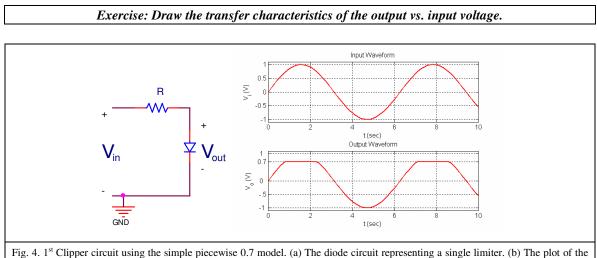

input voltage and the resulting output voltage as a function of time.

To begin the analysis of clipper circuit, we present two basic forms. In each of the two forms, we will examine the transfer characteristic, namely the output voltage as a function of input voltage, and the output voltage as a function of time.

The first basic form is shown in Fig. 4. We will use the simple piecewise 0.7 model in our analysis.

If the input is less than 0.7 V, the diode is off, the output voltage will be equal to the input voltage because the diode is an open circuit. The slope of the transfer characteristic curve for input less or equal to 0.7 V will have a slope of 1. If the input is greater than 0.7V, the diode is on, the output will be clamped at 0.7 V. The difference voltage between the input and 0.7V will be "carried" by the series resistor, as there is now current flow in this case. Assuming the input is a sine wave with a magnitude of 1, the output waveform as a function of time is shown in Fig. 4(b). When the voltage exceeds 0.7 V, the output voltage is clipped off and remains at 0.7 V.

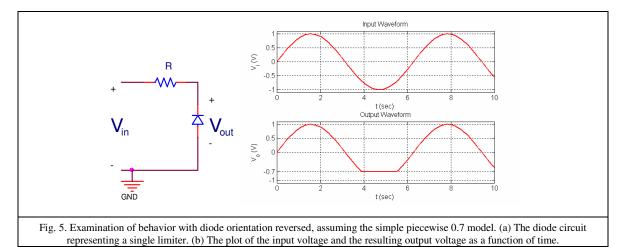

If the orientation of the diode is switched, as shown in Fig. 5(a), the same analysis follows. If the input voltage is greater than -0.7V, the diode is an open circuit, and the output voltage is equivalent to the input voltage. On the other hand, if the input is less than -0.7V, the diode is on and is a short circuit, thus output voltage is limited to be -0.7V. Fig. 5(b) shows the output voltage as a function of time when input is a sine wave with 1V magnitude. When the input voltage falls below -0.7V, the output voltage is clipped off and remains at -0.7V.

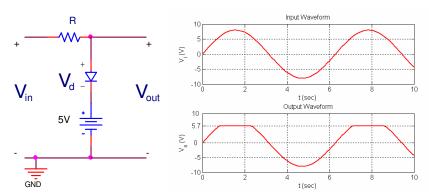

With the first canonical form, we have a limitation on the value the output becomes bounded, i.e., it is bounded by either 0.7 V or -0.7 V. We can change this value by adding a battery in series with the diode. We obtain our second canonical form by augmenting this battery, as in Fig. 6. The input needs to become (0.7 + battery voltage) Volts before the output voltage in the transfer characteristic flattens out. Furthermore, if the orientation of the battery is switched, the clipping will occur in the negative region.

Fig. 6. The  $2^{nd}$  canonical form for analyzing clipper circuit, assuming the simple piecewise 0.7 model. (a) The new circuit with battery added in series with the diode. (b) The plot of the input voltage and the resulting output voltage as a function of time.

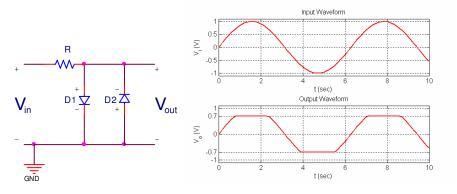

What we have examined is known formally as a single limiter, since the circuit will limit the output voltage on one side. By placing the two diodes with different orientation together in parallel, we obtain a circuit that bounds the output voltage on both sides. This double clipping action is more formally known as a double limiter. An example is shown in Fig. 7. The output voltage is both bounded below and above by 0.7 V and -0.7 V, respectively.

Fig. 7. A combination of two canonical forms in parallel, again assuming simple piecewise 0.7 model. (a) The double limiter circuit. (b) Plot of input voltage waveform and the resulting output voltage waveform.

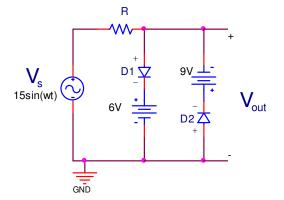

Using the second canonical form, we can achieve a clipping at different voltages by placing different battery voltages. A classical example, used both in lecture and the textbook, is shown in Fig. 8. Knowing the canonical forms, we easily simplify the problem by examining each of the two parallel branches separately and superposing the two results.

Fig. 8. Clipper circuit diagram.

#### 2.5.2 Level Shift Circuit

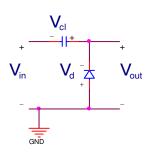

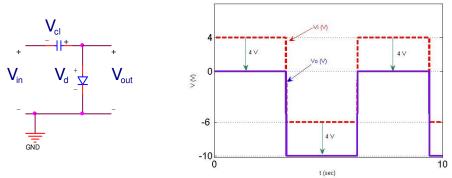

A level shift circuit is composed of a capacitor in series with a diode. Note the orientation of the diode in relation to the output voltage and also note the polarity of the capacitor, as shown in Fig. 9. The intuition behind a level shift circuit is gained by considering the two cases with the diode on and off separately. We will use the ideal diode model. When the diode is turned on, we have a short circuit; hence the output voltage is zero. At this stage, the capacitor will get charged to an equal and opposite value as the input voltage. On the other hand, when the diode is turned off, the output voltage is given by KVL,  $V_{out} = V_{cl} + V_{in}$ .

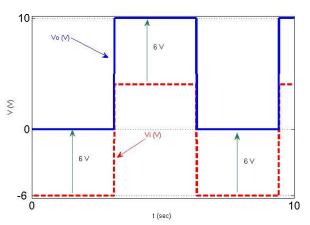

Let's look at an example now. Consider a square wave as an input passed into the level shift circuit shown in Fig.10, with the positive peak at 4 V and negative peak at -6 V. Initially, when the square wave takes a negative value, the diode becomes a short circuit; hence the output voltage becomes zero. At this stage, the capacitor will get charged to become the negative of the input voltage; KVL shows us that  $V_{in} = -V_{cl}$ . Thus  $V_{c1}=6V$  here. When the input jumps to a positive value, the diode will be turned off, and  $V_{out} = V_{cl} + V_{in} = 4 + 6 = 10$  V. When the input returns to -6V again, the diode is again a short circuit and  $V_{out} = 0$ . But in this case, the capacitor is already fully charged to 6V, there will be no longer current flow. The resulting waveform is shown in Fig. 10.

Fig. 9. The prototypical level shift circuit. Note the orientation of the diode and capacitor in relation to the input voltage.

Fig. 10. The output voltage waveform,  $V_{out}$ , shown in solid lines, is obtained when the input voltage waveform,  $V_{in}$ , shown in dashed lines, is passed into the level shift circuit in Fig. 9. The resulting output waveform is shifted upward by 6 V.

If we switch the orientation of the diode (but still define all the polarities in the same way), the square wave will be shifted downward instead of being shifted upward. This new orientation is shown in Fig. 11. The polarity of the capacitor and output voltage remained the same. The only change is that the direction of the diode is reversed. The resulting waveform will then take the form as shown in Fig. 12.

Fig. 11. Reversing the orientation of the diode while keeping the polarity the same.

Fig 12. The output voltage waveform,  $V_{out}$ , shown in solid lines, is obtained when the input voltage waveform,  $V_{in}$ , shown in dashed lines, is passed into the level shift circuit in Fig. 10. The resulting output waveform is shifted downward by 4 V.

| Exercise: Draw the diode current as a fund | ction of time. |

|--------------------------------------------|----------------|

|--------------------------------------------|----------------|

#### 2.5.3 Clamping Circuit (a.k.a. DC Restorer)

The level shift circuit shows that the square wave can be shifted upward and downward, depending on the orientation of the diode. In either case, the wave is bounded above or below by the threshold value of the diode. In other words, the peak or trough of the waveform is "clamped" at this particular threshold value of the diode. Because we assume the ideal diode model, the output waveform becomes bounded by 0 V. If we had assumed the simple piecewise 0.7 model, the output waveform would become bounded either below or above by 0.7 V. We can clamp the waveform by utilizing different diodes with different threshold value. However, we sometimes wish to clamp the waveform with a large range of possible voltage values. To accomplish this greater freedom, we add a battery in conjunction with the diode. Thus, it can be seen that clamping circuit is a more generalized class of a level shift circuit.

#### 2.5.4 Rectifier Circuit

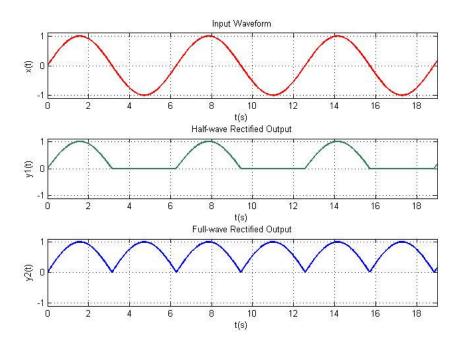

Rectifier circuits are divided into two classes – half-wave and full-wave rectifier. Consider a sinusoidal input signal x(t) as given. Mathematically, a half-wave rectifier produces an output  $y_1(t) = \frac{|x(t)| + x(t)}{2}$ , while a full-wave rectifier produces an output  $y_2(t) = |x(t)|$ . These outputs,  $y_1(t)$  and  $y_2(t)$ , represent a half wave and a full-wave rectified output, respectively, assuming the ideal diode model. An example showing the input and output waveform for a half-wave and a full-wave circuit is shown in Fig. 13. If we were mathematicians, our discussion of rectifier circuits would terminate here; however, as an engineer, we want to know how to construct circuits to produce the output signals  $y_1(t)$  and  $y_2(t)$  given an input signal x(t).

Fig. 13 Half-wave rectified and full-wave rectified signals. The topmost signal is the input signal which is fed into a half-wave rectifier to produce the middle output signal, and fed into a full wave rectifier to produce the bottom signal.

#### Half-Wave Rectifier

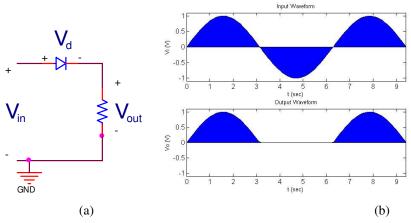

Fig. 14 shows the classical half-wave rectifier circuits. To analyze the output, we follow the input voltage and apply fundamental diode principles and KVL. When the input is positive, the diode behaves as a short circuit, thus the output voltage is given by  $V_{out} = V_{in} - V_d$  (KVL). Assuming an ideal diode model,  $V_{out} = V_{in}$ . Assuming a simple piecewise 0.7 model,  $V_{out} = V_{in} - 0.7$ . When the input is negative, the diode is reverse biased and behaves as an open circuit. Thus, the output voltage is zero since no current flows in the closed loop.

Fig. 14. (a) Half-wave rectifier circuit. (b) A sinusoidal input and the resulting output.

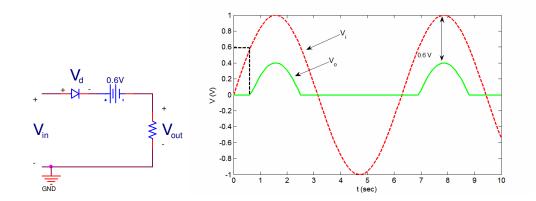

Now consider adding a 0.6 V battery to produce the circuit shown in Fig. 15. The ideal diode model is still assumed. The diode will be on only when the input is greater than the voltage across the battery, 0.6 V, since only then will the voltage across the diode be positive. ( $V_d = V_{in} - 0.6 \text{ V}$ ) The output voltage will be  $V_{in} - 0.6 \text{ (KVL)}$ . Whenever the input voltage falls below 0.6 V, the diode will be reverse biased. Thus, a zero current implies zero voltage.

Fig. 15. Adding a 0.6 V battery to the circuit produces the corresponding output signal, shown in green from the input signal, shown in red. Ideal diode model is assumed here.

#### Full-Wave Rectifier

A full-wave rectifier can be constructed in two ways:

- 1. Using two AC sources and two diodes

- 2. Using a diode bridge

The first method composes of two sources which have  $\pi$  phase difference along with two diodes, as in Fig. 16. When  $V_{s1}$  is positive,  $V_{s2}$  is negative. Hence the top diode will be a short and the bottom diode will be an open. On the other hand, when  $V_{s1}$  is negative,  $V_{s2}$  is positive. Hence the bottom diode will be on and the top diode will be an open circuit. Therefore, we obtain the resulting waveform as shown in Fig. 13. In practice, a transformer can be used to provide the two out-of-phase voltage sources.

Fig. 16. A full-wave rectifier implemented using two AC sources and two diodes model. The two voltage sources are out of phase, as seen from the left plot.

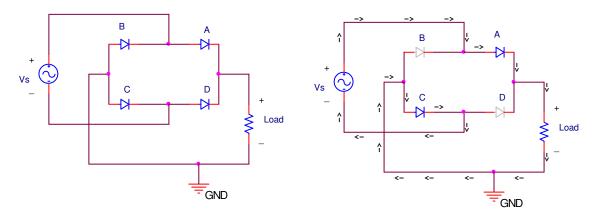

A second way to construct a full-wave rectifier is to use a diode bridge. This configuration is used because sometimes it may be impractical to obtain two voltage sources. Fig 17 shows a diode bridge. The four diodes are aligned such that diode A and C orient in the same direction and diode B and D orient in the same direction. The output is taken across the load resistor. The negative lead of the resistor is essentially the ground that connects to the junction between B and C.

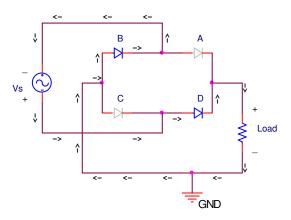

In the positive portion of the cycle, both diode A and C will be on and both diode B and D will be under reversed bias. The current will flow through diode A, the load resistor, the ground, and return through diode C. The direction of the current is shown by arrows in Fig. 18. Diode B and D is shaded to indicate that they are both under reverse bias and off.

Fig. 17. A full-wave rectifier implemented using a diode bridge model.

Fig. 18. The input is in the positive cycle. The arrows show the path of the current. Diode B and D, shown in gray, are both under reverse bias and therefore off.

In the negative portion of the cycle, the opposite occurs. Diode B and D will be on and diode A and C will be under reverse bias. The current flows through diode D, the load resistor, and returns through diode B. This scenario is shown in Fig. 19. Again, the shading of diode A and C indicate their reverse bias condition, and the arrows show the path of the current.

Fig. 19. The input is in the positive cycle. The arrows show the path of the current. Diode A and C, shown in gray, are both under reverse bias and therefore off.

In either case, current will flow through the load resistor from the marked positive lead toward negative. Therefore, the voltage measured across the load will always be positive, so we obtain a full-wave rectified version of the original sinusoid.

#### 2.5.5 Peak Detector

Peak detectors have useful applications in converting an AC signals into DC signals. They also have extremely important applications in envelope detection.

Fig. 20. Peak detection. (a) The top waveform is fed into a peak detector circuit to produce the bottom curve, assuming the capacitance is nearly infinite. (b) Peak detection circuit.

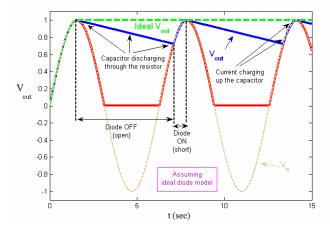

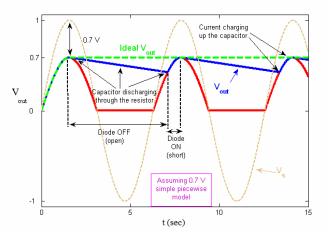

To construct a peak detector, we add a capacitor in parallel with the resistor in the existing configuration of a standard half wave rectifier. Assume the capacitor is initially uncharged.  $V_d = V_s - V_c$ . Initially, in the first quarter of a full period of a sine wave input, the diode will be a short circuit because the voltage across it will be positive, since  $V_s > V_c$ . The capacitor will get charged, thus the voltage across the capacitor will follow the input voltage.

When the input voltage reaches the peak of the sinusoidal curve, the input voltage will start to drop faster than the capacitor voltage, since we assume that the capacitor is fairly large (thus large time constant). When the input voltage drops faster than the capacitor voltage,  $V_s < V_c$ ,  $V_d < 0$ , and diode is turned off. The output voltage follows the capacitor discharge (as Vout = Vc). The shape of this curve will depend on how large the capacitance is. If the capacitance is assumed infinity, the curve will be a flat line. As the capacitor continues to discharge, there will be a point in which it intersects the input curve. After this intersection,  $V_s > V_c$ ,  $V_d > 0$ , diode will turn on again, and the capacitor follows the input curve as it gets charged up again.

Fig. 21. The plot of the output voltage  $V_{out}$  versus the input voltage  $V_s$ , given the peak detector circuit in Fig. 19 and assuming the ideal diode model. The ideal voltage output is shown in thick dashed lines, when the capacitor is assumed to be nearly infinite.

How does adding a battery in series with the diode affect the behavior of the output? We can gain an intuitive understanding of a peak detector by considering the circuit first without the capacitor. In another word, the capacitor is nonexistent, and it is simply a short where the capacitor should be. In this case, the output with a battery will be a half wave rectified shifted downward by the voltage across the battery.

Adding the capacitor will add a curve connecting from the peaks to a point on the rising portion of the peak.

Fig. 22. The plot of the output voltage  $V_{out}$  versus the input voltage  $V_s$ , given the peak detector circuit in Fig. 19 and assuming the 0.7 simple piecewise model. The ideal voltage output is shown in thick dashed lines, when the capacitor is assumed to be nearly infinite.

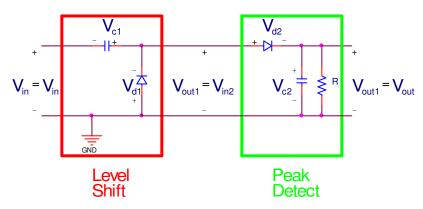

#### 2.5.6 Voltage Doubler Circuit

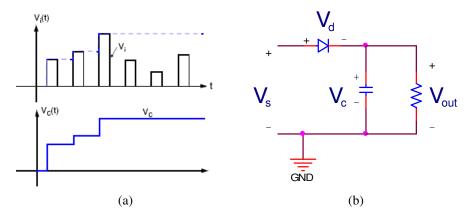

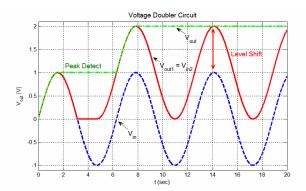

A voltage doubler is composed of a level shift circuit and a peak detector circuit in a cascade composition. In a sense, the level shift circuits will already double the input voltage. However, we use a peak detector to convert this AC signal into a DC signal. Fig. 23 shows such cascade composition. The output of the level shift circuit on the left is passed as an input to the peak detector circuit on the right.

Fig. 23. Voltage doubler circuit. A cascade composition of the level shift circuit with the peak detector. The output of the level shift circuit on the left is passed in as the input to the peak detector circuit on the right.

An example is shown below in Fig. 24. The input voltage waveform, indicated by dash lines, is passed into the circuit. After passing through the level shift circuit, a shifted version of the original waveform is formed. This new waveform is passed as an input to the peak detector circuit. The peak detector detects the peak of the new waveform, resulting in the final line indicated by 'peak detect.'

Fig. 24 A plot of the input voltage  $V_{in}$ , the intermediate voltage  $V_{out1}$  or  $V_{in2}$ , and the final voltage output  $V_{out}$ . After the initial waveform, indicated in dash, is shifted upward, the peak detector detects the peak to obtain the final output voltage.

#### 2.5.7 Diode Logic Gates

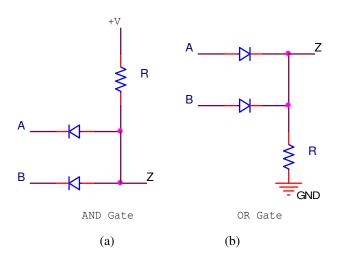

The two fundamental logic gates, AND and OR, can be implemented using diodes, as shown in Fig. 25. In an AND gate (Fig. 25(a)), the cathodes of the diodes are connected to a resistor that connects to a positive voltage source. The output is measured at point Z, the cathode of two diodes. In an OR gate (Fig. 25(b)), the anodes of the diodes are connected to a resistor that connects to ground, and the output is taken at point Z, the anode the two diodes.

Fig. 25. Diode logic gates. Z represents the output, given A and B as inputs. (a) AND gate. (b) OR gate.

#### AND Gate

AND gate is shown in Fig. 25(a). If either input A or B is low, the diode will conduct, resulting in a short circuit thus a low output Z. Only when both the inputs to A and B are high will neither of the diode conduct. The diode will behave as open circuits resulting in a high output Z. These conditions are shown in Table 1, which presents the truth table for the AND gate.

| Α | В | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Table 1. The truth table for the AND gate shown in Fig. 24(a).

#### OR Gate

OR gate is shown in Fig. 25(b). If both of the input to A and B is low, the diode will be off because the voltage across the diode is zero, hence no current flows. The output will therefore be pulled down to zero. If either of the input is high, the diode will conduct, as current flows from the higher potential to a lower potential. The output voltage at point Z will hence be a positive, high voltage, which is equal to the voltage across the resistor. Table 2 below presents the truth table for the OR gate. We can see from the table that the output is high when either one of the inputs A or B is high.

| Α | В | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Table 2. The truth table for the OR gate shown in Fig. 24(b).