# UNIVERSITY OF CALIFORNIA

# College of Engineering Department of Electrical Engineering and Computer Sciences

EECS 40 Introduction to Microelectronic Circuits

Fall 2003 Prof. King

### FINAL EXAMINATION

December 10, 2003

Time allotted: 2 hours 50 minutes (170 minutes)

| print)                        | Last                | First                                                     |

|-------------------------------|---------------------|-----------------------------------------------------------|

|                               |                     | STUDENT ID#:                                              |

| . This is a <b>CLOS</b> I     | E <b>D BOOK</b> exa | m. However, you may use 3 sheets of notes and a calculato |

| 2. SHOW YOUR<br>(Make your me |                     | ASONING on this exam. the grader.)                        |

| . Write your answ             | wers clearly (le    | egibly) in the spaces (lines, boxes, or plots) provided.  |

|                               |                     | on answers whenever appropriate.                          |

|                               |                     |                                                           |

|                               | SCORE:              | 1 / 20                                                    |

|                               |                     | 2/20                                                      |

|                               |                     | 3/20                                                      |

|                               |                     | 4/20                                                      |

|                               |                     | 5/20                                                      |

|                               |                     | 6/20                                                      |

|                               |                     | 7/ 20                                                     |

|                               |                     | 8/ 10                                                     |

Total: \_\_\_\_\_/150

# **Problem 1:** Circuit Analysis and Equivalent Circuits [20 points in total]

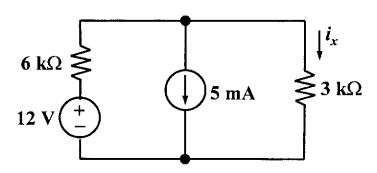

a) Consider the following circuit:

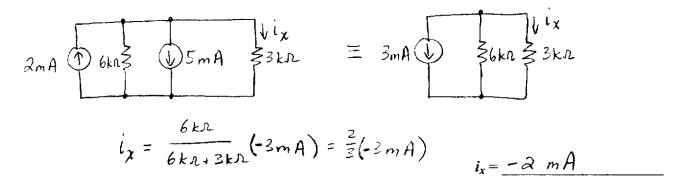

i) Use a source transformation in order to find  $i_x$ . [6 pts]

$$\frac{6kn}{3} = \frac{12V}{6kn}$$

Therefore the circuit above is equivalent to

ii) What is the power developed/absorbed by the 5 mA current source? [3 pts]

The voltage drop across the current source is ix x 3kD =-6V

$$6kn \stackrel{?}{>} 6V \stackrel{?}{\bigcirc} 5mA \stackrel{?}{>} 3kn$$

$$P = IV = (5mA)(6V) = -3$$

$$P(0 =) power = 30 mW$$

$$Power = 30 mW$$

$$P = IV = (5mA)(6V) = -30 \text{ mW}$$

$P(0 =)$  power is developed

# Problem 1 (continued)

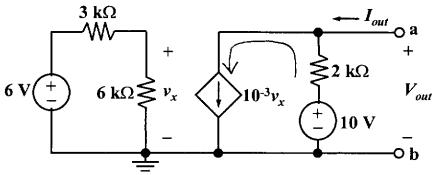

b) Consider the following circuit:

i) Find  $V_{out}$ . [6 pts]

$$V_{X} = \frac{6 \text{ kg}}{3 \text{kg.} + 6 \text{kg.}} (6V) = \frac{2}{3} (6V) = 4V$$

dependent current source value = 10-3 vx = 4x10-3 A = 4 mA

Voltage drop across Ika resistor is (-4mA)(2ka)=-8V

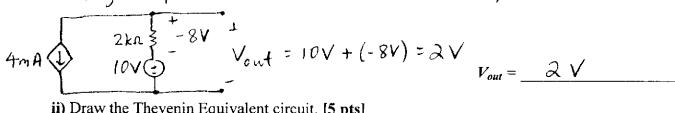

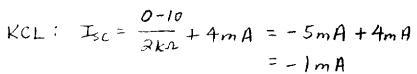

ii) Draw the Thevenin Equivalent circuit. [5 pts]

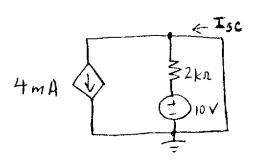

Determine the short-circuit current Is:

$$R_{Th} = \frac{V_{oc}}{-I_{sc}} = \frac{av}{ImA} = akn$$

Thevenin Equivalent Circuit:

### Problem 2: Op Amp Circuit [20 points in total]

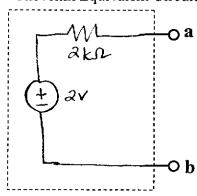

a) The following is the circuit model for an op amp circuit operating in its linear region:

Typically,  $R_{in}$  is very large (~1 M $\Omega$ ), A is very large (>10<sup>4</sup>), and  $R_{out}$  is very small (<100  $\Omega$ ).

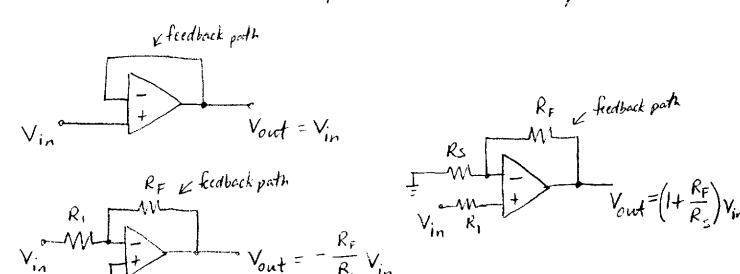

What type of feedback is used in an op amp circuit, in order to ensure that the op amp will operate in its linear region? Illustrate (with a simple diagram) how this is achieved. [5 pts]

Negative feedback is used to achieve linear operation.

(or all)

Part, of the op-amp output voltage is fed

back to the (-) input terminal. Examples:

## Problem 2 (continued)

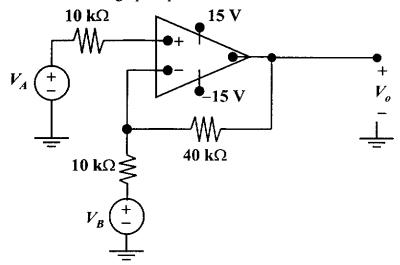

b) Consider the following op amp circuit below. You can assume that the op amp is ideal.

i) Find an expression for  $V_o$ , using superposition. [10 pts]

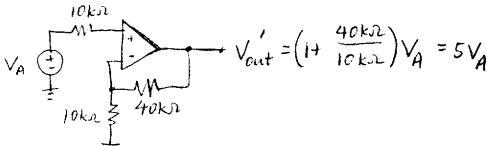

Setting VB = 0 V:

Setting

$$V_A = 0V'$$

$V_{out} = V_{out} = V_{$

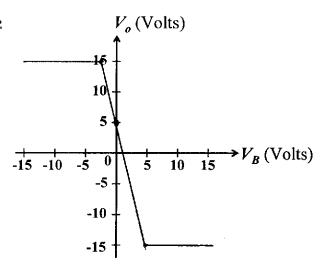

ii) Suppose  $V_A$  is fixed at 1 Volt. Plot  $V_o$  vs.  $V_B$ . [5 pts]

$V_0 = 5(1) - 4(V_B) = 5 - 4V_B$

$-15\sqrt{\langle V_0 \leq 15 V \rangle}$

due to power supplies

Problem 3: First-Order Circuits [20 points in total]

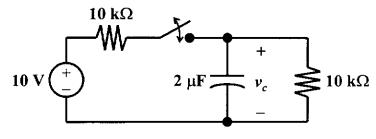

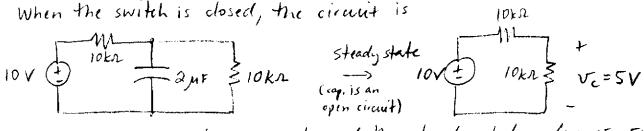

In the circuit below, the switch is open for all t < 0. The switch is closed at t = 0, and then it is opened again at t = 10 ms.

Initially, capacitor is

$$v_{c} \leq 10 \text{ k}\Omega$$

$$= v_{c} (0^{+}) = 0 \text{ V}$$

i) Write an equation for  $v_c(t)$ , for  $0 \le t \le 10$  ms. [8 pts]

The capacitor will charge up, toward the steady-state value  $v_e=5V$ The capacitor "sees" the parallel combination of the 10th resistors  $0 \le t \le 10 \text{ ms}$ :  $v_c(t) = \frac{5(1-e^{-t/10 \text{ ms}})}{5(1-e^{-t/10 \text{ ms}})}$  Volts

ii) Write an equation for  $v_c(t)$ , for t > 10 ms. [8 pts]

At

$$t = 10ms$$

,  $v_c = 0.63(5V) = 3.15V$

When the switch is open, the capacitor circuit is

RC =

$$(10k\Lambda)(2\mu f) = 20ms$$

$t > 10 \text{ ms}: v_c(t) = 3.15 e^{-(t-10ms)/20ms}$  Volts

iii) Sketch  $v_c(t)$  for t > 0 [4 pts]

#### Problem 4: pn junctions; diodes [20 points in total]

a) Consider a pn junction formed in the surface of an n-type silicon wafer maintained at T = 300K. The p and n regions are uniformly doped, as indicated in the figure below:

Schematic cross-sectional view of pn junction

In the p-type region, the electron mobility is  $100 \text{ cm}^2/\text{V} \cdot \text{s}$  and the hole mobility =  $50 \text{ cm}^2/\text{V} \cdot \text{s}$

i) Estimate the sheet resistance of the p-type region. [6 pts] (Use the following values of constants:  $q = 1.6 \times 10^{-19}$  C,  $n_i = 10^{10}$  cm<sup>-3</sup>)

resistivity =

$$\frac{1}{21/9P} = \frac{1}{(1.6 \times 10^{-19})(50)(10^{20})} = 1.25 \text{ m}\Omega - \text{cm}$$

sheet resistance =  $\frac{2}{1.25 \times 10^{-3}} \frac{1.25 \times 10^{-3} \Omega - \text{cm}}{0.1 \times 10^{-9} \text{ cm}} = 125 \Omega / \Omega$

Sheet resistance =

$$125 \Omega / \Box$$

ii) Suppose the p-type region serves as the drain region of a p-channel MOSFET in a CMOS inverter, and that the n-type substrate is therefore biased at the power-supply voltage  $V_{DD}$ . How will the pn-junction capacitance change as the PMOSFET is turned on (so that the drain bias is changed from 0 V to  $V_{DD}$ )? Explain briefly. [4 pts]

As the PMOSFET turns on, the output of the inverter charges from OV to VDD. The drain pn junction bias VDD changes from -VDD to OV.

Therefore the depletion-region width decreasing reverse bias), and hince the drain capacitance 7 increases.

# Problem 4 (continued)

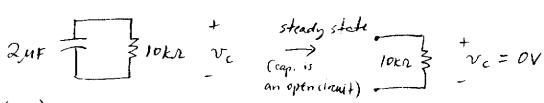

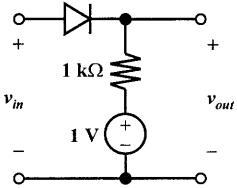

b) Consider the diode circuit below. Assume the diode is a perfect rectifier.

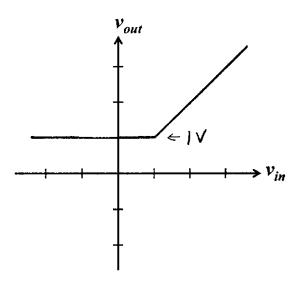

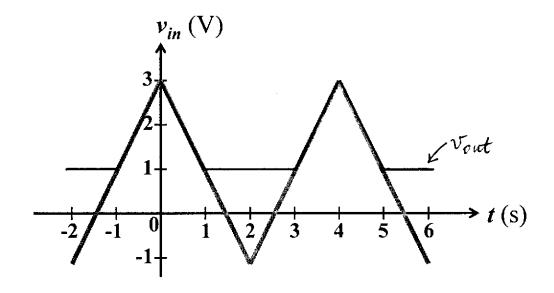

i) Plot  $v_{out}$  vs.  $v_{in}$ . [5 pts]

The diode will turn on when Vin > IV. When the diode is on, vont = Vin. When the diode is off, Vout = IV

ii) Sketch  $v_{out}$  for the given  $v_{in}(t)$ , using the same axes. [5 pts]

### Problem 5: MOSFET [20 points in total]

- a) Consider an NMOSFET with parameters  $W = 1 \mu \text{m}$ ,  $L = 0.1 \mu \text{m}$ ,  $k_n' = 10^{-3} \text{ A/V}^2$ ,  $V_T = 0.5 \text{ V}$ , biased at  $V_{GS} = V_{DD} = 1 \text{ V}$ . The areal gate capacitance  $C_{ox} = 3 \times 10^{-6} \text{ F/cm}^2$ .

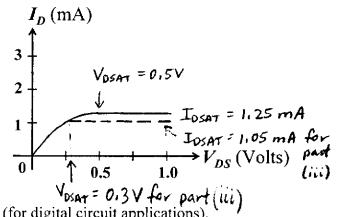

- i) Accurately sketch the  $I_D$  vs.  $V_{DS}$  characteristic in the range  $0 \le V_{DS} \le 1$  V, neglecting velocity saturation and channel-length modulation. Indicate the numerical values for the saturation voltage  $(V_{DSAT})$  and current  $(I_{DSAT})$ . [6 pts]

$$V_{DSAT} = V_{GS} - V_T = 1 - 0.5 = 0.5 V$$

$$I_{OSAT} = \frac{N!}{L} \frac{k_n'}{2} (V_{GS} - V_T)^2 = \left(\frac{1}{0.1}\right) \left(\frac{10^{-3}}{2}\right) (1-0.5)^2 = 1.25 \text{ mA}$$

ii) Estimate the effective resistance of this MOSFET (for digital circuit applications).

(Again, assume that velocity saturation and channel-length modulation can be neglected. [3 pts]

$$R_{eq} = \frac{3}{4} \frac{V_{OD}}{I_{OSAT}} = \frac{3}{4} \frac{(IV)}{I.25_{mA}} = 600 \Omega$$

$$k'_{n} = \mu_{n} C_{ox} = \lambda \mu_{n} = \frac{k'_{n}}{C_{ox}} = \frac{10^{-3}}{3 \times 10^{-6}}$$

iii) On the same plot in part (i) above, accurately sketch and label the  $I_D$  vs.  $V_{DS}$  characteristic, taking into account that the electron velocity in the MOSFET channel saturates at  $10^7$  cm/s. [5 pts]

$$V_{DSAT} = \frac{L}{\mu_n} v_{5at} = \frac{0.1 \times 10^{-4}}{(10^{-3}/3 \times 10^{-6})} 10^7 = 0.3 \text{ V}$$

$$I_{DSAT} = WC_{OX} (V_{GS} - V_T - \frac{V_{DSAT}}{2}) V_{SAT}$$

$$= (10^{-4})(3 \times 10^{-6})(1 - 0.5 - \frac{0.3}{2})(10^{7})$$

$$= 1.05 mA$$

# **Problem 5** (continued)

b) High drive current ( $I_{DSAT}$ ) is desirable for reduced equivalent resistance, to achieve smaller propagation delay to allow higher-speed circuit operation. Indicate in the table below how you would adjust various MOSFET parameters so as to increase  $I_{DSAT}$ . Briefly describe the tradeoff or disadvantage involved, if any, for each. (For example, the answer for gate length L is given.) [6 pts]

| MOSFET<br>Parameter     | To increase I <sub>DSAT</sub> , parameter must be | Associated tradeoff or disadvantage                                                                              |

|-------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Gate length L           | decreased                                         | Subthreshold leakage current increases, so that static power dissipation increases                               |

| Threshold voltage $V_T$ | decreased                                         | Subthreshold leakage current increases, so static power consumption increases.                                   |

| Channel width W         | increased                                         | Intrinsic capacitance at  the output of the logic gate increases; therefore dynamic power consumption increases. |

# **Problem 6:** Logic Circuits [20 points in total]

a) Given the following truth table for the logic function F:

| A | В | F |                                      |

|---|---|---|--------------------------------------|

| 0 | 0 | 1 | 4                                    |

| 0 | 1 | 0 | $ ightarrow \overline{\mathfrak{B}}$ |

| 1 | 0 | 1 | <                                    |

| 1 | 1 | 1 | ← AB                                 |

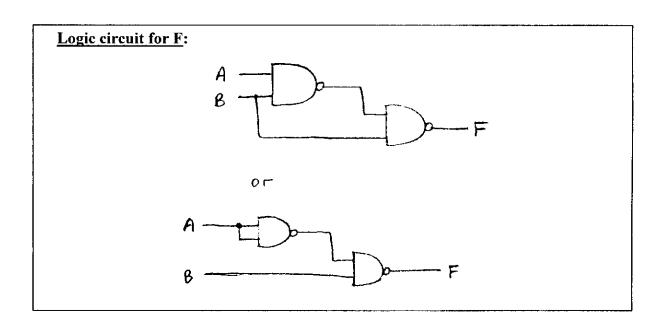

i) Write a simple logic expression for F. [2 pts]

$$F = B + AB$$

Alternative logic expressions:

$$F = A + \overline{AB}$$

$$F = A + \overline{B}$$

$$\overline{A \cdot B}$$

$$F = \overline{B} + \overline{AB}$$

ii) Implement the function F, using only 2-input NAND gates. [5 pts]

From De Morgan's Law:

$$\overline{E} + AB = \overline{B} + \overline{AB} = \overline{B \cdot \overline{AB}}$$

$$\overline{X} + \overline{Y} = \overline{XY}$$

$$A + \overline{B} = \overline{A \cdot B}$$

### Problem 6 (continued)

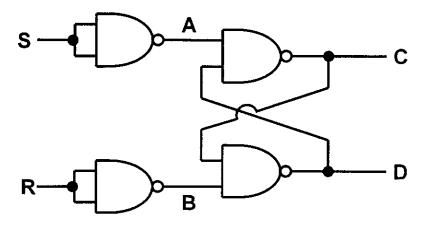

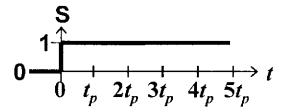

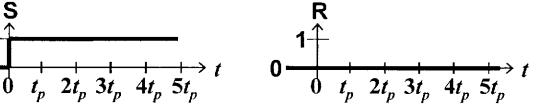

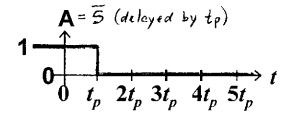

b) Consider the S-R flip-flop circuit below:

The output C is initially equal to 0, and the output D is initially equal to 1.

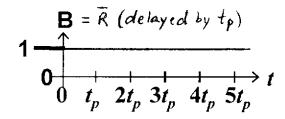

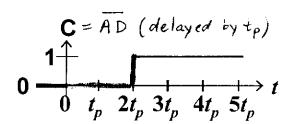

For the given S and R timing diagrams below, draw the timing diagrams (for t > 0) for A, B, C, and D on the plots provided. [13 pts]

|   |   | NAND |

|---|---|------|

| 0 | 0 | 1    |

| 0 | ı | 1    |

| ŀ | 0 |      |

| 1 | 1 | 0    |

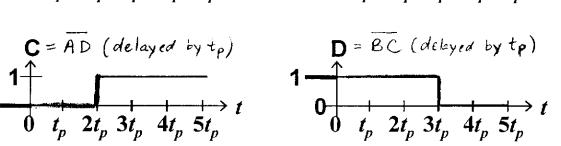

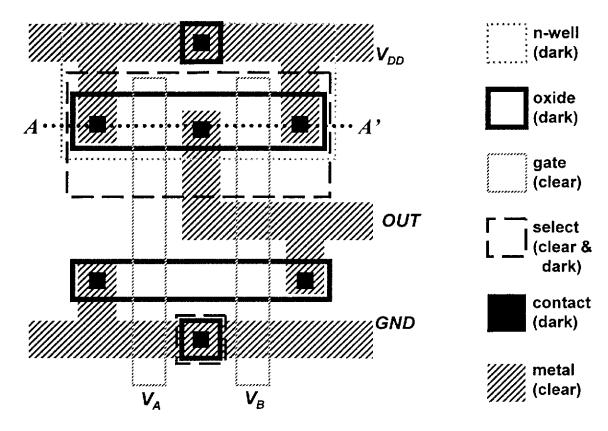

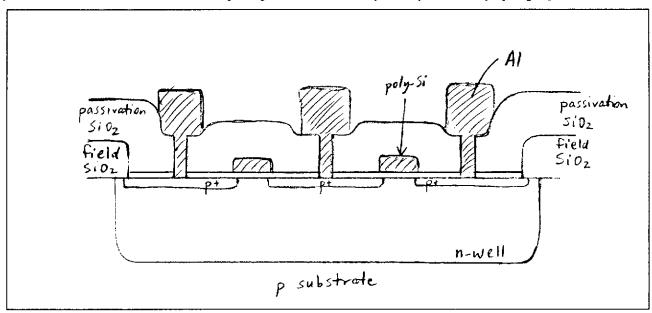

#### Problem 7: CMOS Technology [20 points in total]

The layout of a CMOS logic gate is shown below:

The following fabrication process (starting with a p-type Si wafer) is used:

- 1. Thermally grow 700 nm of SiO<sub>2</sub>.

- 2. Pattern the SiO<sub>2</sub> using the n-well mask.

- 3. Implant phosphorus and perform a high-temperature, long anneal to "drive in" the well to a depth of 1  $\mu m$ .

- 4. Remove the SiO<sub>2</sub> (using a highly selective wet etch process which does not etch Si).

- 5. Grow 0.5 μm of SiO<sub>2</sub> ("field oxide").

- 6. Pattern the SiO<sub>2</sub> using the oxide mask.

- 7. Thermally grow 10 nm of SiO<sub>2</sub> ("gate oxide") in the bare regions of the Si.

- 8. Deposit 200 nm of poly-Si (by CVD).

- 9. Pattern the poly-Si using the gate mask.

- 10. Use clear-field select mask to pattern photoresist; implant phosphorus. This will form the n+ source and drain junctions for the n-channel MOSFETs.

- 11. Use dark-field select mask to pattern photoresist; implant boron. This will form the p+source and drain junctions for the p-channel MOSFETs.

- 12. Thermally anneal the wafer in order to activate the implanted dopants. The final source/drain junction depth is 100 nm.

- 13. Deposit 0.5 μm of SiO<sub>2</sub> ("passivation oxide").

- 14. Pattern the deposited SiO<sub>2</sub> using the contact mask.

- 15. Deposit 0.5 um of aluminum.

- 16. Pattern the aluminum using the metal mask.

## Problem 7 (continued)

a) Draw cross-section A-A' in the space provided. Identify all layers clearly. [10 pts]

Cross-section A-A'

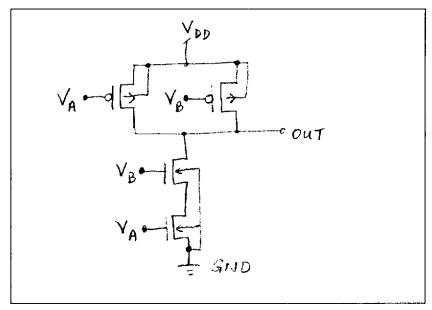

**b)** Draw the circuit schematic, labeling  $V_{DD}$ , GND,  $V_A$ ,  $V_B$ , and OUT. [5 pts]

**Circuit Schematic**

c) Assuming that  $k_n' = 3k_p'$ , would you expect this logic gate to have comparable worst-case "pull-up" and "pull-down" propagation delays? (Is  $t_{pLH} \cong t_{pHL}$ ?) Justify your answer. [5 pts]  $\forall e \le 1$

pull-up:

$$R = R_p \propto \frac{1}{(W/L)_p k_p'}$$

For  $R_p = 2R_n$ ,  $(\frac{W}{L})_p k_p' = (\frac{W}{L})_n k_n'/2$

$= (\frac{W}{L})_n \frac{3k_p'}{2}$

14 =  $\frac{(W/L)_p}{(W/L)_n} = \frac{3}{2}$  which is indeed the case!

### Problem 8: Technology Scaling (Short-Answer Questions) [10 points in total]

a) Explain how transistor scaling improves both the cost (per function) and performance (circuit operating speed) of CMOS integrated circuits. [5 pts]

The circuit layout area and hence the <u>chip area is reduced</u> when the size of the transistor is reduced. Thus, <u>more chips can be fabricated on a single wafer</u>, and the cost per chip is reduced. (Note that the cost of a processing a wafer increases only moderately as technology is advanced.)

The output capacitance (due to drain projunction capacitances, Mosfet gate capacitances, and wiring capacitance) is reduced

-> propagation delay & Contput is reduced,

so logic gates can be operated at higher clock frequencies.

b) Explain why interconnect delay is becoming more of a concern as CMOS technology advances. [5 pts]

The spacing between the wires which interconnect the transistors is scaled down together with the lateral dimensions of the transistors. At the same time, the height of the wires is not being scaled down (in order to minimize the increase in resistance per unit length). Therefore, coupling capacitance per unit length between these wires increases, so that interconnect delay does not scale down as quickly as transistor delay. Thus, interconnect delay is a growing issue, particularly for long wires (used to route "global" signals).