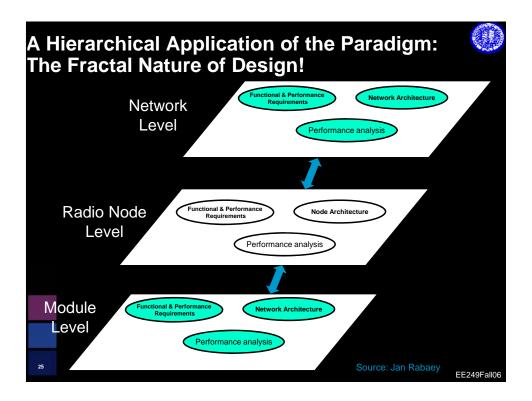

## **Design Flow**

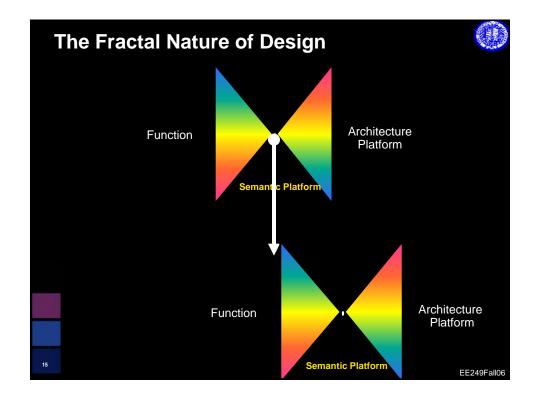

- Theory:

- Initial intent captured with declarative notation

- Map into a set of interconnected component:

- Each component can be declarative or operational

- Interconnect is operational: describes how components interact

- Repeat on each component until implementation is reached

- Choice of model of computations for component and interaction is already a design step!

- Meta-model in Metropolis (operational) and Trace Algebras

(denotational) are used to capture this process and make it rigorous

21

EE249Fall06

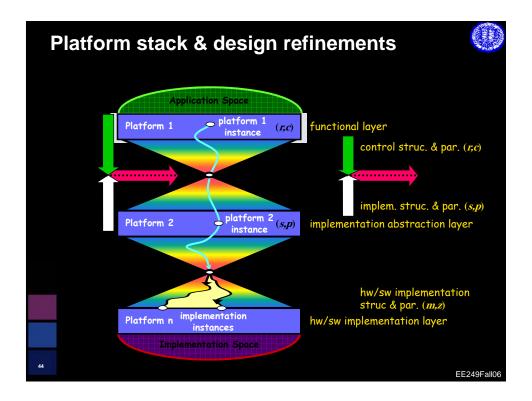

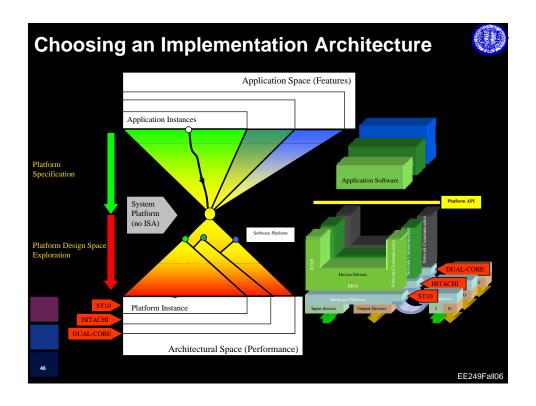

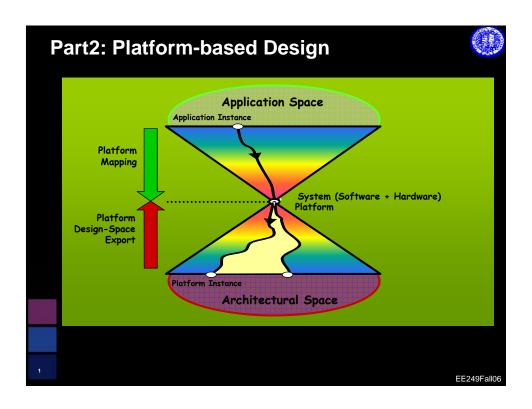

## Consequences

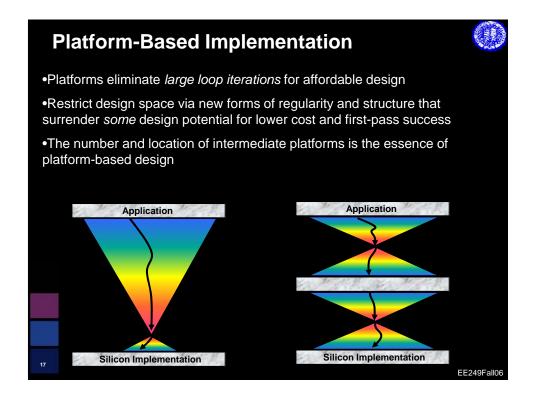

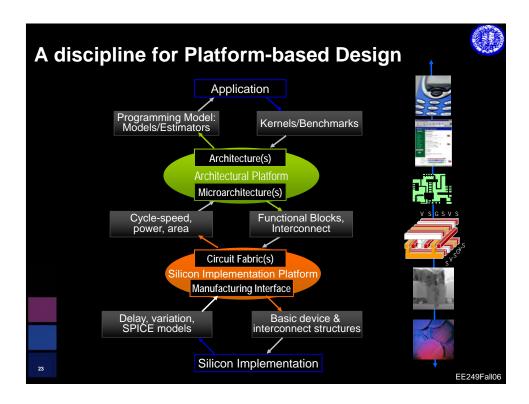

- There is no difference between HW and SW. Decision comes later.

- HW/SW implementation depend on choice of component at the architecture platform level.

- Function/Architecture co-design happens at all levels of abstractions

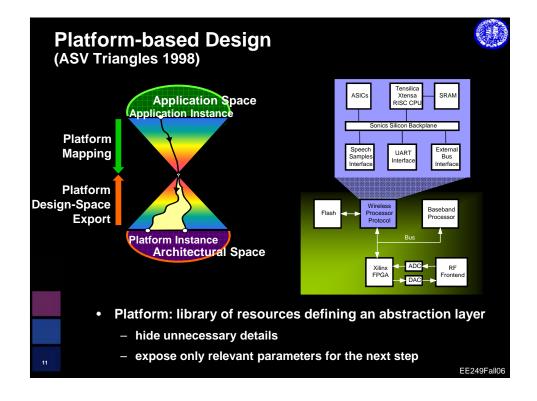

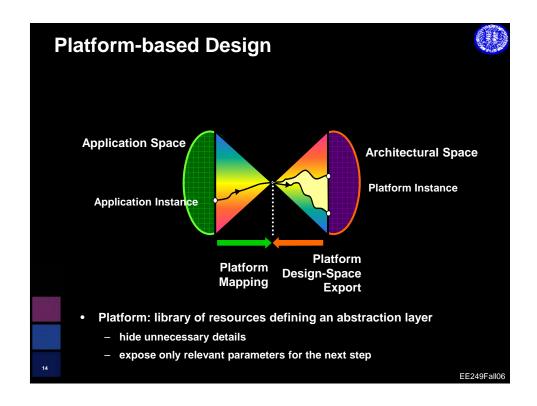

- Each platform is an "architecture" since it is a library of usable components and interconnects. It can be designed independently of a particular behavior.

- Usable components can be considered as "containers", i.e., they can support a set of behaviors.

- Mapping chooses one such behavior. A Platform Instance is a mapped behavior onto a platform.

- A fixed architecture with a programmable processor is a platform in this sense. A processor is indeed a collection of possible bahaviours.

- A SW implementation on a fixed architecture is a platform instance.

EE249Fall06

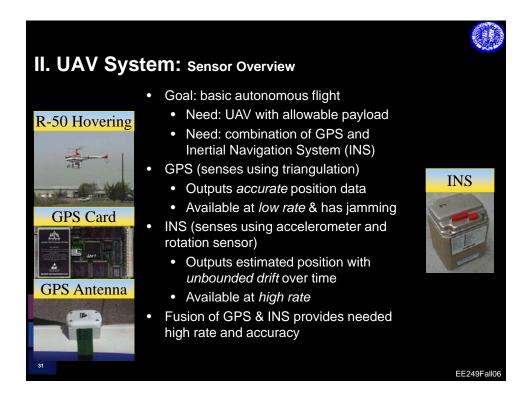

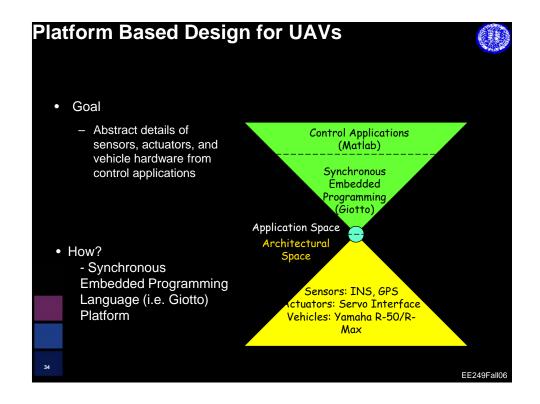

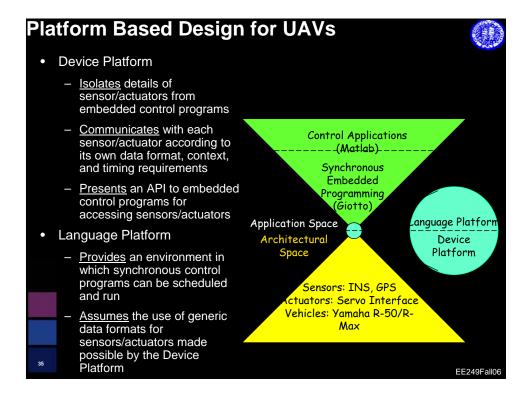

## **III. Synchronous Control** Advantages of time-triggered framework: - Allows for composability and validate - These are important properties for safety critical systems like the **UAV** controller Timing guarantees ensure no jitter Disadvantages: - Bounded delay is introduced - Stale data will be used by the controller - Implementation and system integration become more difficult Platform design allows for time-triggered framework for the UAV controller - Use Giotto as a middleware to ease implementation: - provides real-time guarantees for control blocks - handles all processing resources - Handles all I/O procedures EE249Fall06

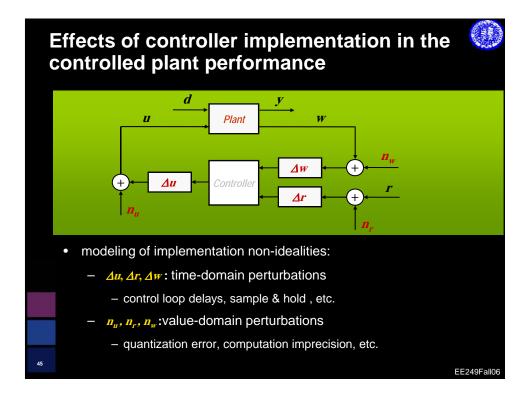

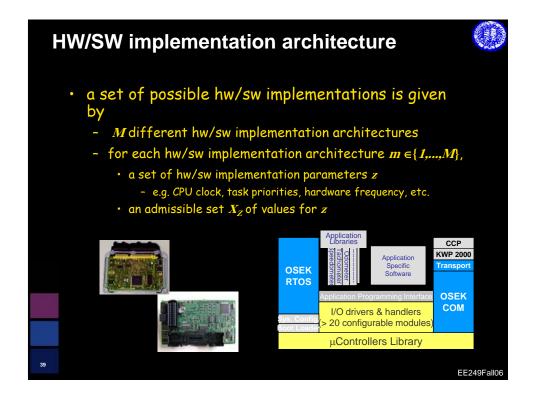

## Implementation abstraction layer we introduce an implementation abstraction layer which exposes ONLY the implementation non-idealities that affect the performance of the controlled plant, e.g. control loop delay quantization error sample and hold error computation imprecision at the implementation abstraction layer, platform instances are described by **S** different implementation architectures for each implementation architecture $s \in \{1,...,S\}$ , a set of implementation parameters p - e.g. latency, quantization interval, computation errors, etc. an admissible set $X_p$ of values for pEE249Fall06