### **Crystallographic Planes**

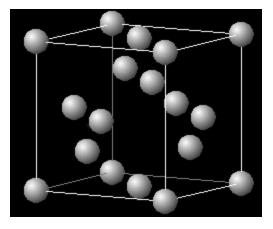

Unit cell:

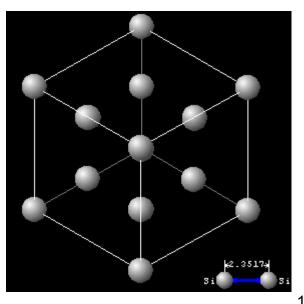

<u>Si lattice constant =</u> 5.431Å

$\rightarrow$  5 x 10<sup>22</sup> atoms/cm<sup>3</sup>

View in <111> direction

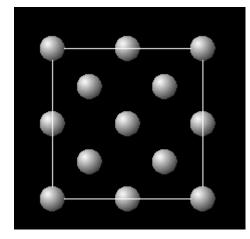

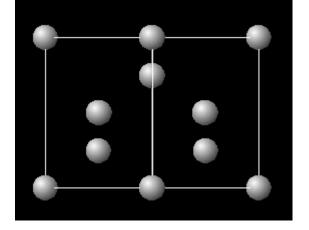

View in <100> direction View in <110> direction

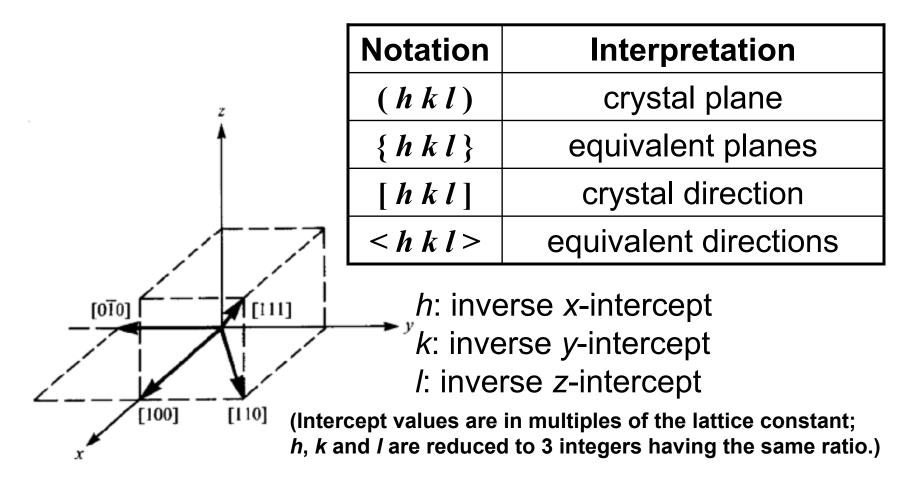

#### Crystallographic Notation Miller Indices

Sample direction vectors and their corresponding Miller indices.

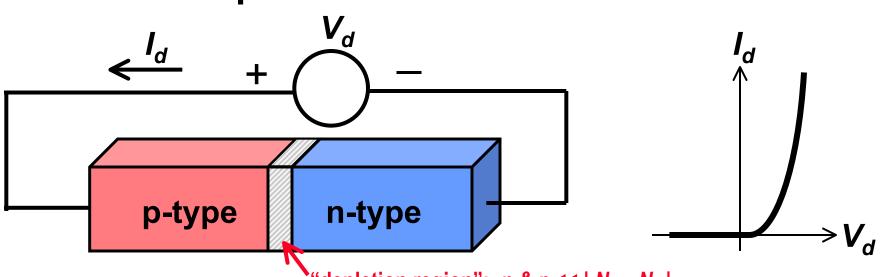

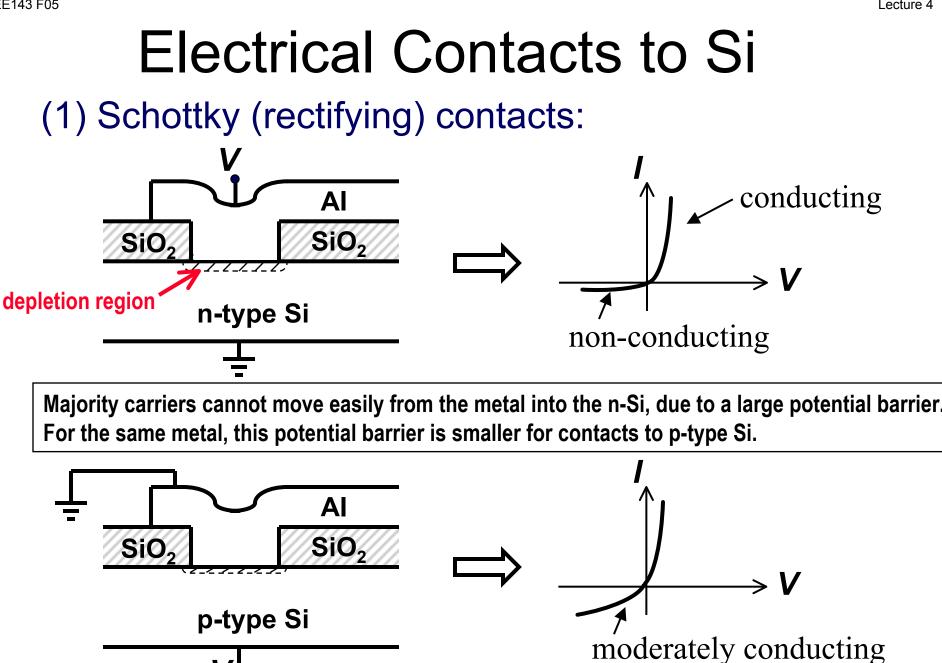

### The pn-Junction Diode

"depletion region": *n* & *p* << | *N<sub>D</sub>* – *N<sub>A</sub>* |

A *rectifying contact* is formed between a p-type region and an n-type region

- Large current can flow in the direction from p to n

- for  $V_d > \sim 0.7$  Volts (Si diode)

- Negligible current flows in the direction from n to p

- But for large negative  $V_d$ , the junction will eventually break down and conduct a large negative current

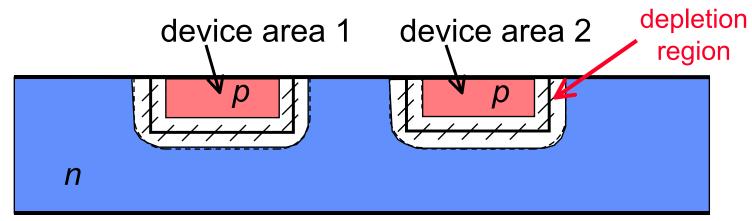

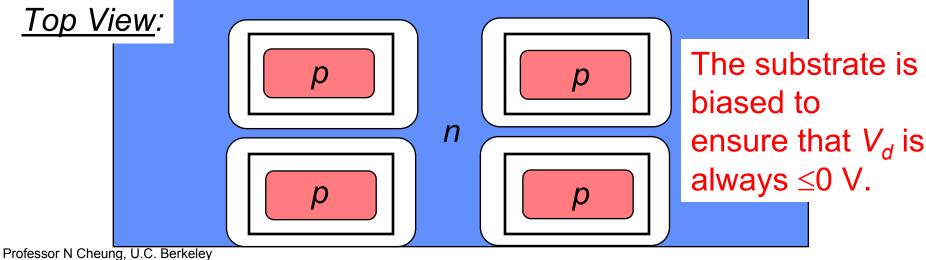

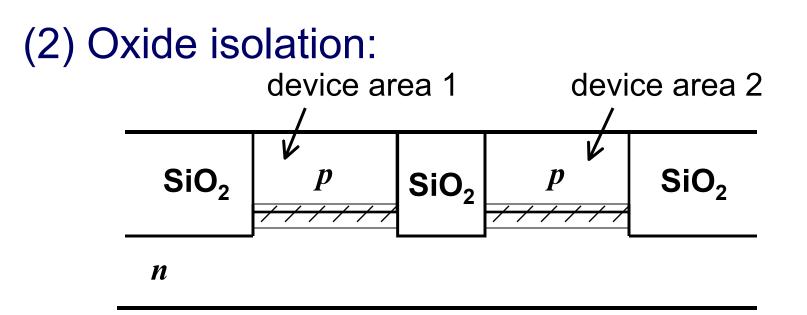

## **Device Isolation Methods**

### (1) pn-junction isolation:

Cross-Sectional View:

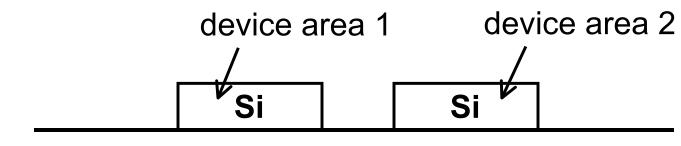

#### (3) Silicon-on-Insulator substrate:

dielectric substrate (e.g.  $SiO_2$ ,  $AI_2O_3$ )

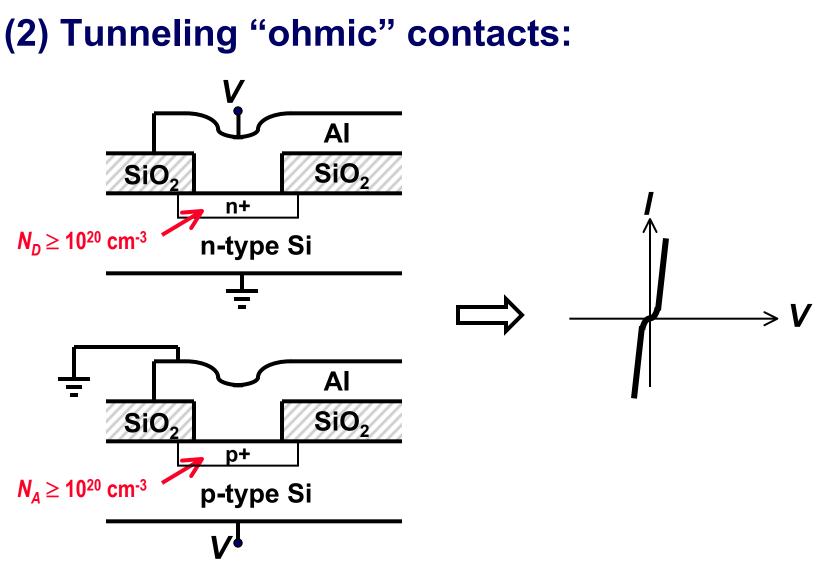

The depth of the depletion region ( $x_d$ ) decreases with increasing dopant concentration. For very high doping,  $x_d$  is small enough (<10nm) to allow quantum tunneling of carriers.

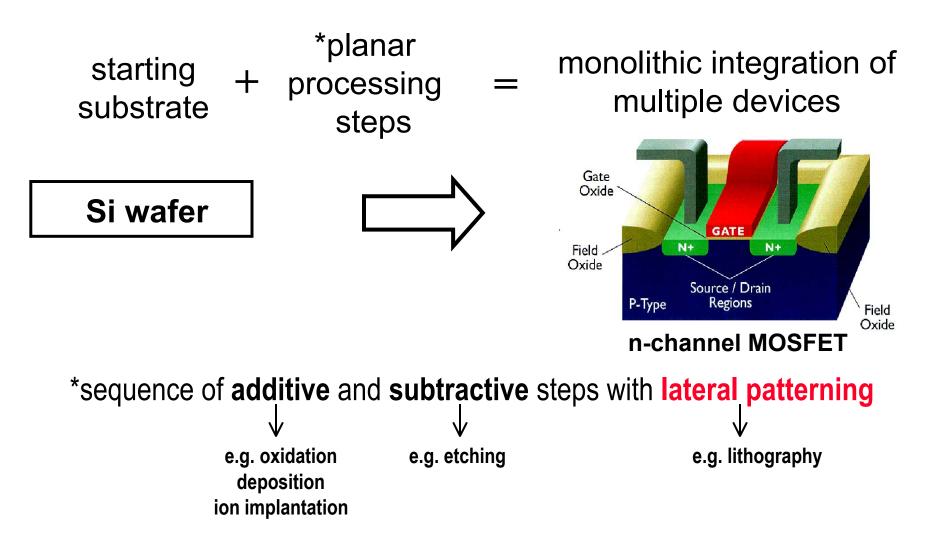

## Planar Technology

#### Suspended Beam Array

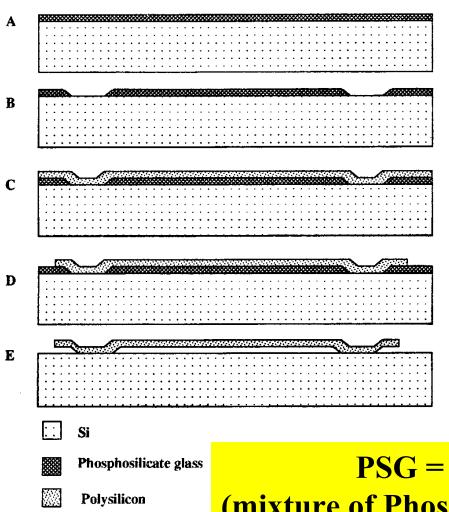

Doped oxide (PSG) deposition (CVD) (blanket addition)

Anchor patterning (litho. & etch) (patterned subtraction)

Poly-Si deposition (blanket addition)

Poly-Si beam patterning (litho. & etch) (patterned subtraction)

Selective etch of PSG (blanket subtraction)

PSG = PhosphoSilicate Glass (mixture of Phosphorus oxide and Silicon Oxide)

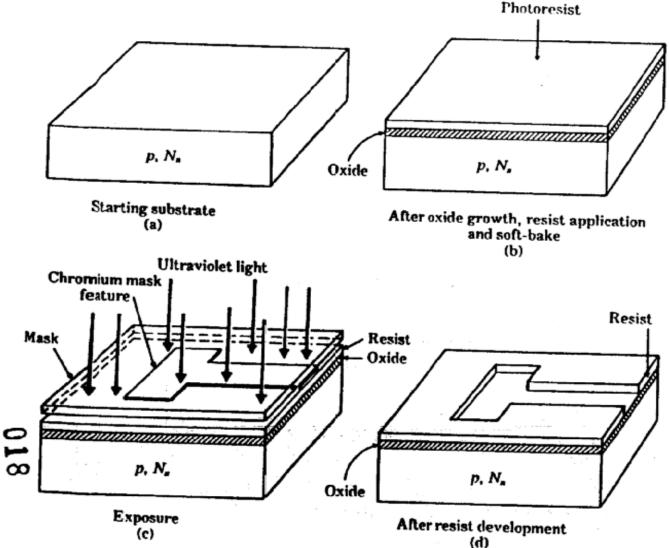

#### Al contact to n+ Si

#### Process Flow Example #2 - cont

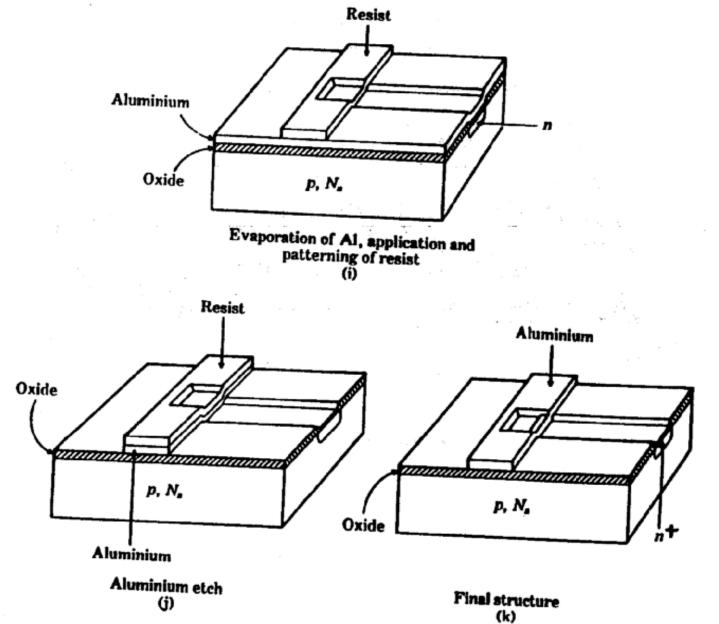

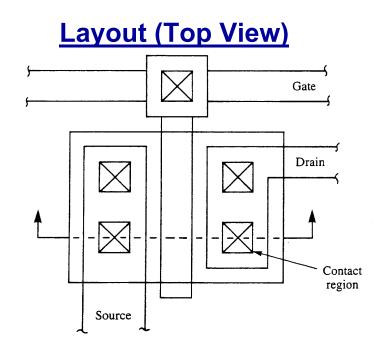

## N-channel MOSFET

p-type substrate

4 lithography steps are required: 1. active area

- 2. gate electrode

- 3. contacts

- 4. metal interconnects

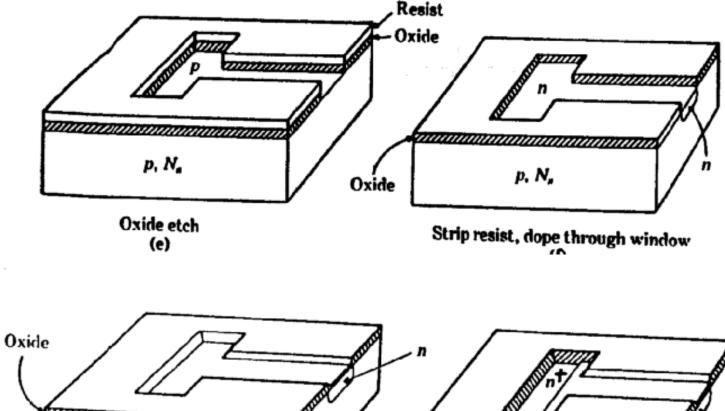

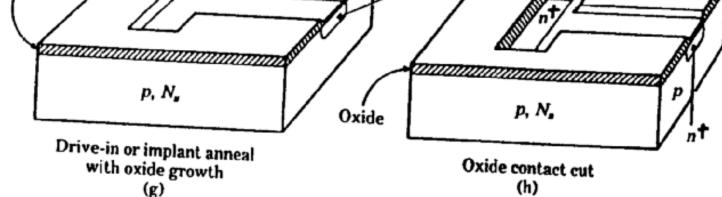

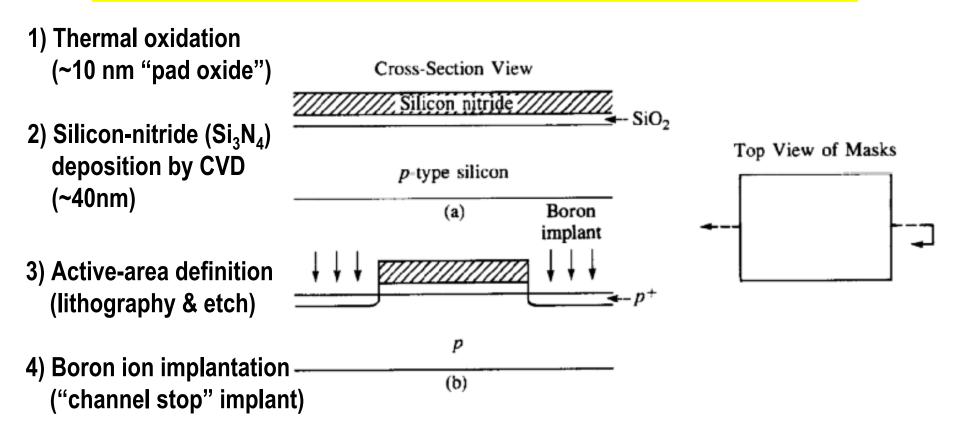

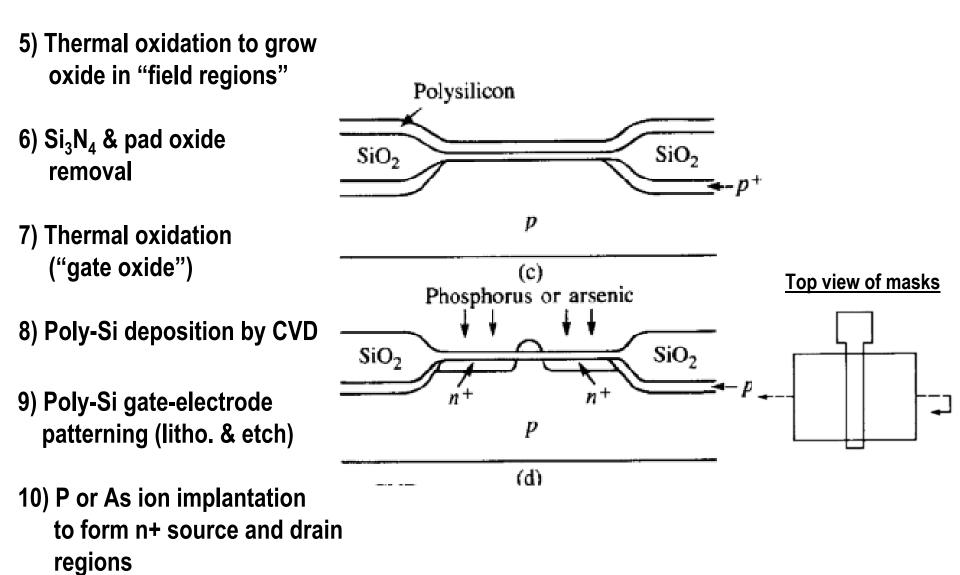

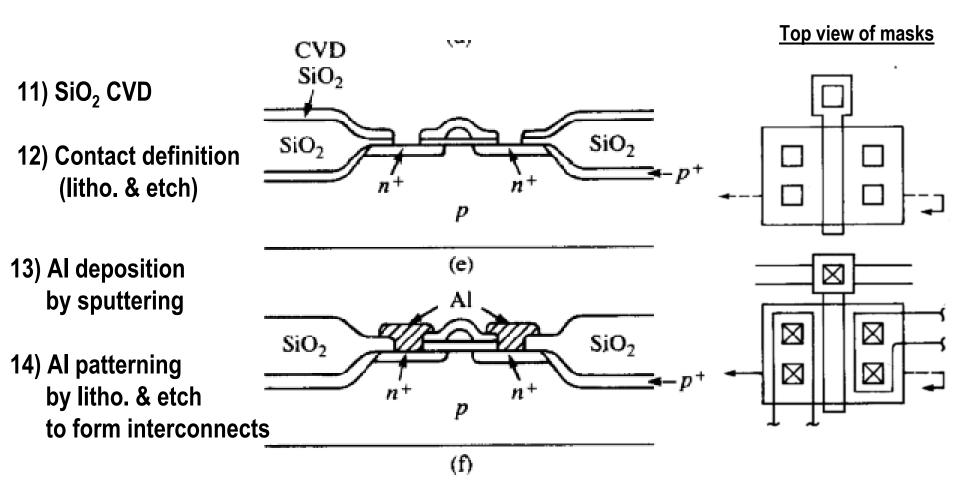

#### Simple nMOSFET Process Flow

**Read Jaeger (textbook)** Chap 1 for narrative description

#### Process Flow Example #3 - cont

#### Process Flow Example #3 cont.

Professor N Cheung, U.C. Berkeley