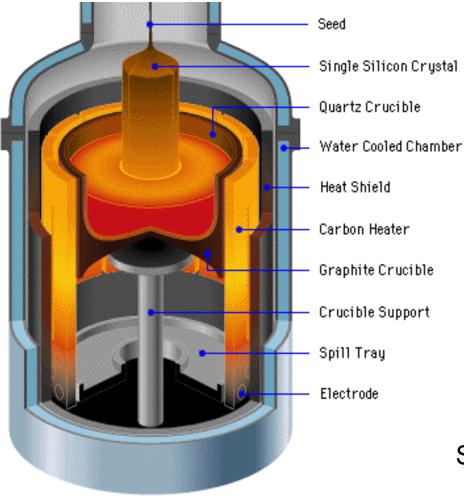

#### Czochralski Crystal Growth Crystal Pulling

#### Crystal Ingots

#### Shaping and Polishing

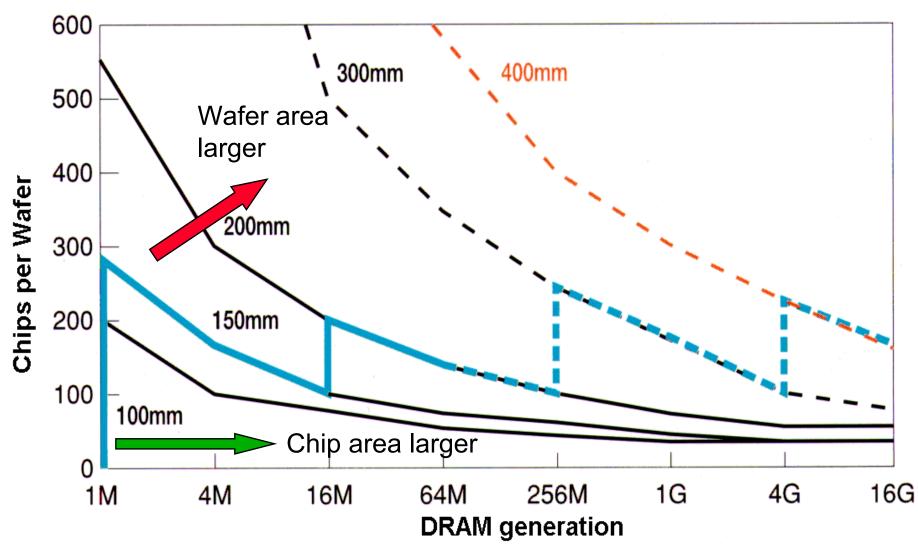

300 mm wafer

#### Advantage of larger diameter wafers

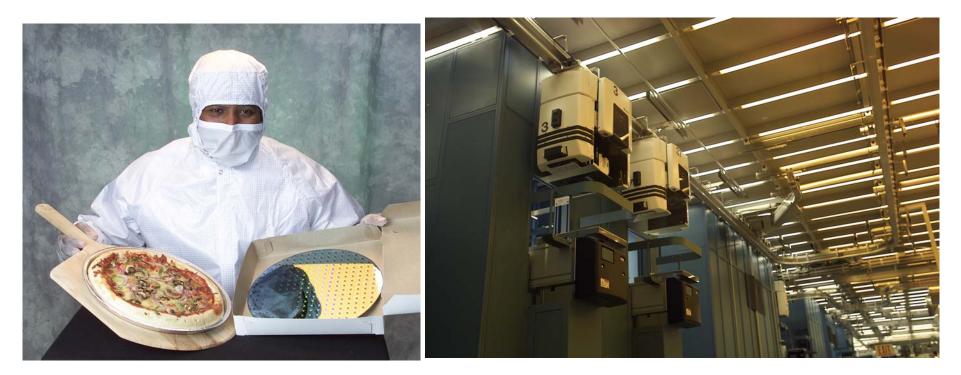

# Large-Diameter Wafer HandlingLa Vals FabProduction Fab

300mm wafer vs pizza

Overhead rail transport of wafer cassette

•Lateral uniformity of processing effects across the WHOLE wafer is key consideration for microfabrication design

#### EE143 F05

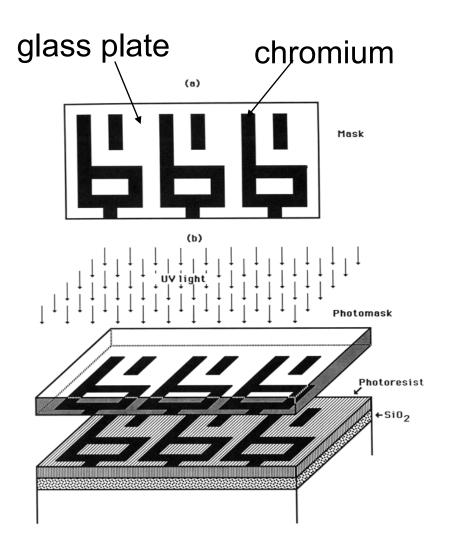

### Photolithography

#### **Positive Resist**

Part exposed to light will be dissolved in development solution.

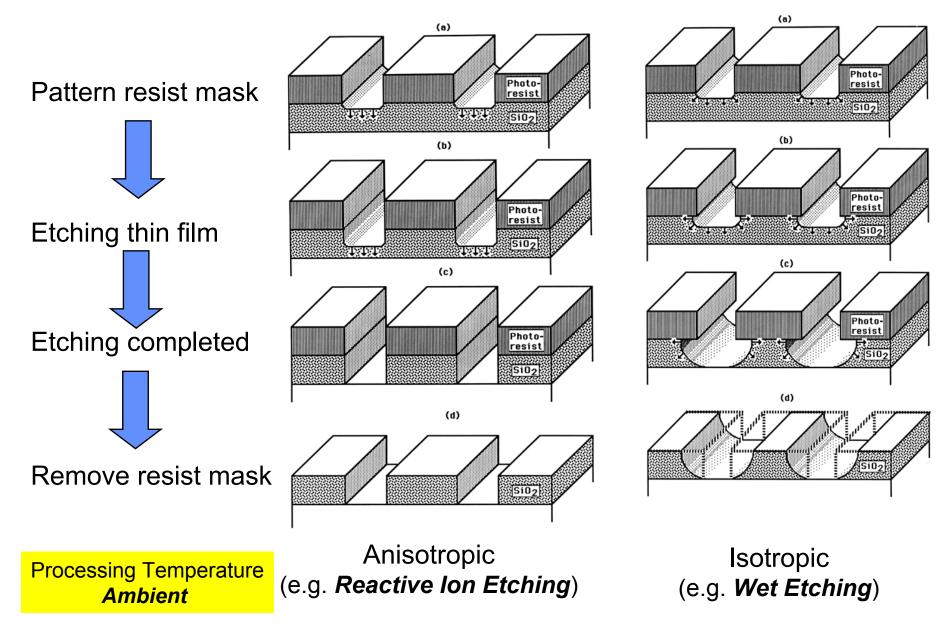

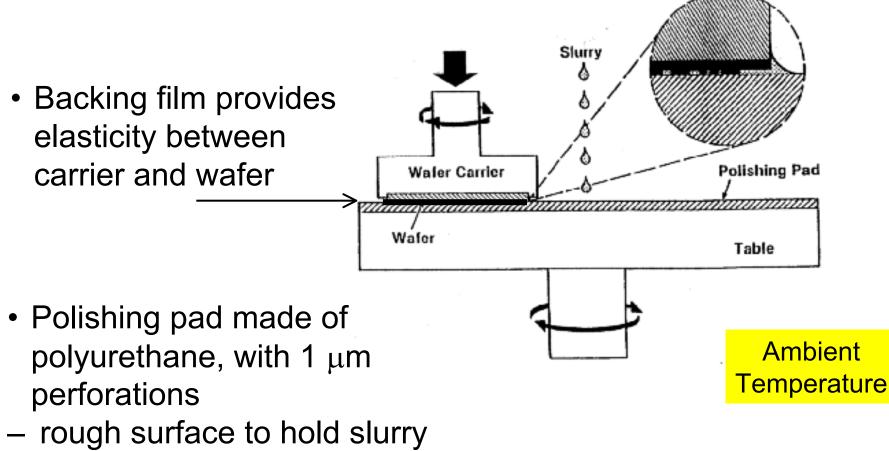

Processing Temperature Ambient

### Etching

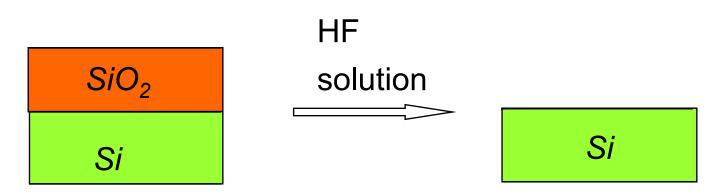

#### **Etching Selectivity**

#### Example: HF solution etches SiO<sub>2</sub> but not Si

#### \* A high etching selectivity is usually desired

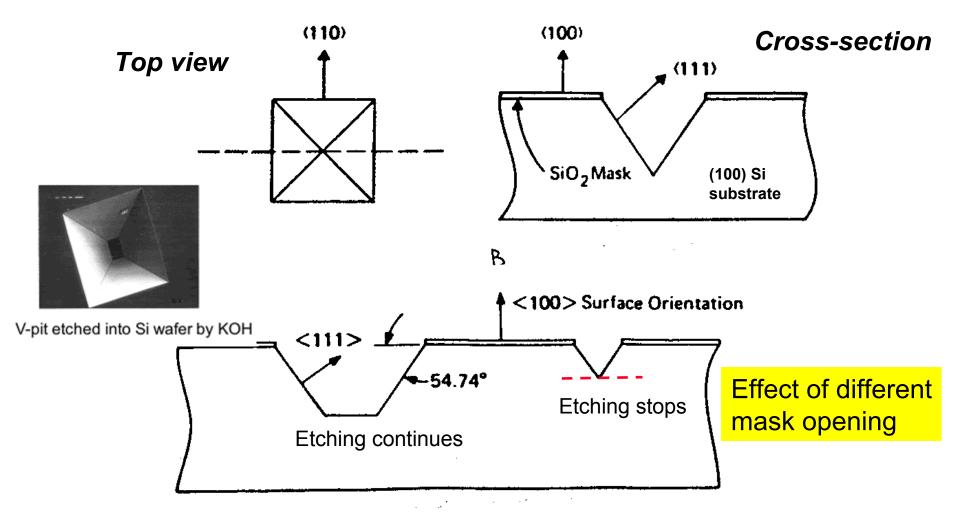

#### "Anisotropic " Wet Etching of Si Crystals

#### Etchants : KOH or EDP (Ethylene-Diamine\_Pyrocatechol)

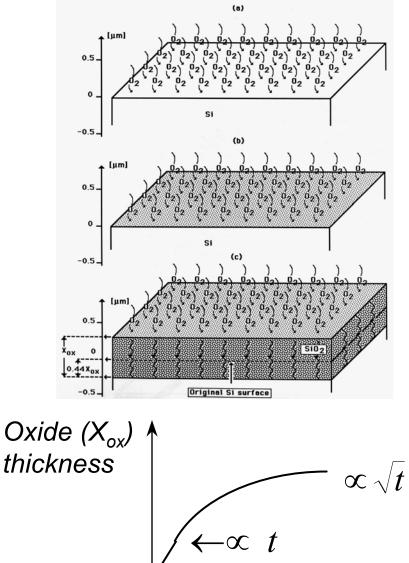

### **Thermal Oxidation**

Processing Temperature 900-1100 °C

- $Si + O_2 \rightarrow SiO_2$

- Si + 2  $H_2O \rightarrow SiO_2 + 2H_2$

- $O_2$  (or  $H_2O$ ) diffuses through SiO<sub>2</sub> and reacts with Si at the interface to form more SiO<sub>2</sub>.

- 1μm of SiO<sub>2</sub> formed consumes

0.44 μm of Si substrate.

- Thin oxide growth (e.g. gate oxide)

use O<sub>2</sub>. Dry oxidation

- Thick oxide growth (e.g. field oxide) - use H<sub>2</sub>O. Wet oxidation

•Oxidation time(t)

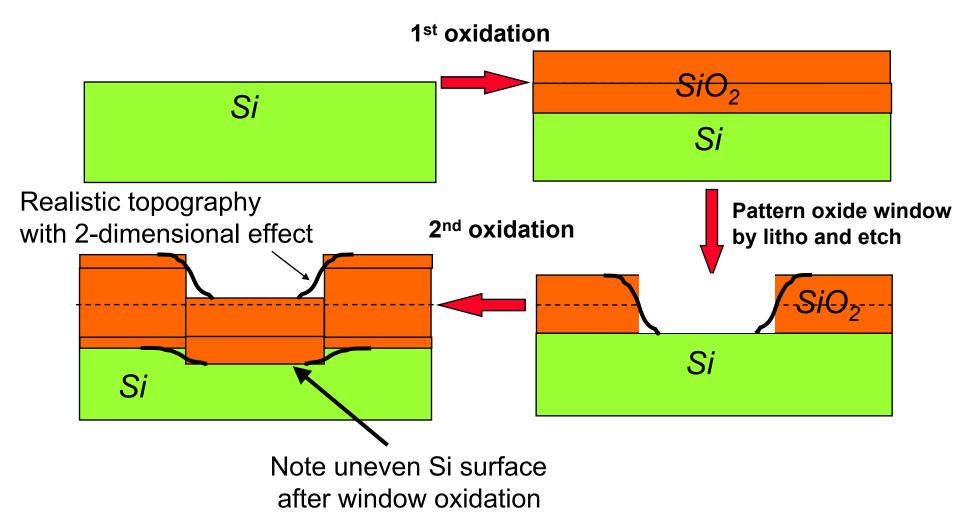

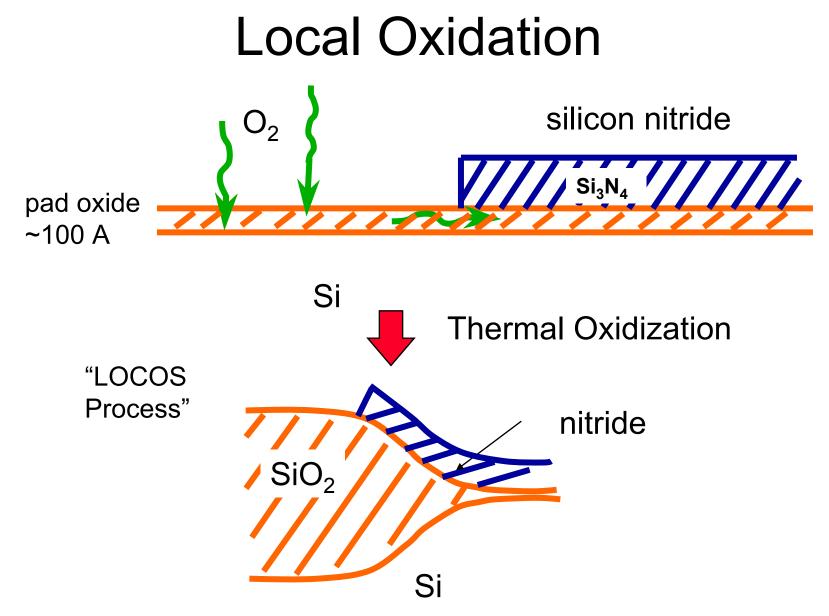

## Uneven surface topography with window oxidation

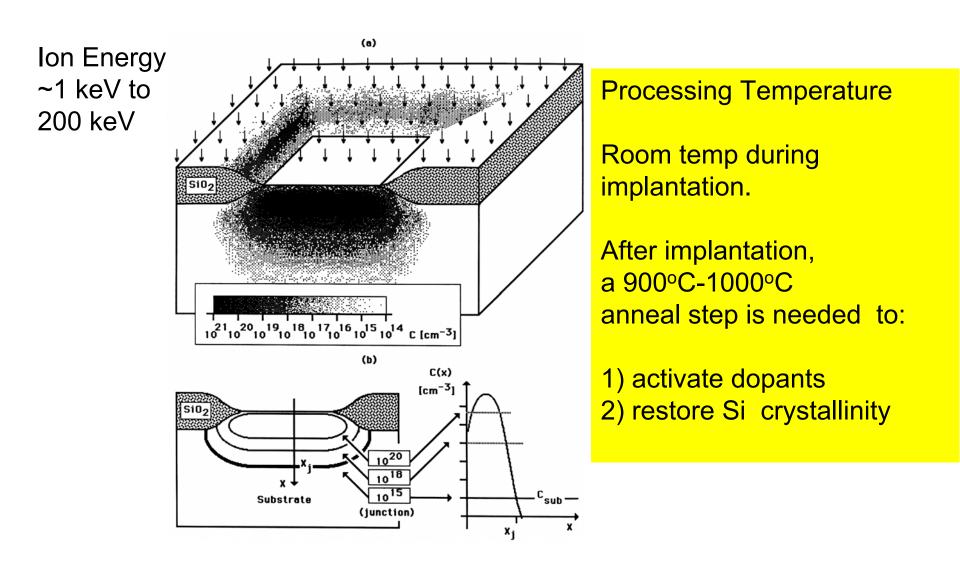

### Ion Implantation

typically used to introduce dopans into semiconductors

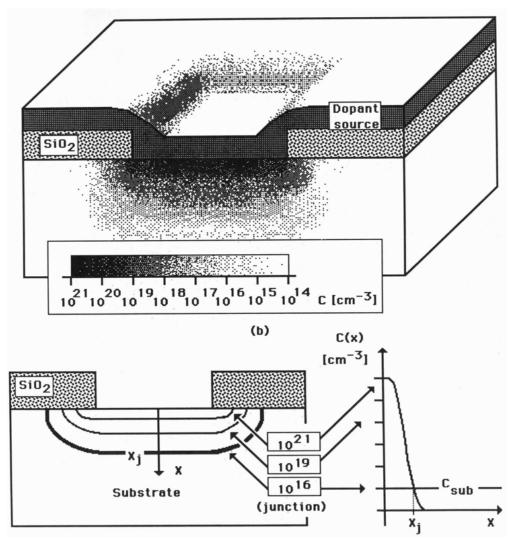

#### Diffusion

- To introduce dopants into semiconductors [Predeposition]

- To spread out the dopant profile [ Drive-in]

$D = D_0 \cdot e^{-Q_{kT}}$   $D = Diffusion \ Constant$   $Q = Activation \ Energy$  $T = Temp \ in \ K (D \uparrow as \ T \uparrow)$

Processing Temperature 950-1200 °C

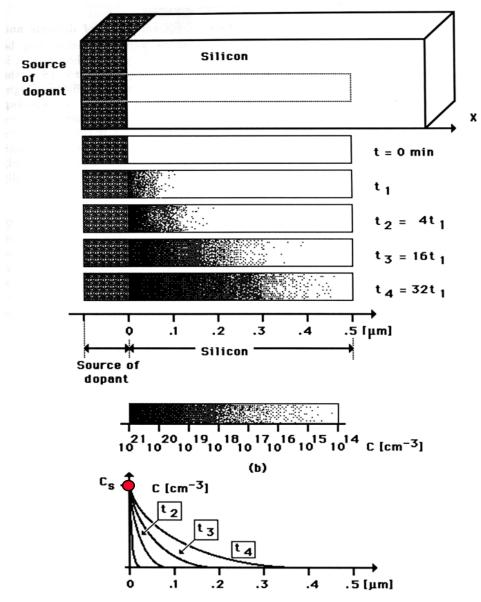

### Predeposition

- Si surface concentration maintained at constant  $C_s$  (solid-solubility) during predep.

- Dose of dopant incorporation

$$= \frac{C_s \cdot 2\sqrt{Dt}}{\sqrt{\pi}}$$

Professor N Cheung, U.C. Berkeley

EE143 F05

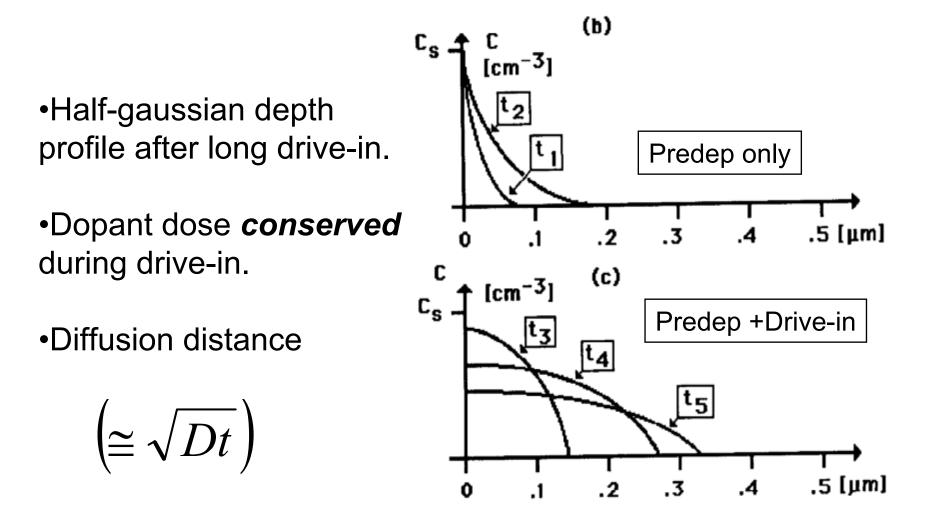

#### Predeposition and Drive-in

**Concentration versus Depth**

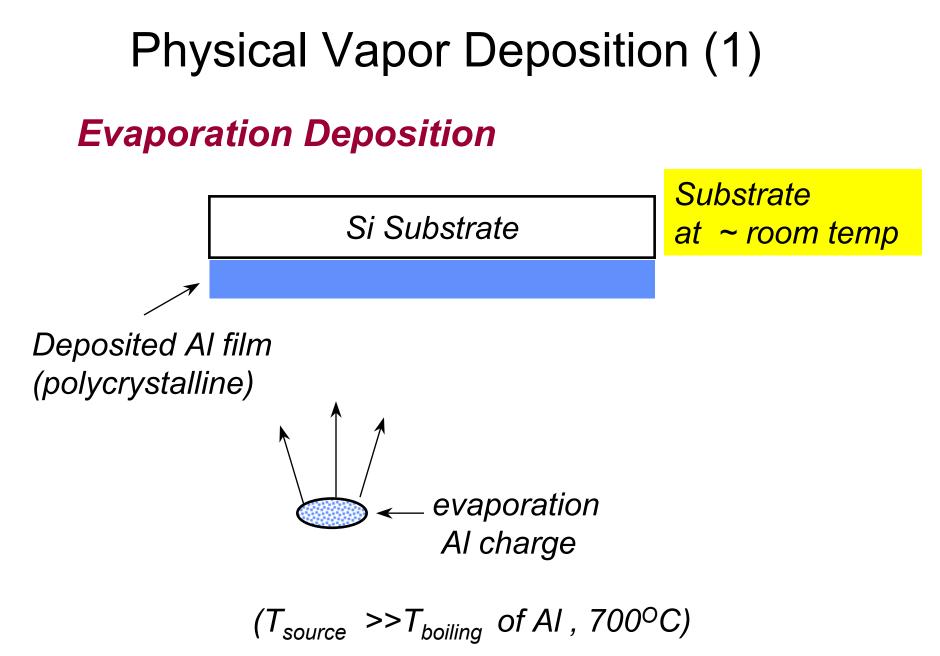

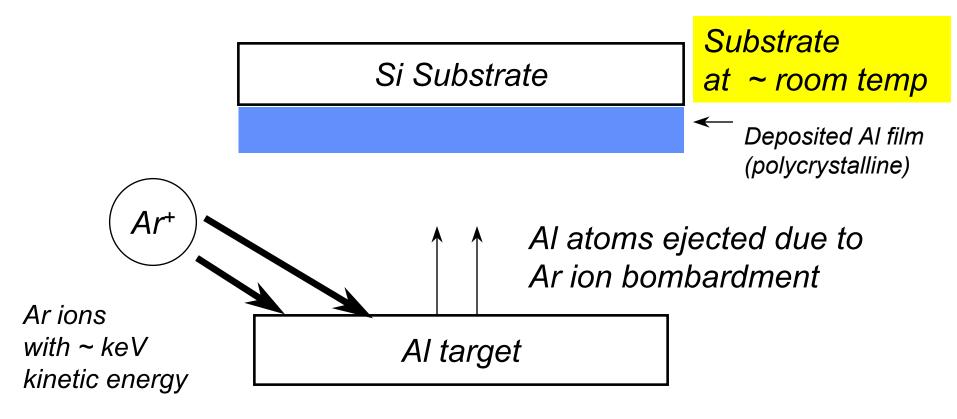

### Physical Vapor Deposition (2)

#### **Sputtering Deposition**

## CVD, eg. of Si<sub>3</sub>N<sub>4</sub> Processing Temperature 300-600°C SiCl<sub>2</sub>H<sub>2</sub>(v) + NH<sub>3</sub>(v) $\longrightarrow$ Si<sub>3</sub>N<sub>4</sub> + effluent(v) $intermediate Si_3N_4$ film

Si Substrate Substrate holder (hot)

Solid films are formed by chemical reactions taking place at the surface.

EE143 F05

Lecture 2

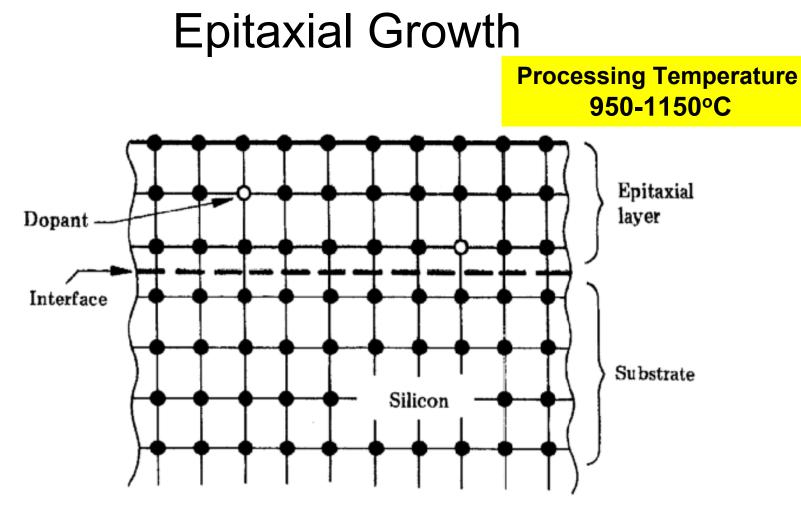

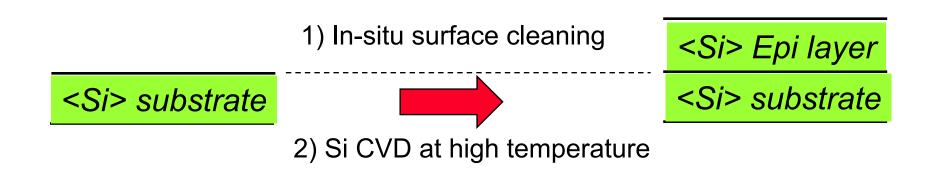

- Requires an ultra-clean Si surface prior to epi growth.

- Requires deposition of Si at very high temperature for perfect crystallinity.

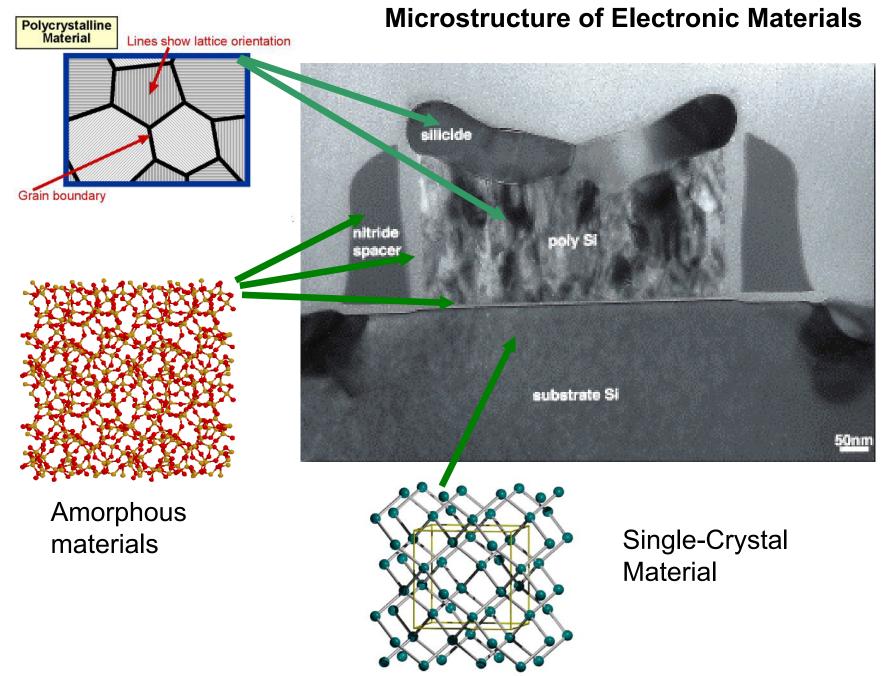

### **Epitaxial Growth**

Typically used when we need a lightly doped singlecrystal Si layer on top of heavily doped substrate.

Example

$$n^-$$

$10^{15}/cm^3$

$n^+  e.g. 10^{20}/cm^3$

$10^{15}/cm^3$

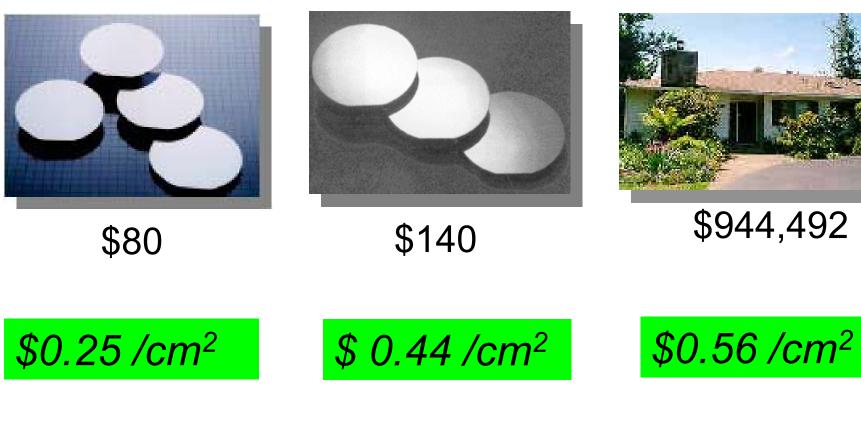

### Cost of Silicon Real Estate

200mm Si wafer

200mm Epi wafer

1812 sq/ft House Menlo Park, CA

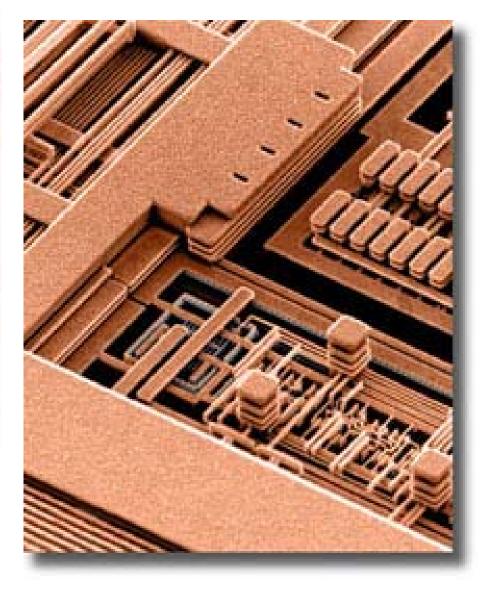

### Chemical Mechanical Polishing (CMP)

Wafer is polished using a slurry containing

- silica abrasives (10-90 nm particle size)

- etching agents (e.g. dilute HF)

EE143 F05

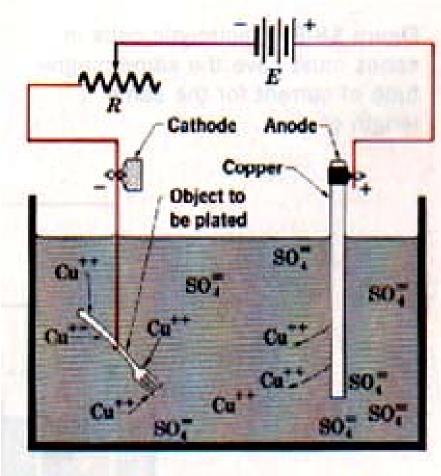

#### **Metal Plating**

Figure 18-7. An electrolytic cell used for copper plating.

~ ambient temp

#### List of Conventional Microfabrication Modules

- Lithography

- Thermal Oxidation

- Etching (Chemical, Plasma)

- Ion Implantation

- Diffusion

- Physical Vapor Deposition PVD

- Chemical Vapor Deposition CVD and Epitaxial Growth

- Chemical Mechanical Polishing CMP

- Metal Plating

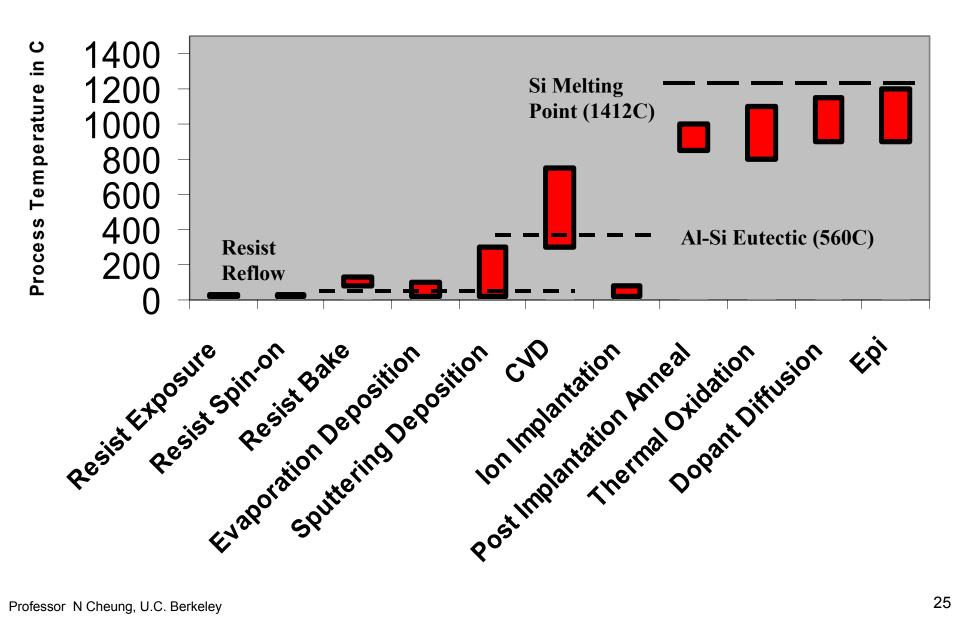

#### Processing Temperature and Material Failure Temperature

### Interesting Facts about Chip Manufacturing

- A typical 2-gram silicon chip requires 1.6 kilograms of fossil fuel, 72 grams of chemicals and 32 kilograms of water to manufacture.

- To make the high-grade silicon needed for the chips requires 160 times the energy used to produce raw silicon. This accounts for about half of the total energy used by the chip. Only a quarter is consumed during its processing life.

- Because a chip's components are so tiny and precisely engineered, far more materials, such as fuels and solvents, are needed for their manufacture than for more traditional goods.

- The mass of these secondary materials outweighs the product by a factor of 600. In contrast, making a typical car requires only about twice its weight in fossil fuels.

Williams, E. D., Ayres, R. U. & Heller, M. The 1-7 kilogram microchip: energy and material use in the production of semiconductor devices. *Environmental Science and Technology*, Published online (2002).