#### EE105 Microelectronic Devices and Circuits: MOSFET

Prof. Ming C. Wu

wu@eecs.berkeley.edu

511 Sutardja Dai Hall (SDH)

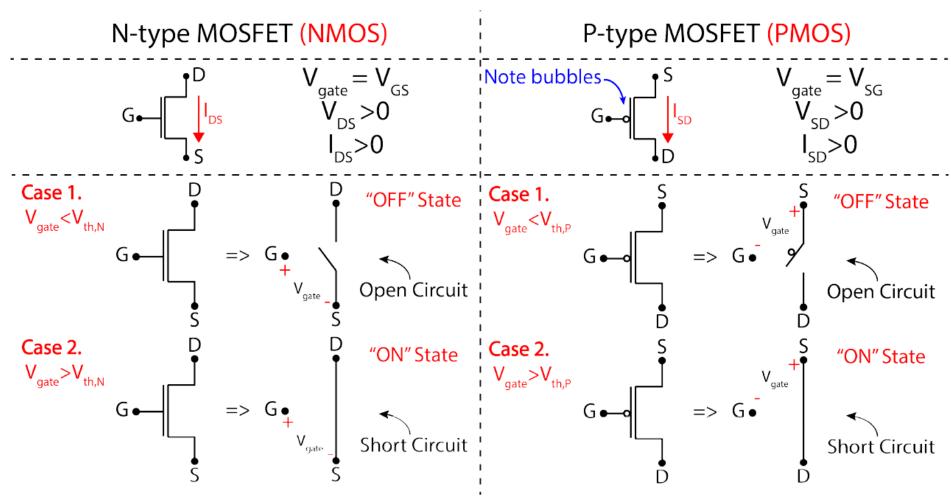

# Simplest Model of MOSFET (from EE16B)

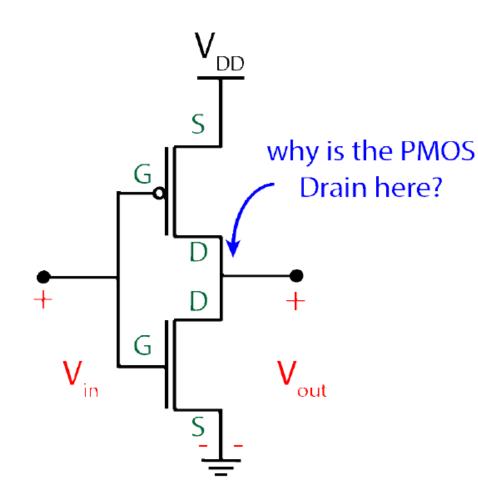

#### **CMOS Inverter**

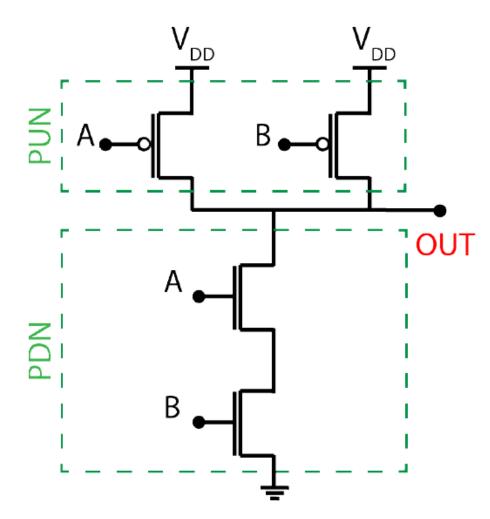

#### **CMOS NAND Gate**

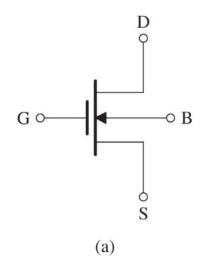

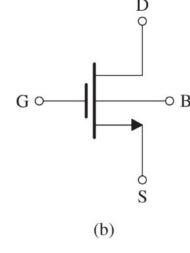

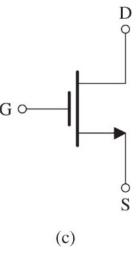

## **More Circuit Symbol for NMOS**

4 terminal including Body (Arrow pointing to channel indicating substrate is p-type) Modified circuit symbol with arrow on source (Arrow indicating direction of current flow) Simplified circuit symbol with body connected to source (or when the effect of the body on device operation is unimportant)

Note in NMOS

- 1. Drain voltage is always more positive than Source voltage

- 2. Current always flows from Drain to Source

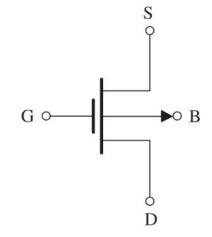

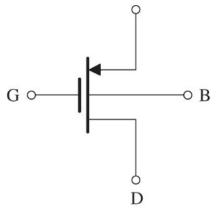

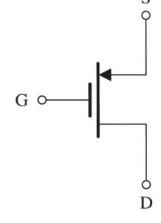

#### **More Circuit Symbol of PMOS**

4 terminal including Body (Arrow pointing away from channel indicating substrate is n-type)

Modified circuit symbol with arrow on source (Arrow indicating direction of current flow)

Simplified circuit symbol with body connected to source (or when the effect of the body on device operation is unimportant)

#### Note in PMOS

- 1. Source voltage is always more positive than Drain voltage

- 2. Current always flows from Source to Drain

- 3. Source is usually drawn on top so current flows downward (convention)

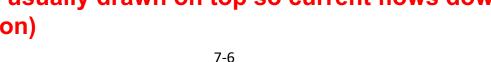

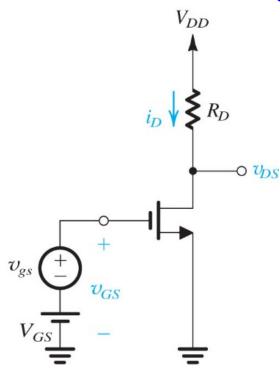

#### **Analog Voltage Amplifier**

UDS

- DC bias at Quiescent (Q) point

- Small-signal input superimposed on a DC bias voltage

- Symbol used in this course:

$$v_{GS} = V_{GS} + v_{gs}$$

Need to know the transistor's I-V characteristics to find the voltage gain (and other properties of the amplifier)

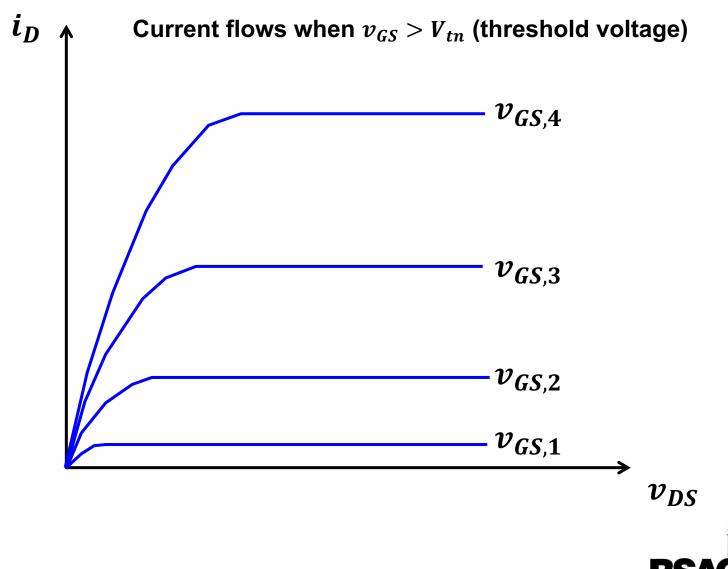

### I-V Curves of NMOS (for fixed Gate Voltage)

#### **Drain Current vs Gate Voltage**

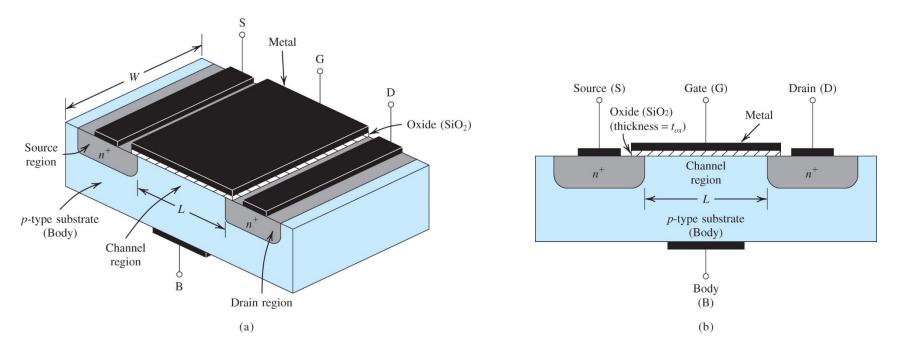

#### **MOSFET Device Structure**

- MOSFET: metal-oxide-semiconductor field effect transistor

- Typically

- Channel length: L ~ < 10 nm to 0.35  $\mu$ m,

- Channel width: W ~ 0.05  $\mu$ m to 100  $\mu$ m,

- Oxide thickness:  $t_{ox} \sim 1$  to 10 nm

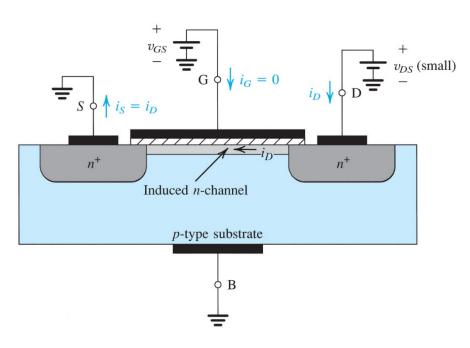

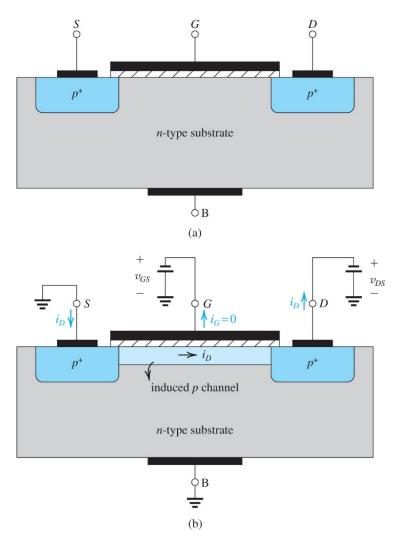

# **NMOSFET (or simply NMOS)**

- N-channel MOSFET

- Current conducted by electrons

- 3 terminal device

- Source (S): n+ (heavily n-type)

- Drain (D): n+

- Gate (G): metal deposited on insulator above channel

- Substrate (called "Body") is a 4<sup>th</sup> terminal

- Substrate is p-doped

- Electrons is induced in channel when a positive gate voltage is applied

- Electrons moves from Source to Drain

- Current flows from D to S

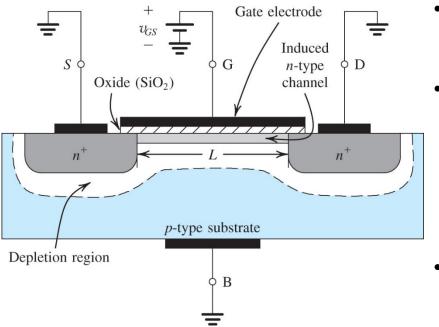

#### **Creating a "Channel" for Current Flow**

MOS is a capacitor across an insulator (oxide) When a positive voltage is applied at Gate, electrons are induced under the gate.

At "thresold", sufficient number of electrons form a "channel" between Source and Drain, forming a conductive channel.

Total charge in the channel:

$$\left|Q\right| = C_{ox} \cdot WL \cdot \left(v_{GS} - V_t\right)$$

where  $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$  is oxide capacitance per unit area  $\varepsilon_{ox} = 3.9\varepsilon_0 = 3.9 \times 8.854 \times 10^{-12}$  F/m W: gate width L: gate length  $V_t$ : Threshold voltage  $v_{GS} - V_t = v_{OV}$  is called "Overdrive Voltage"

#### **Large-Signal Model**

# (usually used to solve DC bias voltage and current)

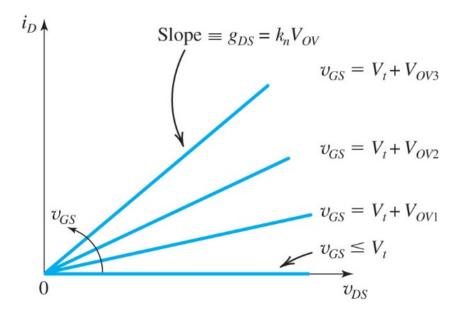

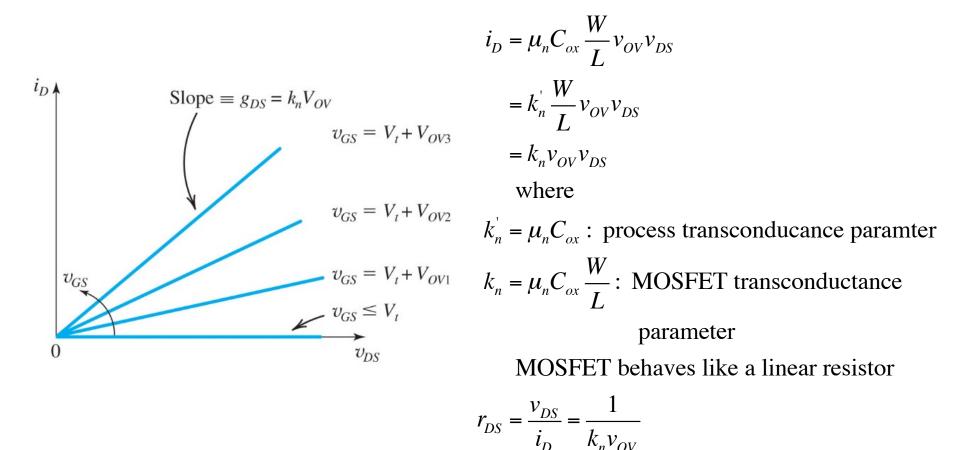

## **Current at Small v**<sub>DS</sub>

When  $v_{OV} = v_{GS} - V_t > 0$ , a channel is formed between Source and Drain.

Linear charge density in channel:

$$\frac{|Q|}{L} = C_{ox} W \cdot v_{OV}$$

Electric field along the channel

$$\left|E\right| = \frac{v_{DS}}{L}$$

Drain current = charge density x velocity:

$$i_{D} = \frac{|Q|}{L} v_{n} = \frac{|Q|}{L} \mu_{n} |E| = C_{ox} W \cdot v_{OV} \mu_{n} \frac{v_{DS}}{L}$$

$$i_{D} = \mu_{n} C_{ox} \frac{W}{L} v_{OV} v_{DS}$$

At small  $v_{DS}$ , the transistor is like a gate-controlled variable resistor

#### **Current at Small v**<sub>DS</sub>

Resistance value can be changed

by gate voltage (overdrive voltage)

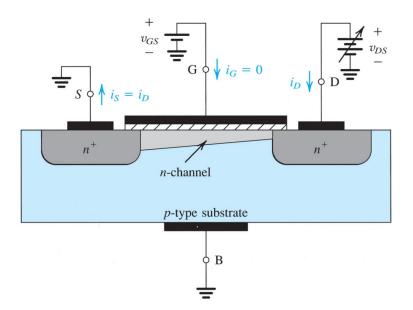

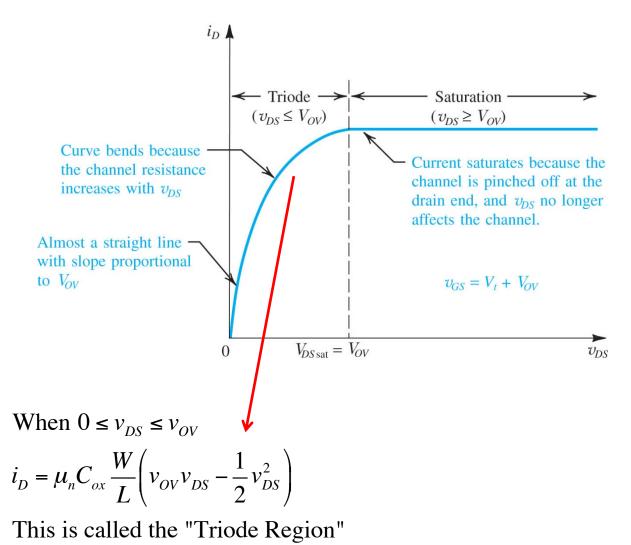

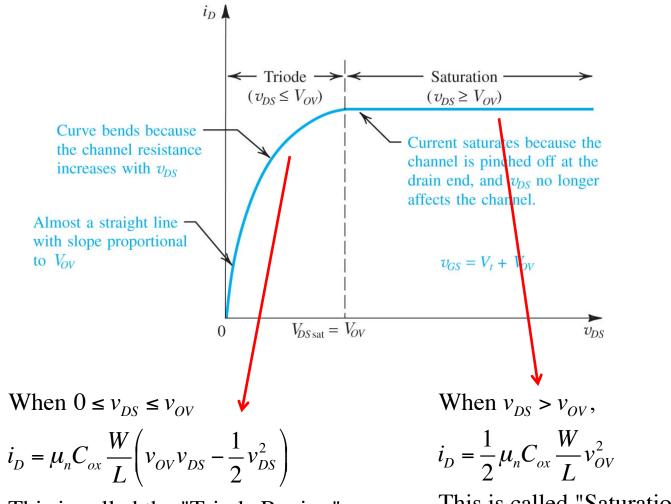

# **Triode Region (v**<sub>DS</sub> < v<sub>OV</sub>)

As  $v_{DS}$  increases, the potential in the channel is no longer a constant. Assume the channel is v(x):

$$i_D = C_{ox} W \left( v_{GS} - v(x) - V_t \right) v_n(x)$$

$$v_n(x) = \mu_n \left| E(x) \right| = \mu_n \frac{dv(x)}{dx}$$

Note:  $i_D$  is still constant along the channel (think Kirchhoff's Current Law) Integrate along the channel x=L x=L/(x) dy(x)

$$\int_{x=0}^{x=L} i_D dx = \int_{x=0}^{x=L} \left( C_{ox} W \left( v_{GS} - v(x) - V_t \right) \mu_n \frac{dv(x)}{dx} \right) dx$$

Change of variable on right-hand side:  $x \rightarrow v$

$$i_D L = \int_{v=0}^{v=v_{DS}} \left( C_{ox} W \left( v_{OV} - v \right) \mu_n \right) dv$$

$$i_D = \mu_n C_{ox} \frac{W}{L} \left( v_{OV} v_{DS} - \frac{1}{2} v_{DS}^2 \right)$$

# **Triode Region (v**<sub>DS</sub> < v<sub>OV</sub>)

Cal

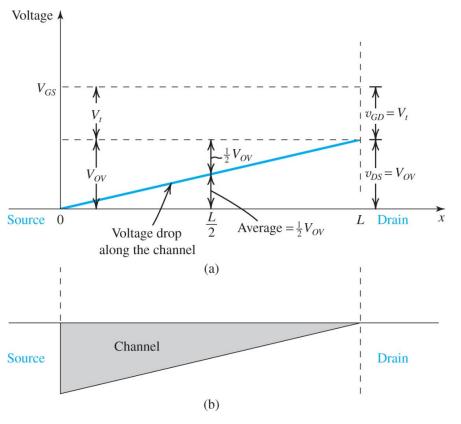

### **Pinch-Off**

The channel potential at the drain side is  $v_{DS}$ . When  $v_{DS} = v_{OV}$ , the local charge density there  $\frac{|Q|}{\text{area}} = C_{ox} (v_{GS} - v_{DS} - V_t) = C_{ox} (v_{OV} - v_{DS}) = 0$ So the channel is "pinched off" near the Drain. Once the channel is pinched off, the drain current remains constant:

$$i_D = \frac{1}{2}\mu_n C_{ox} \frac{W}{L} v_{OV}^2$$

This region,  $v_{DS} > v_{OV}$ , is called "Saturation"

# **Saturation Region (v**<sub>DS</sub> > v<sub>OV</sub>)

This is called the "Triode Region"

This is called "Saturation Region"

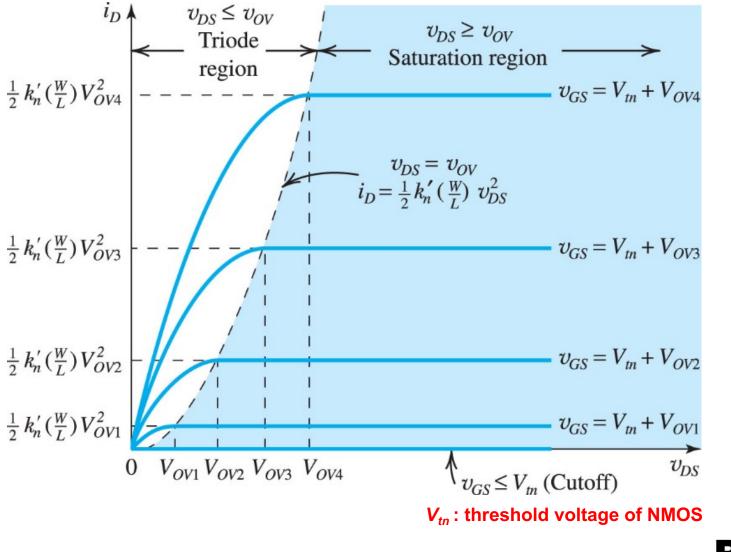

#### **Full I-V Curves of NMOSFET**

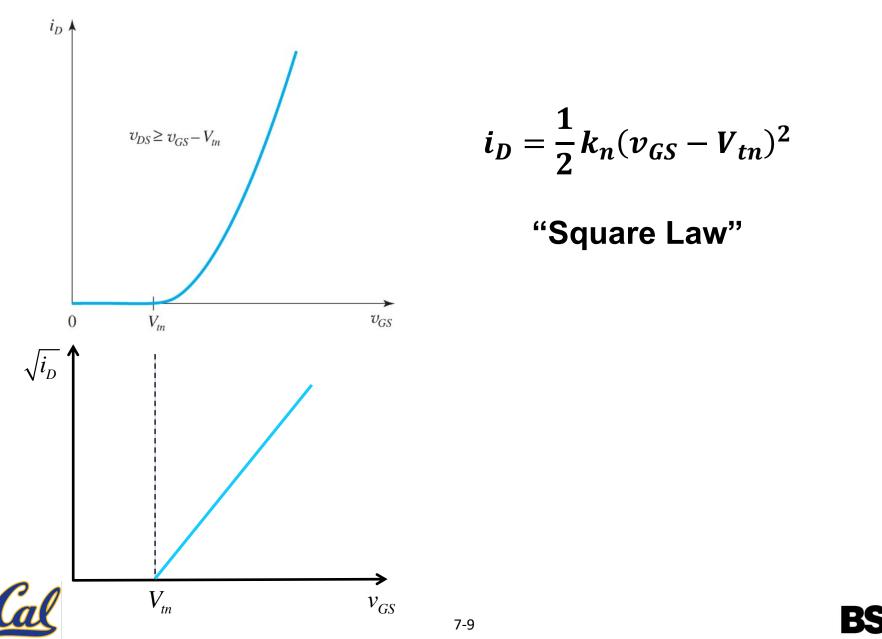

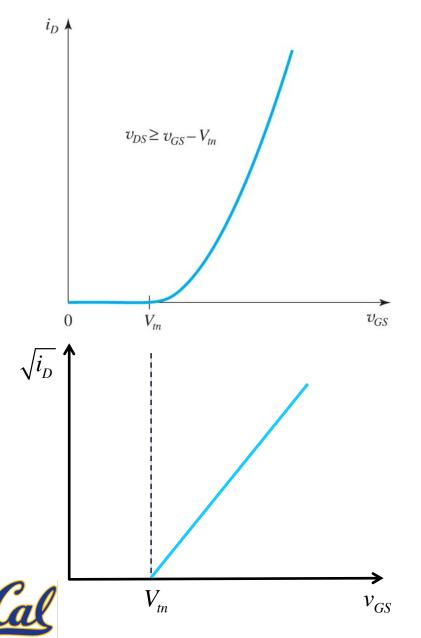

#### **Drain Current vs Gate Voltage**

In Saturation Region

$$i_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} v_{OV}^2$$

$$= \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (v_{GS} - V_{tn})^2$$

To experimentally determine  $V_{tn}$ : Measure and plot  $\sqrt{i_D}$  versus  $v_{GS}$  $\sqrt{i_D} = \sqrt{\frac{1}{2}\mu_n C_{ox}\frac{W}{L}} (v_{GS} - V_{tn})$  $V_{tn}$  = intercept with horizontal axis

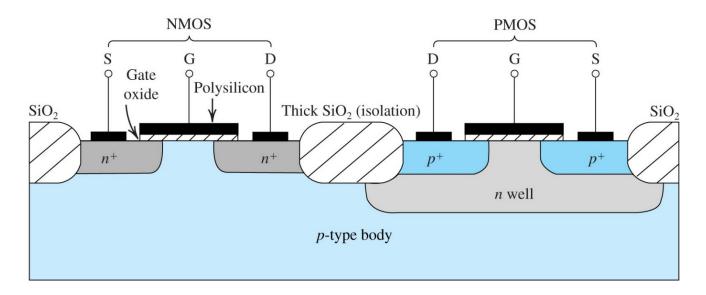

# **PMOSFET (or simply PMOS)**

- P-channel MOSFET

- Current conducted by holes

- 3 terminal device

- Source (S): p+ (heavily p-type)

- Drain (D): p+

- Gate (G): metal deposited on insulator above channel

- Substrate (called "Body") is a 4<sup>th</sup> terminal

- Substrate is n-doped

- Holes is induced in channel when a negative gate voltage is applied

- Holes moves from Source to Drain

- Current flows from S to D

# CMOS (Complementary MOS)

- CMOS is the prevalent IC technology today

- Since NMOS and PMOS are formed on oppositely doped substrates, one of the transistor needs to be placed in a "well"

- PMOS is placed in an "n well" here.

- Alternatively, NMOS can be placed in p well