#### UNIVERSITY OF CALIFORNIA AT BERKELEY College of Engineering Department of Electrical Engineering and Computer Sciences

### EE105 Lab Experiments

# Experiment 3: Single Stage CE & CS Amplifier

### Contents

| 1        | Introduction                                                                                      | 1 |

|----------|---------------------------------------------------------------------------------------------------|---|

| <b>2</b> | Design Specification                                                                              | 1 |

| 3        | Attenuation network for Input                                                                     | 1 |

| 4        | Single Stage Common-Emitter BJT Amplifier         4.1 Hand Calcuation       4.2 Hspice Simulation |   |

| 5        | Single Stage Common-Source MOSFET Amplifier5.1Hand Calcuation5.2Hspice Simulation                 |   |

### 1 Introduction

Common-Emitter(CE) and Common-Source(CS) are the two most widely used configurations for BJT and MOSFET amplifier design. In this pre-lab, you will explore the design of a single stage amplifier based on these two topologies to understand the trade-off between different specifications(gain, bandwidth and output swing). Initial design starts with hand calculation and finer tuning and verification will be carried out by Hspice simulation. You will use the device parameters you characterized in your Lab 2 in your design.

## 2 Design Specification

The BJT you will use is 2N4401 and the MOSFET you will use is BS170. The design specifications are given in the table below:

| Middle Band $Gain(A_{mid})$     | ≥100                     |

|---------------------------------|--------------------------|

| High Cutoff Frequency $(f_H)$   | ≥20kHz                   |

| Output Swing(SW)                | $\geq 2V$ (peak to peak) |

| Supply $Voltage(V_{dd}/V_{ss})$ | +10V/-10V                |

| Output $load(C_{load})$         | 1nF                      |

Table 1: Amplifier Specification

### 3 Attenuation network for Input

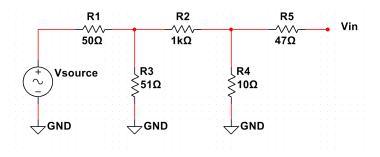

Since the gain of the amplifier is large and the smallest magnitude of function generator is limited. You will need to attenuate the source signal before connecting to the input of your amplifier. The attenuation network

is given as in Figure 1. Calculate the attenuation ratio between Vsource and Vin and output impedance looking from Vin. Draw the Thevenin equivalent model of this network.

Figure 1: Attenuation Network

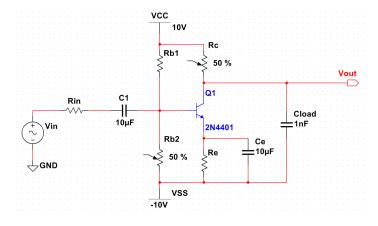

### 4 Single Stage Common-Emitter BJT Amplifier

The CE amplifier is given as in Firgure 2.

Figure 2: Single Stage Common Emitter BJT Amplifier

### 4.1 Hand Calcuation

Explain what is the function of  $R_e$ . Draw small signal equivalent circuit. For hand calculation you could treat emitter as ac ground in your small signal circuit. Derive the expression for the middle band gain and high cutoff frequency (Hint: the high cutoff frequency is determined by  $C_{load}$  and small signal output impdance of the amplifier). Refer to your Lab 2 report for  $\beta$  and  $V_A$ . Use  $R_{in}$  from Thevenin model above. Pick reasonable resistor values to satisfy the design specifications. Since you cannot choose whatever resistor value you want, you need to pick  $R_{b1}$ ,  $R_e$  according to the availability of the resistor values in our labs. Then design  $R_{b2}$  and  $R_c$  value accordingly. You will implement them as potential meter or a combination of resistor and potential meter if necessary in your real lab.

#### 4.2 Hspice Simulation

Implement your design in Hspice and verify all the design specs in the simulation. Tune resistors value if necessary. Keep in mind how each resistor value affect the overall performance.

You need to include model file(npn\_2N4401.mod) in your scripts and modify the BJT model by editing only  $Bf(\beta_F)$  and  $Vaf(V_A)$  in that model file according to your extraction in your Lab 2. Instantiate the model as following:

#### Q<name> <collector> <base> <emitter> BJT\_2N4401

Attach AC simulation results showing the gain and high cutoff frequency are satisfied.Plot gain in dB and frequency in log scale

Attach transient simulation results with waveform of both  $V_{in}$  and  $V_{out}$  showing output swing. The way to measure output swing is as follows: Check the gain at middle band frequency while increasing the input magnitude. Notice the point when the gain starts to fall off middle band gain, which means the output has reached its swing limitation. Record the peak-to-peak value of output at that point as the output swing.

Calculate the total power consumption. Measure the sum of the currents in  $R_{b1}$  and  $R_c$ , then time (Vcc-Vss) to get the total estimation of power consumption.

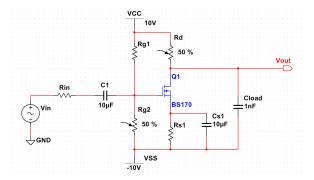

### 5 Single Stage Common-Source MOSFET Amplifier

The CS amplifier is given as in Figure 3.

Figure 3: Single Stage Common Source MOS Amplifier

#### 5.1 Hand Calcuation

Explain what is the function of  $R_s$ . Draw small signal equivalent circuit. For hand calculation you could treat source as ac ground in your small signal circuit. Derive the expression for the middle band gain and high cutoff frequency (Hint: the high cutoff frequency is determined by  $C_{load}$  and the output impedance of the amplifier). Refer to your Lab 2 report for  $V_{th}$  and  $K_n$ . Use  $R_{in}$  from the Thevenin model above. Pick reasonable resistor values to satisfy the design specifications. Since you cannot choose whatever resistor value you want, you need to pick  $R_{g1}$ ,  $R_s$  according to the availability of the resistor values in our labs. Then design  $R_{g2}$  and  $R_d$  value accordingly. You will implement them as potential meter or a combination of resistor and potential meter if necessary in your real lab.

#### 5.2 Hspice Simulation

Implement your design in Hspice and verify all the design specs in simulation. Tune resistors value if necessary. Keep in mind how each resistor value affect the overall performance.

You need to include model file(mos\_BS140.mod) in your scripts and modify the model file by editing only Vto and Kp in that model file according to your extraction in your Lab 2. Instantiate the model as following:

X<name> <drain> <gate> <source> BS170

Attach AC simulation results showing the gain and high cutoff frequency are satisfied.Plot gain in dB and frequency in log scale.

Attach transient simulation results with waveform of both  $V_{in}$  and  $V_{out}$  showing output swing. The way to measure output swing is as follows: Check the output magnitude at middle band frequency while increasing the input magnitude. Notice the point when the gain starts to fall off middle band gain, which means the output has reached its swing limitation. Record the peak-to-peak value of output at that point as the output swing.

Calculate the total power consumption. Measure the sum of the currents in  $R_g 1$  and  $R_d$ , then time (Vcc-Vss) to get the total estimation of power consumption.