# EE 105 | Discussion 2

Kieran Peleaux & Qianyi Xie

### **Discussion Outline**

- Overview of SPICE

- What is SPICE?

- SPICE Workflow

- Netlist Syntax

- Topology & Analysis

- Running a SPICE Simulation

- Viewing Simulation Results

- Beyond the Basics

- Non-ideal op amp practice

### What is SPICE?

**S**imulation

Program with ntegrated

Circuit

Emphasis

- Software used for analog circuit simulation (originally intended for developing ICs)

- Developed @ UC Berkeley—version 1 released in 1973 (under public domain)

- Started out as a command-line tool

- Now multiple companies offer their own packaged versions of spice

- LTspice, HSPICE, PSpice, TINA-TI

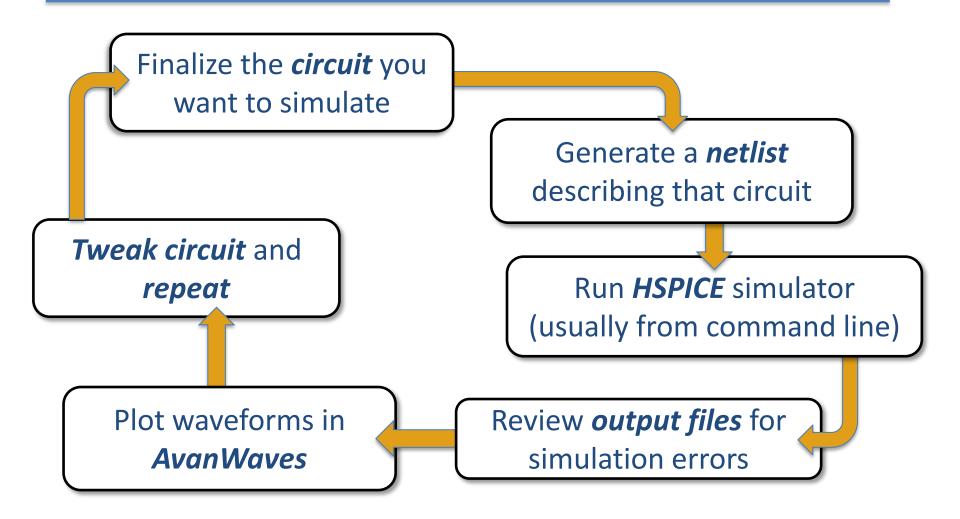

### **SPICE Workflow**

### What is a Netlist?

- A simple text file that contains a *circuit description* and *analysis options*

- Different circuit elements specified by unique commands

- Circuit is topology defined by:

- giving each node a unique name

- assigning elements between these nodes

## **Netlist Syntax**

- Filename ends in .sp

- E.g., mycircuit.sp

- First line is always a comment!

- Not case sensitive

- vs = Vs = VS = vS

- Last line must be .end

- Other than first/last line, order doesn't matter

```

1 EE105 SPICE Tutorial Example 1 - Simple RC Circuit

2 vs vs gnd PWL(Os OV 5ms OV 5.001ms 5V 10ms 5V)

3 r1 vs vo 1k

4 c1 vo gnd 1uF

5 .tran 0.01ms 10ms

6 .option post=2 nomod

7 .end

```

# Netlist Syntax | Topology

- Each line denotes a different circuit element

- The 1<sup>st</sup> term defines the type of element and assigns it an arbitrary number/letter,

- The 2<sup>nd</sup> term is the first node the element is connected to

- The 3<sup>rd</sup> term is the second node the element is connected to (more nodes will follow for devices with >2 terminals)

- The last term is the element value (can use prefixes f, p, n, u, m, k, meg, giga, & tera to denote magnitude)

```

1 EE105 SPICE Tutorial Example 1 - Simple RC Circuit

2 vs vs gnd PWL(Os OV 5ms OV 5.001ms 5V 10ms 5V)

3 r1 vs vo 1k

4 c1 vo gnd 1uF

5 .tran 0.01ms 10ms

6 .option post=2 nomod

7 .end

```

# Netlist Syntax | Topology

- Circuit nodes & elements can have the same name

- gnd is a standard name used to reference ground (can also use 0)

- Order of nodes matters for things like sources!

```

1 EE105 SPICE Tutorial Example 1 - Simple RC Circuit

2 vs vs gnd PWL(Os OV 5ms OV 5.001ms 5V 10ms 5V)

3 r1 vs vo 1k

4 c1 vo gnd 1uF

5 .tran 0.01ms 10ms

6 .option post=2 nomod

7 .end

```

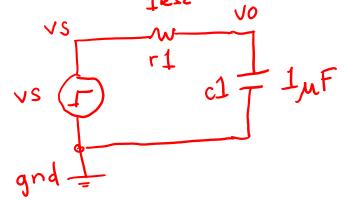

# Netlist Syntax | Topology

• What does this circuit look like? Draw using labels that match the netlist.

- 1 EE105 SPICE Tutorial Example 1 Simple RC Circuit

- 2 vs vs gnd PWL(Os OV 5ms OV 5.001ms 5V 10ms 5V)

- 3 r1 vs vo 1k

- 4 c1 vo gnd 1uF

- 5 .tran 0.01ms 10ms

- 6 .option post=2 nomod

- 7 .end

Berkelev

**Electrical Engineering and Computer Sciences**

## Netlist Syntax | Analysis

- Line 5 tells HSPICE to perform a transient analysis from time t = 0 ms to t = 10 ms in steps of 10 µs

- Line 6 tells HSPICE to generate waveform files necessary for viewing in *awaves* while not including model info in the output

```

1 EE105 SPICE Tutorial Example 1 - Simple RC Circuit

2 vs vs gnd PWL(Os OV 5ms OV 5.001ms 5V 10ms 5V)

3 r1 vs vo 1k

4 c1 vo gnd 1uF

5 .tran 0.01ms 10ms

6 .option post=2 nomod

7 .end

```

## **Simulating in HSPICE**

• To simulate the circuit, simply run the command below in a UNIX terminal

```

hspice mycircuit.sp > mycircuit.lis

```

- This will run the simulation and store the outputs in mycircuit.lis

- You can open mycircuit.lis and check for errors/operating points, but most of the time we'll be interested in looking at plots of voltages and currents

### **Viewing Simulation Results**

To run *awaves*, use the command below (make sure you have X11 enabled!)

awaves &

- This will run the *awaves* software and leave your terminal free to use

- Click "Open Waveform File" & navigate to the file called mycircuit.tr0

| 🛃 CustomExplorer Console    |                                             |      | ×     |

|-----------------------------|---------------------------------------------|------|-------|

| File Edit Tools Options Win | dows Help                                   | SYNC | IPSYS |

| Import a New Design         |                                             |      |       |

| Open Existing Design(s)     |                                             |      |       |

| Open Waveform File          | рэуз, шс.                                   |      |       |

| Load Session                | Version J-2014.09<br>8 Aug 22 2014 11:04:31 |      |       |

| Save Session                | 21:31 (PID:14578)                           |      |       |

| Run Tcl Script              |                                             |      |       |

| Save Log As                 |                                             |      |       |

| Exit                        |                                             | <br> | _     |

| Log History                 |                                             |      |       |

| Command                     |                                             | Ш    | N     |

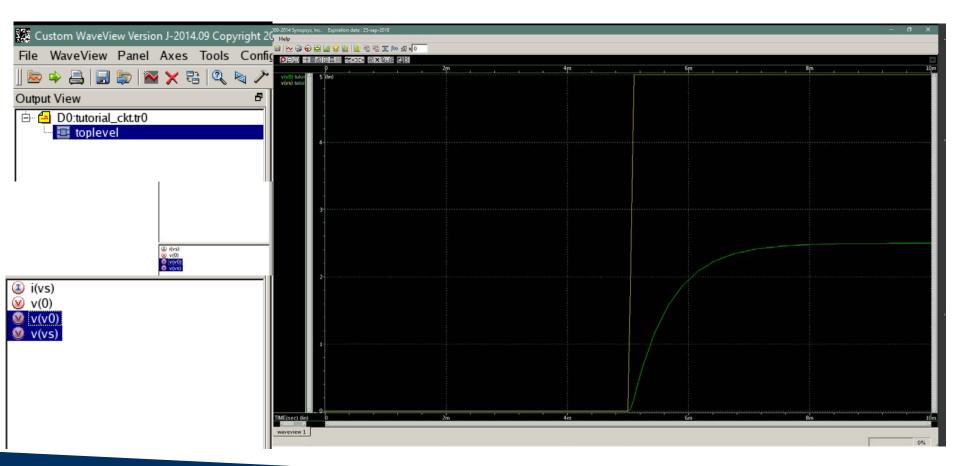

### **Viewing Simulation Results**

• This will open up the Custom WaveView window, where you can add traces to view

## **Beyond the Basics**

- Can perform many different type of analyses

- AC (.ac), DC (.dc), transfer function (.tf), DC operating point (.op)

- For nonlinear devices (diodes, MOSFETs), must define a model to specify device parameters

- Model names cannot start w/ a number!

```

1 EE105 SPICE Tutorial Example 2 - Simple Diode Circuit

2 .model tut_diode d (is=1e-14 vj=0.6 rs=10)

3 vs vs gnd 5V

4 rs vs vd 5k

5 d1 vd gnd tut_diode

6 .op

7 .end

```

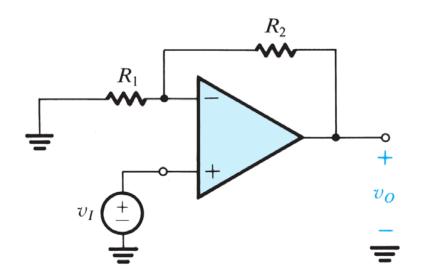

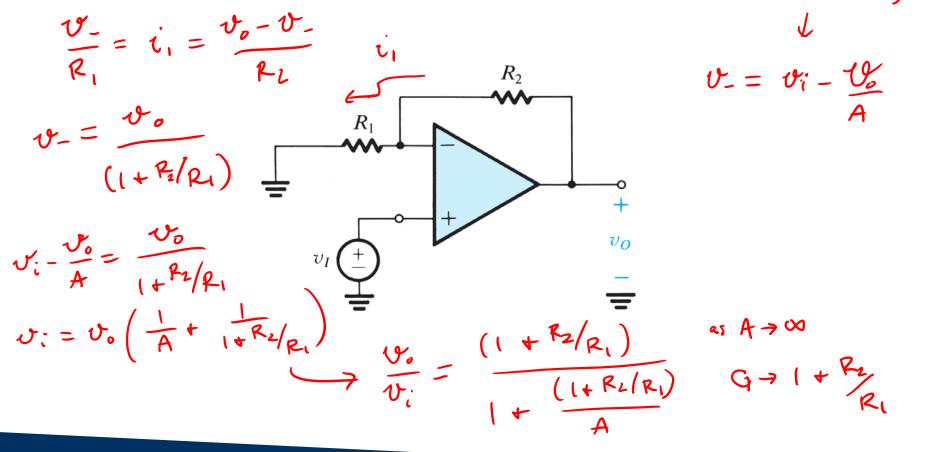

#### Non-ideal Op Amps | Finite Gain

V./Vi Find an expression for the closed loop gain, G' assuming Aclided = -RZ/RI non-infinite open loop gain, A $v_{o} = A(v_{+} - v_{-})$  $\dot{v}_{i} = (v_{i} - v_{-}) = (v_{-} - v_{o})$ vo=A(0-v-)  $R_2$ R, ι,  $v_{-}=-\frac{v_{-}}{A}$  $\frac{3}{\sqrt{R_{l}}} \frac{R_{2}(v_{i}^{2} + \frac{v_{o}}{A})}{R_{l}} = -\frac{v_{o}\left(1 + \frac{1}{A}\right)}{\frac{1}{R_{l}}}$   $\frac{+}{v_{o}} \frac{R_{2}v_{i}^{2}}{R_{l}} = -\frac{v_{o}\left(1 + \frac{1}{A} + \frac{R_{l}}{R_{l}} - \frac{1}{A}\right)}{\frac{1}{R_{l}}}$  $R_1$  $\frac{v_0}{v_i} = \frac{(-R_2/R_1)}{1 + (R_2/R_1 + 1)}$  $a_3 A \rightarrow \infty$   $G \rightarrow - \frac{R_2}{R_1}$

### Non-ideal Op Amps | Finite Gain

• Find an expression for the closed loop gain, G assuming non-infinite open loop gain, A  $\vartheta_0 = (\upsilon_1 - \upsilon_2) A \longrightarrow \upsilon_0 = (\upsilon_1 - \upsilon_2) A$

#### Non-ideal Op Amps | Finite Gain

• If  $R_1 = 1k\Omega$ ,  $R_2 = 9k\Omega$ , and  $A = 10^3$ , find the percent deviation from the ideal case