## Microelectronic Devices and Circuits- EECS105

### Second Midterm Exam

Wendesday, November 17, 1999

Costas J. Spanos

# University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Sciences

|                 | (last) | (first) |  |

|-----------------|--------|---------|--|

| Your Signature: |        |         |  |

- 1. Print and sign your name on this page before you start.

- 2. You are allowed two 8.5"x11" handwritten sheets with formulas. No books or notes!

- 3. Do everything on this exam, and make your methods as clear as possible.

Problem 1 \_\_\_\_\_\_/30

Problem 2 \_\_\_\_\_\_/35

Problem 3 \_\_\_\_\_\_/35

TOTAL \_\_\_\_\_/100

| Problem 1 of 3 Answer | r each question | briefly and | clearly. (30 | ) points) |

|-----------------------|-----------------|-------------|--------------|-----------|

|-----------------------|-----------------|-------------|--------------|-----------|

How does the small signal output resistance of a BJT depend on its size (emitter-to-base junction area), when  $V_{\text{BE}}$  is held constant? (6pts)

Why is it desirable to have  $V_{BS} = 0V$  in MOS Common Gate applications? (6pts)

What happens to the overall (loaded) |Av| when Ic increases in a CE amplifier? (Assume that  $R_L$  is initially equal to ro,  $Rs << r_{\pi}$  and  $r_{oc} = infinity$ )(6 pts)

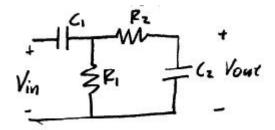

How many poles and how many zeros does this circuit have? What is its function, assuming that  $R_1C_1 << R_2C_2$ ? (6pts)

### Problem 2 of 3 (35 points)

For each of the following questions, make sure that you show the expressions <u>before</u> you plug in the specific values. A correct expression is worth 70% of the credit, even if the numerical calculation is incorrect!

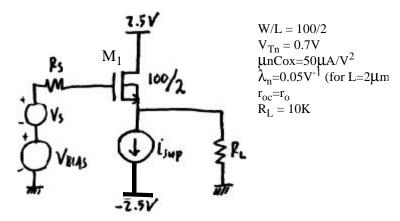

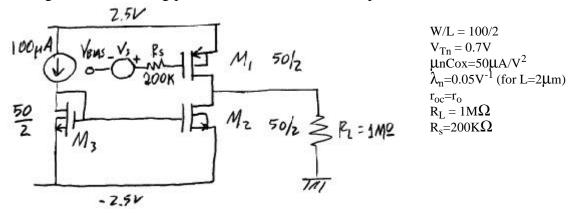

You are given the following nmos common drain amplifier.

a) Assume  $V_{bs}$ =0v, and find  $V_{bias}$  so that  $I_{sup}$  = 500 $\mu$ A. (12pts)

b) Calculate the overall (loaded) voltage gain, with  $V_{bs}=0V$ . (10pts)

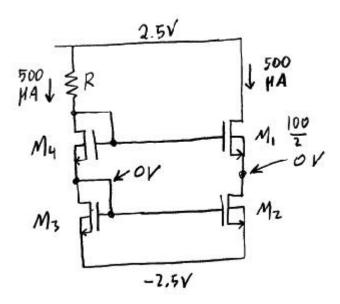

c) You are now going to design the biasing circuit for this amplifier. Assuming that the size of  $M_4$  is the same as  $M_1$  (100/2), size the biasing transistors  $M_2$ ,  $M_3$ , and resistor R in order to get the proper supply current through the common drain amplifier transistor  $M_1$ . Note that the voltage at the drains of  $M_3$  and  $M_2$  is 0V. (13pts)

#### Problem 3 of 3 (35 points)

For each of the following questions, make sure that you show the expressions <u>before</u> you plug in the specific values. A correct expression is worth 70% of the credit, even if the numerical calculation is incorrect!

You are given the following p-channel common-source amplifier.

a) Draw the small signal model of the amplifier. Make sure that you include the entire small signal model of the CS amplifier transistor  $M_1$ , along with all the relevant capacitances, including  $r_{o2}$ ,  $C_{db2}$  and  $C_{gd2}$  from the current sink transistor  $M_2$ . (10 points)

b) Apply the Miller approximation (ignore all capacitances when calculating the Miller gain), and derive a <u>symbolic</u> expression for the complete transfer function (hint: this function has two poles and no zeros) (7 points).

c) Calculate the dc gain and the values of the two poles, given that  $C_{gs1}$ =78fF,  $C_{gd1}$ =25fF,  $C_{gd2}$ =25fF,  $C_{db1}$ =90fF,  $C_{db2}$ =30fF (8 points)

d) Draw the Bode plot for amplitude and phase of the gain of this amplifier (10 points).