### The CPU

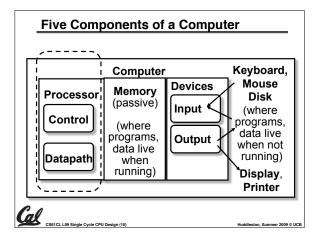

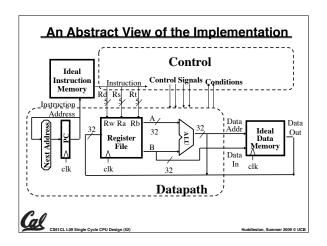

- Processor (CPU): the active part of the computer, which does all the work (data manipulation and decisionmaking)

- Datapath: portion of the processor which contains hardware necessary to perform operations required by the processor (the brawn)

- Control: portion of the processor (also in hardware) which tells the datapath what needs to be done (the brain)

......

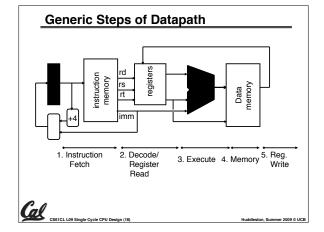

### Stages of the Datapath : Overview

- Problem: a single, atomic block which "executes an instruction" (performs all necessary operations beginning with fetching the instruction) would be too bulky and inefficient

- Solution: break up the process of "executing an instruction" into stages, and then connect the stages to create the whole datapath

- · smaller stages are easier to design

- easy to optimize (change) one stage without touching the others

CS61CL L09 Single Cycle CPU Design (12)

Huddleston Summer 2009 © HC

### Stages of the Datapath (1/5)

- There is a wide variety of MIPS instructions: so what general steps do they have in common?

- Stage 1: Instruction Fetch

- no matter what the instruction, the 32-bit instruction must first be fetched from memory (the cache-memory hierarchy)

- also, this is where we Increment PC (that is, PC = PC + 4, to point to the next instruction: byte addressing so + 4)

Huddleston, Summer 20

### Stages of the Datapath (2/5)

- Stage 2: Instruction Decode

- upon fetching the instruction, we next gather data from the fields (decode all necessary instruction data)

- first, read the opcode to determine instruction type and field lengths

- second, read in data from all necessary registers

- for add, read two registers

- for addi, read one register

- for jal, no reads necessary

igle Cycle CPU Design (14)

Huddleston, Summer 2009 © UC

### Stages of the Datapath (3/5)

- Stage 3: ALU (Arithmetic-Logic Unit)

- the real work of most instructions is done here: arithmetic (+, -, \*, /), shifting, logic (&, l), comparisons (slt)

- · what about loads and stores?

- lw \$t0, 40(\$t1)

- the address we are accessing in memory = the value in \$£1 PLUS the value 40

- so we do this addition in this stage

S61CL L09 Single Cycle CPU Design (15)

Huddleston Summer 2009 @

### Stages of the Datapath (4/5)

- Stage 4: Memory Access

- actually only the load and store instructions do anything during this stage; the others remain idle during this stage or skip it all together

- since these instructions have a unique step, we need this extra stage to account for them

- as a result of the cache system, this stage is expected to be fast

CSS1CL L09 Single Cycle CBU Design (17)

U-14-1-- 0----- 0000 5 U00

### Stages of the Datapath (5/5)

- Stage 5: Register Write

- most instructions write the result of some computation into a register

- examples: arithmetic, logical, shifts, loads, slt

- what about stores, branches, jumps?

- don't write anything into a register at the end

- these remain idle during this fifth stage or skip it all together

Huddleston, Summer 2009 © UCB

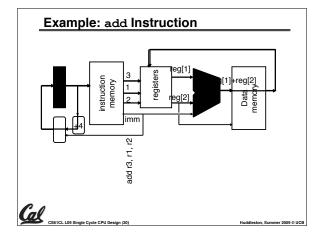

### **Datapath Walkthroughs (1/3)**

- •add \$r3,\$r1,\$r2 # r3 = r1+r2

- Stage 1: fetch this instruction, inc. PC

- Stage 2: decode to find it's an add, then read registers \$r1 and \$r2

- Stage 3: add the two values retrieved in Stage 2

- Stage 4: idle (nothing to write to memory)

- Stage 5: write result of Stage 3 into register \$r3

uddleston. Summer 2009 ©

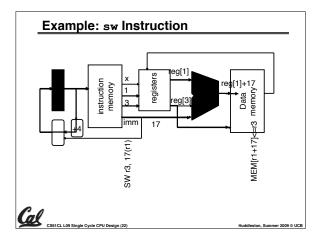

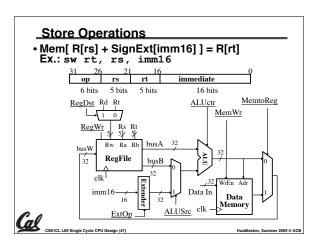

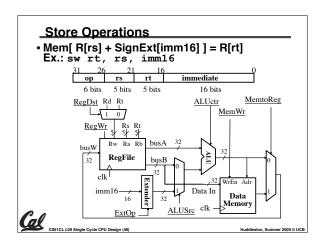

### Datapath Walkthroughs (3/3)

- •sw \$r3, 17(\$r1)

- · Stage 1: fetch this instruction, inc. PC

- Stage 2: decode to find it's a sw, then read registers \$r1 and \$r3

- Stage 3: add 17 to value in register \$r1 (retrieved in Stage 2)

- Stage 4: write value in register \$r3 (retrieved in Stage 2) into memory address computed in Stage 3

- Stage 5: idle (nothing to write into a register)

1CL LOS Single Cuele CDU Decine (21)

Huddleston Summer 2000 © HC

### Why Five Stages? (1/2)

- Could we have a different number of stages?

- · Yes. and other architectures do

- So why does MIPS have five if instructions tend to idle for at least one stage?

- The five stages are the union of all the operations needed by all the instructions.

- There is one type of instruction that uses all five stages: the load

uddleeton Summer 20

### Why Five Stages? (2/2)

- lw \$r3, 17(\$r1)

- · Stage 1: fetch this instruction, inc. PC

- Stage 2: decode to find it's a lw, then read register \$r1

- Stage 3: add 17 to value in register \$r1 (retrieved in Stage 2)

- Stage 4: read value from memory address compute in Stage 3

- Stage 5: write value found in Stage 4 into register \$x3

1CL L09 Single Cycle CPU Design (24)

Huddleston, Summer 2009 ©

#

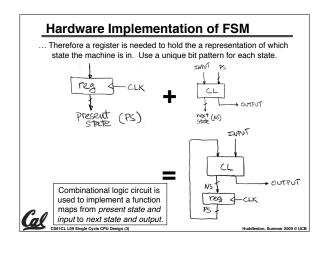

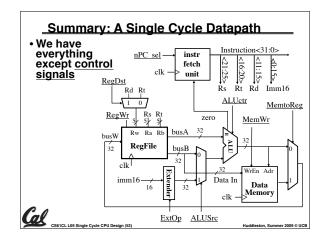

## • The datapath based on data transfers required to perform instructions • A controller causes the right transfers to happen Output: Outp

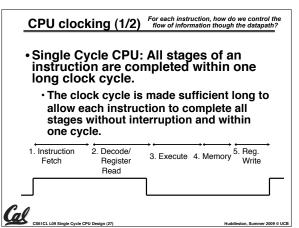

### CPU clocking (2/2) For each instruction, how do we control the flow of information though the datapath? Multiple-cycle CPU: Only one stage of instruction per clock cycle. The clock is made as long as the slowest stage. 1. Instruction 2. Decode/ 3. Execute 4. Memory Fetch Register Write Several significant advantages over single cycle execution: Unused stages in a particular instruction can be skipped OR instructions can be pipelined

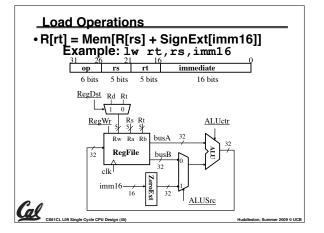

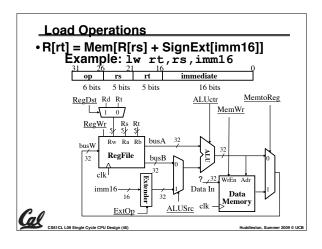

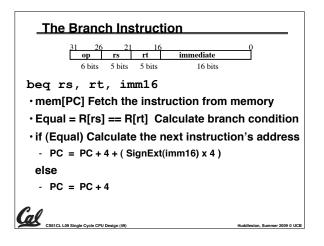

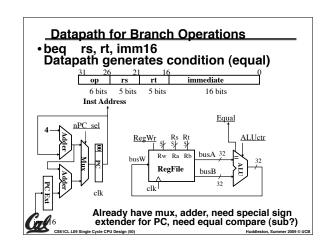

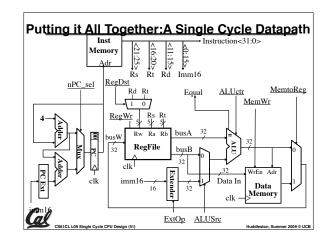

### The MIPS-lite Subset for today ADDU and SUBU ·addu rd.rs.rt op rs rt rd shamt funct 5 bits 5 bits 5 bits 5 bits • subu rd, rs, rt **OR Immediate:** rs ori rt.rs.imm16 6 hits 5 hits 5 bits 16 bits LOAD and STORE Word op rs ·lw rt,rs,imm16 6 bits 5 bits 16 bits •sw rt,rs,imm16 BRANCH: rs rt immediate ·beg rs.rt.imm16 16 bits

(overlapped).

### What Hardware Is Needed? (1/2)

- PC: a register which keeps track of memory addr of the next instruction

- General Purpose Registers

- · used in Stages 2 (Read) and 5 (Write)

- MIPS has 32 of these

- Memory

- · used in Stages 1 (Fetch) and 4 (R/W)

- cache system makes these two stages as fast as the others, on average

### How to Design a Processor: step-by-step

- 1. Analyze instruction set architecture (ISA)

- ⇒ datapath requirements

- · meaning of each instruction is given by the register transfers

- · datapath must include storage element for ISA registers

- · datapath must support each register transfer

- 2. Select set of datapath components and establish clocking methodology

- · 3. Assemble datapath meeting requirements

- 4. Analyze implementation of each instruction to determine setting of control points that effects the register transfer.

- . 5. Assemble the control logic (hard part!)

### · The different fields are:

I-type

J-type

· op: operation ("opcode") of the instruction

op 6 bits

op

op

6 bits

· rs, rt, rd: the source and destination register specifiers

**Review: The MIPS Instruction Formats**

· All MIPS instructions are 32 bits long. 3 formats:

5 bits

5 bits

5 bits

5 bits

target address

5 bits

16 bits

address/immediate

- · shamt: shift amount

- · funct: selects the variant of the operation in the "op" field address / immediate: address offset or immediate value

- target address: target address of jump instruction

### ALU Needs for MIPS-lite + Rest of MIPS

Addition, subtraction, logical OR, ==:

ADDU  $R[rd] = R[rs] + R[rt]; \dots$  $R[rd] = R[rs] - R[rt]; \dots$ SHRH ORI R[rt] = R[rs] | zero ext(Imm16)... BEQ if ( R[rs] == R[rt] )...

- Test to see if output == 0 for any ALU operation gives == test. How?

- P&H also adds AND, Set Less Than (1 if A < B. 0 otherwise)

### How to Design a Processor: step-by-step

- 1. Analyze instruction set architecture (ISA)

- ⇒ datapath requirements

- · meaning of each instruction is given by the register transfers

- · datapath must include storage element for ISA registers

- · datapath must support each register transfer

- 2. Select set of datapath components and establish clocking methodology

- 3. Assemble datapath meeting requirements

- 4. Analyze implementation of each instruction to determine setting of control points that effects the register transfer.

- . 5. Assemble the control logic (hard part!)

### What Hardware Is Needed? (2/2)

- ALU

- · used in Stage 3

- · something that performs all necessary functions: arithmetic, logicals, etc.

- · we'll design details later

- Miscellaneous Registers

- · In implementations with only one stage per clock cycle, registers are inserted between stages to hold intermediate data and control signals as they travels from stage to stage.

- · Note: Register is a general purpose term meaning something that stores bits. Not all registers are in the "register file".

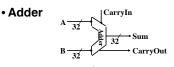

### Combinational Logic Elements (Building Blocks)

### Storage Element: Idealized Memory

- Memory (idealized)

- · One input bus: Data In

- · One output bus: Data Out

- Memory word is found by: · Address selects the word to put on Data Out

- · Write Enable = 1: address selects the memory word to be written via the Data In bus

- Clock input (CLK)

- · The CLK input is a factor ONLY during write operation

- · During read operation, behaves as a combinational logic block:

- Address valid ⇒ Data Out valid after "access time."

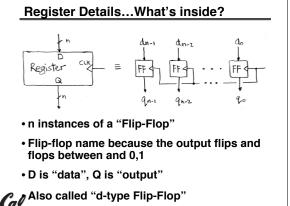

### Storage Element: Register (Building Block)

- Similar to D Flip Flop except

- N-bit input and output

- · Write Enable input

Write Enable:

- negated (or deasserted) (0): Data Out will not change

- asserted (1): Data Out will become Data In on positive edge of clock

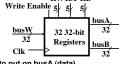

### **Storage Element: Register File**

- · Register File consists of 32 registers:

- · Two 32-bit output busses: busA and busB

- One 32-bit input bus: busW

RWRA RB

- · Register is selected by:

- · RA (number) selects the register to put on busA (data) · RB (number) selects the register to put on busB (data)

- RW (number) selects the register to be written via busW (data) when Write Enable is 1

- · Clock input (clk)

- · The clk input is a factor ONLY during write operation

- · During read operation, behaves as a combinational logic

- RA or RB valid ⇒ busA or busB valid after "access time.

Add & Subtract

### How to Design a Processor: step-by-step

- 1. Analyze instruction set architecture (ISA) ⇒ datapath requirements

- · meaning of each instruction is given by the register transfers

- · datapath must include storage element for ISA registers

- · datapath must support each register transfer

- 2. Select set of datapath components and establish clocking methodology

- 3. Assemble datapath meeting requirements

- 4. Analyze implementation of each instruction to determine setting of control points that effects the register transfer.

- 5. Assemble the control logic (hard part!)

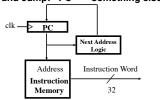

### **Overview of the Instruction Fetch Unit**

- The common RTL operations

- Fetch the Instruction: mem[PC]

- Update the program counter:

- Sequential Code: PC ← PC + 4

- Branch and Jump: PC ← "something else"

Cal

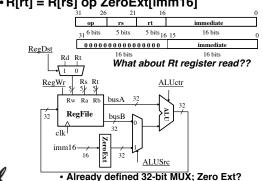

· R[rd] = R[rs] op R[rt] Ex.: addU rd,rs,rt Ra, Rb, and Rw come from instruction's Rs, Rt, and Rd fields · ALUctr and RegWr: control logic after decoding the instruction funct 6 bits 5 bits 5 bits 5 bits · ... Already defined the register file & ALU Rw Ra R busW 32 32-bit 32 busB Registers

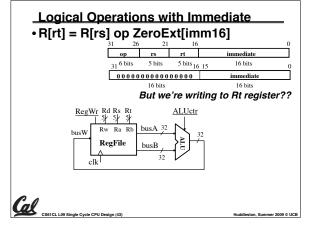

**Logical Operations with Immediate**

•R[rt] = R[rs] op ZeroExt[imm16]

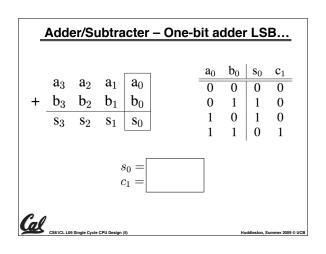

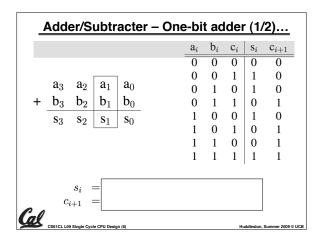

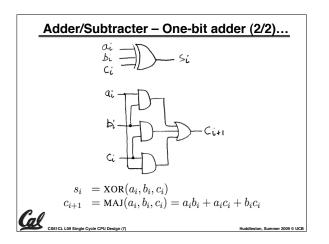

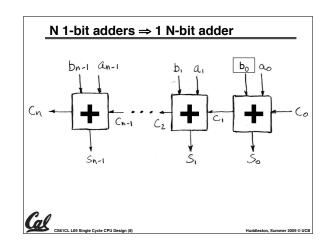

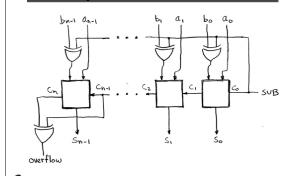

### N-bit adder-subtractor done using N 1-bit adders with XOR gates on input XOR serves as conditional inverter CPU design involves Datapath,Control

- Datapath in MIPS involves 5 CPU stages

1. Instruction Fetch

"And In conclusion..."

- 2. Instruction Decode & Register Read

- 3. ALU (Execute)

- 4. Memory

- Register Write

......

### **Bonus slides**

- These are extra slides that used to be included in lecture notes, but have been moved to this, the "bonus" area to serve as a supplement.

- The slides will appear in the order they would have in the normal presentation

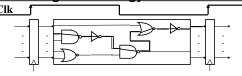

### **Review of Timing Terms**

- Clock (CLK) steady square wave that synchronizes system

- Setup Time when the input must be stable before the rising edge of the CLK

- · Hold Time when the input must be stable after the rising edge of the CLK

- "CLK-to-Q" Delay how long it takes the output to change, measured from the rising edge

- · Flip-flop one bit of state that samples every rising edge of the CLK

- · Register several bits of state that samples on rising edge of CLK or on LOAD

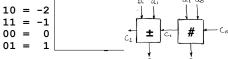

### What about overflow?

- Consider a 2-bit signed # & overflow:

- $\cdot 10 = -2 + -2 \text{ or } -1$

- $\cdot 11 = -1 + -2 \text{ only}$

- $\cdot 00 = 0 \text{ NOTHING!}$

- $\cdot 01 = 1 + 1 \text{ only}$

- Highest adder

- · C<sub>1</sub> = Carry-in = C<sub>in</sub>, C<sub>2</sub> = Carry-out = C<sub>out</sub>

- No  $C_{out}$  or  $C_{in} \Rightarrow NO$  overflow!

What · C<sub>in</sub> and C<sub>out</sub> ⇒ NO overflow!

op?  $(\cdot C_{in} \text{ but no } C_{out} \Rightarrow A,B \text{ both } > 0, \text{ overflow!}$

• C<sub>out</sub> but no C<sub>in</sub> ⇒ A,B both < 0, overflow!

### What about overflow?

Consider a 2-bit signed # & overflow:

Overflows when...

•  $C_{in}$ , but no  $C_{out} \Rightarrow A,B$  both > 0, overflow!  $\cdot C_{out}$ , but no  $C_{in} \Rightarrow A,B$  both < 0, overflow!

overflow =  $c_n \text{ XOR } c_{n-1}$

**Extremely Clever Subtractor**

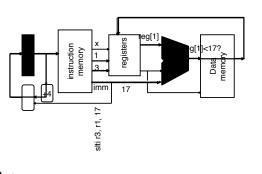

### Datapath Walkthroughs (2/3)

- •slti \$r3,\$r1,17

- Stage 1: fetch this instruction, inc. PC

- Stage 2: decode to find it's an slti. then read register \$r1

- Stage 3: compare value retrieved in Stage 2 with the integer 17

- · Stage 4: idle

- · Stage 5: write the result of Stage 3 in register \$r3

### Example: slti Instruction

Clocking Methodology

- Storage elements clocked by same edge

- Being physical devices, flip-flops (FF) and combinational logic have some delays

- · Gates: delay from input change to output change

- · Signals at FF D input must be stable before active clock edge to allow signal to travel within the FF (set-up time), and we have the usual clock-to-Q delay

- "Critical path" (longest path through logic) determines length of clock period

An Abstract View of the Critical Path Critical Path (Load Instruction) = Delay clock through PC (FFs) + Instruction Memory's Access Time + Register File's Access Time, + ALU to Perform a 32-bit Add + Data Memory Access Time + Ideal Stable Time for Register File Write Instructio (Assumes a fast controller) Instruction In