#### CS 61C:

Great Ideas in Computer Architecture Sequential Elements, Synchronous Digital Systems

Instructors:

Vladimir Stojanovic & Nicholas Weaver http://inst.eecs.Berkeley.edu/~cs61c/sp16

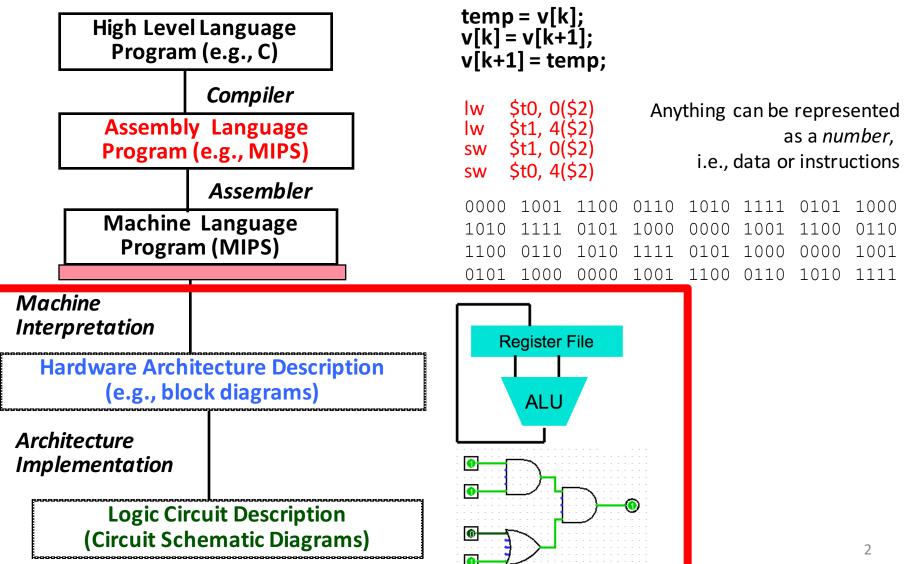

#### Levels of Representation/Interpretation

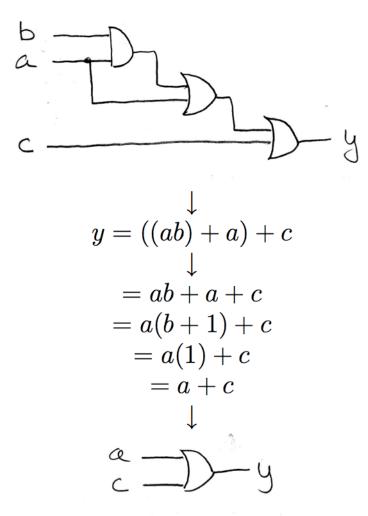

#### Boolean Algebra: Circuit & Algebraic Simplification

original circuit

equation derived from original circuit

algebraic simplification

simplified circuit

#### Laws of Boolean Algebra

| $X \overline{X} = 0$                          | $X + \overline{X} = 1$                         |

|-----------------------------------------------|------------------------------------------------|

| X O = O                                       | X + 1 = 1                                      |

| X 1 = X                                       | X + O = X                                      |

| X X = X                                       | X + X = X                                      |

| X Y = Y X                                     | X + Y = Y + X                                  |

| (X Y) Z = Z (Y Z)                             | (X + Y) + Z = Z + (Y + Z)                      |

| X (Y + Z) = X Y + X Z                         | X + Y Z = (X + Y) (X + Z)                      |

| X Y + X = X                                   | (X + Y) X = X                                  |

| $\overline{X}Y + X = X + Y$                   | $(\overline{X} + Y) X = X Y$                   |

| $\overline{XY} = \overline{X} + \overline{Y}$ | $\overline{X + Y} = \overline{X} \overline{Y}$ |

Complementarity Laws of 0's and 1's Identities Idempotent Laws Commutativity Associativity Distribution **Uniting Theorem** Uniting Theorem v. 2 DeMorgan's Law

#### Boolean Algebraic Simplification Example

y = ab + a + c

. .

## Boolean Algebraic Simplification Example

$$y = ab + a + c$$

= a(1) + c

= a + c

= a(b+1) + c

- abcy

- 0000

- 0011

- 0100

- 0111

- 1001

- 1011

- 1101

- 1111

distribution, identity law of 1's identity

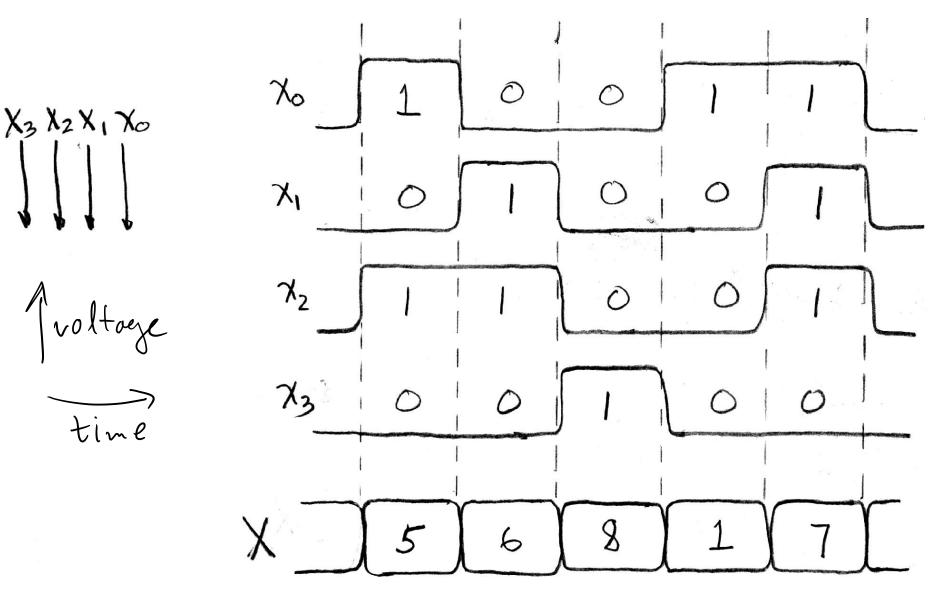

#### Signals and Waveforms: Grouping

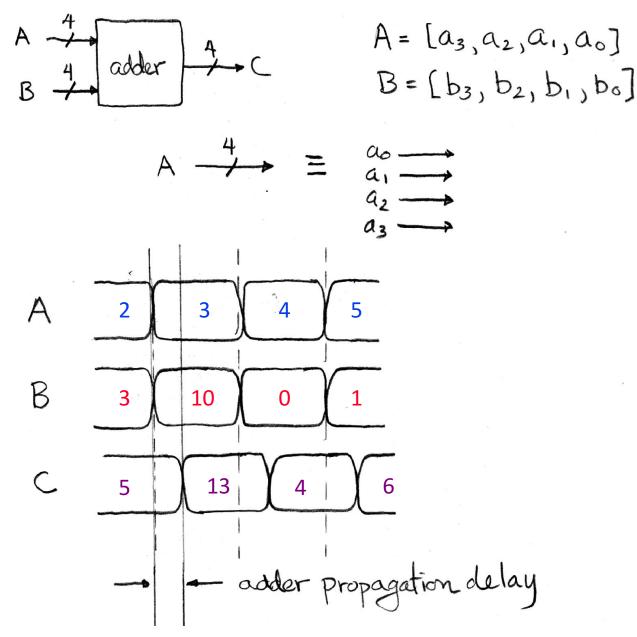

#### Signals and Waveforms: Circuit Delay

#### Sample Debugging Waveform

| <mark>∰</mark> wave – default<br><u>F</u> ile <u>E</u> dit <u>C</u> ursor <u>Z</u> oom <u>B</u> ookm | ark F <u>o</u> rma | t <u>W</u> indow |         |                              |        |        |        |      |      |     |        |      |        |        | _ 8  |

|------------------------------------------------------------------------------------------------------|--------------------|------------------|---------|------------------------------|--------|--------|--------|------|------|-----|--------|------|--------|--------|------|

| 🗃 🖬 🖨 🕴 👗 🖻 🛍 🕴 🔔 .                                                                                  | 🔉 T <del>c</del> 🚽 | 「   ⊕ <b>(</b> ( | e, Q, Q | <b>. <mark>.</mark>x   (</b> |        | 1. 1.  | K      |      |      |     |        |      |        |        |      |

| 🧶 /tb/DBG_00[10]                                                                                     | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| /tb/DBG_00[9]                                                                                        | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| /tb/DBG_00[8]                                                                                        | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| 🥥 /tb/DBG_00[7]                                                                                      | St1                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| 🧶 /tb/DBG_00[6]                                                                                      | St0                |                  |         | 1                            |        |        |        |      |      |     |        |      |        |        |      |

| 🥙 /tb/DBG_00[5]                                                                                      | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| 🥙 /tb/DBG_00[4]                                                                                      | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| 🥙 /tb/DBG_00[3]                                                                                      | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| 🥑 /tb/DBG_00[2]                                                                                      | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| /tb/DBG_00[1]                                                                                        | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| /tb/DBG_00[0]                                                                                        | St0                | пп               | ΠΠ      |                              | ΠΠ     | ΠΠ     | ΠΠ     | ΠΠ   | ΠΠ   |     | ΠΠ     | ΠΠ   | ΠΠ     |        | Π    |

| ⊡/tb/A                                                                                               | 0000               | 003              | 4.1fef  | 0035.0                       | 038 00 | 36 003 | 8,0037 | 0038 |      | 003 | 9.1fee | 003a | fee 00 | 3b,1fe | :d   |

| œ-∥ /tb/IB                                                                                           | 3a                 | 3a               |         |                              |        | 3e     |        |      |      |     |        |      |        |        |      |

| œ-⊘ /tb/ROMAD                                                                                        | 0000               | 1fef             |         | 0038                         |        |        |        |      | 1    | fee |        |      | X1     | fed    |      |

| <b>⊡-</b> ⊘ <u>/tb/D</u>                                                                             | ff                 | <u> </u>         |         |                              |        |        |        |      |      |     | 00     | ff   |        | 39     |      |

| ⊡-@ /tb/TState                                                                                       | 0                  | 2                | 3       | : 1 2                        |        |        |        | 3 4  | 5 (  | 2   |        |      | 3 (1   | 2      |      |

| 🥘 /tb/0E_n                                                                                           | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| /tb/RAMCS_n                                                                                          | St1                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| <pre>/tb/ROMCS_n</pre>                                                                               | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| ⊘ /tb/₩E_n                                                                                           | St1<br>St0         |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| ⊘ /tb/X_0E_n ⊘ /tb/X_RAMCS_n                                                                         | Stu<br>St1         |                  |         |                              |        |        |        |      |      |     |        |      |        |        | L    |

| <pre>/tb/X_ROMCS_n</pre>                                                                             | St0                |                  |         | ╞╎┝┤                         |        |        |        | H    |      |     |        |      |        |        |      |

| /tb/ReadVRAM                                                                                         | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| <ul> <li>/tb/CSyncX</li> </ul>                                                                       | St0                |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

|                                                                                                      |                    |                  | <br>    |                              |        |        |        |      |      |     |        |      |        |        |      |

|                                                                                                      | 0 ps               |                  | us      |                              | Dius   | 10     | 2 us   |      | 4 us |     | Sus    | 10   | 8 us   |        | Dius |

| •                                                                                                    | 0 ps               |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

| 96986540 ps to 111169300 j                                                                           |                    |                  |         |                              |        |        |        |      |      |     |        |      |        |        |      |

## **Clickers/Peer Instruction**

• Simplify  $Z = A + BC + \overline{A}(\overline{BC})$

- A: Z = 0

- B:  $Z = \overline{A(1 + BC)}$

- C: Z = (A + BC)

- D: Z = BC

- E: Z = 1

# Type of Circuits

- *Synchronous Digital Systems* consist of two basic types of circuits:

- Combinational Logic (CL) circuits

- Output is a function of the inputs only, not the history of its execution

- E.g., circuits to add A, B (ALUs)

- Sequential Logic (SL)

- Circuits that "remember" or store information

- aka "State Elements"

- E.g., memories and registers (Registers)

## **Uses for State Elements**

- Place to store values for later re-use:

- Register files (like \$1-\$31 in MIPS)

- Memory (caches and main memory)

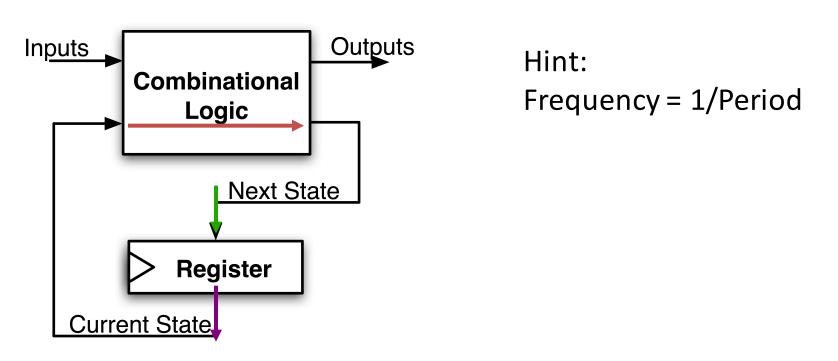

- Help control flow of information between combinational logic blocks

- State elements hold up the movement of information at input to combinational logic blocks to allow for orderly passage

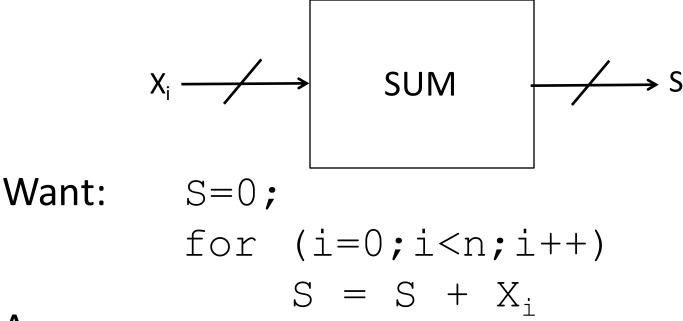

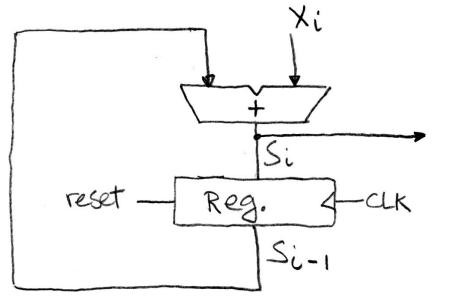

#### **Accumulator Example**

Why do we need to control the flow of information?

Assume:

- Each X value is applied in succession, one per cycle

- After n cycles the sum is present on S

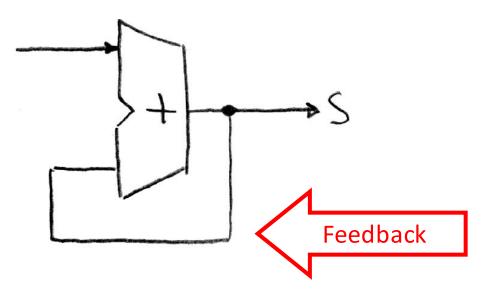

## First Try: Does this work?

#### No!

Reason #1: How to control the next iteration of the 'for' loop? Reason #2: How do we say: 'S=0'?

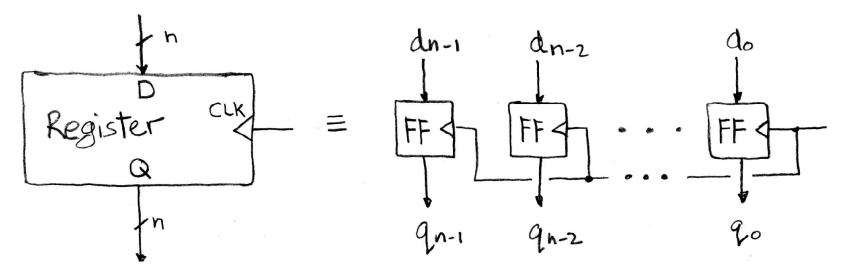

#### **Register Internals**

- n instances of a "Flip-Flop"

- Flip-flop name because the output flips and flops between 0 and 1

- D is "data input", Q is "data output"

- Also called "D-type Flip-Flop"

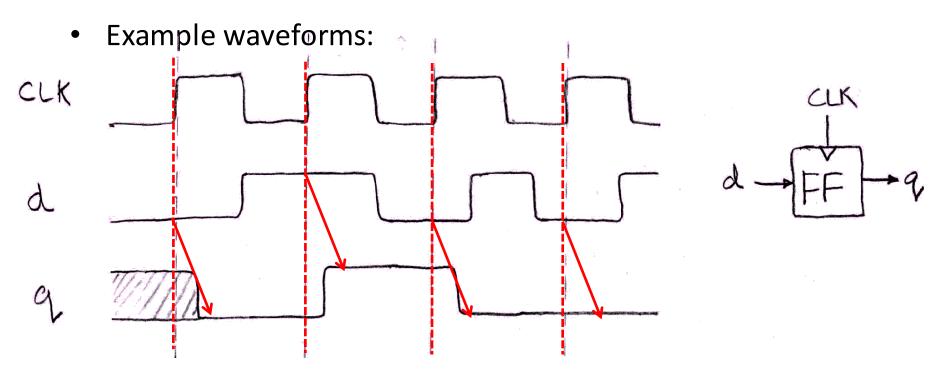

# Flip-Flop Operation

- Edge-triggered d-type flip-flop

This one is "positive edge-triggered"

- "On the rising edge of the clock, the input d is sampled and transferred to the output. At all other times, the input d is ignored."

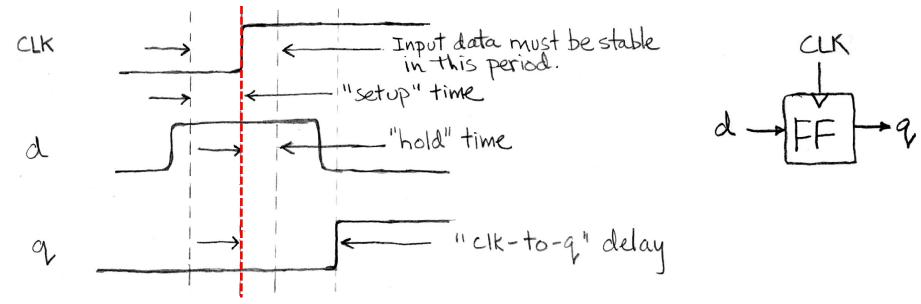

## Flip-Flop Timing

- Edge-triggered d-type flip-flop

This one is "positive edge-triggered"

- "On the rising edge of the clock, the input d is sampled and transferred to the output. At all other times, the input d is ignored."

- Example waveforms (more detail):

# Camera Analogy Timing Terms

- Want to take a portrait timing right before and after taking picture

- Set up time don't move since about to take picture (open camera shutter)

- Hold time need to hold still after shutter opens until camera shutter closes

- *Time click to data* time from open shutter until can see image on output (viewscreen)

## Hardware Timing Terms

- Setup Time: when the input must be stable before the edge of the CLK

- Hold Time: when the input must be stable after the edge of the CLK

- "CLK-to-Q" Delay: how long it takes the output to change, measured from the edge of the CLK

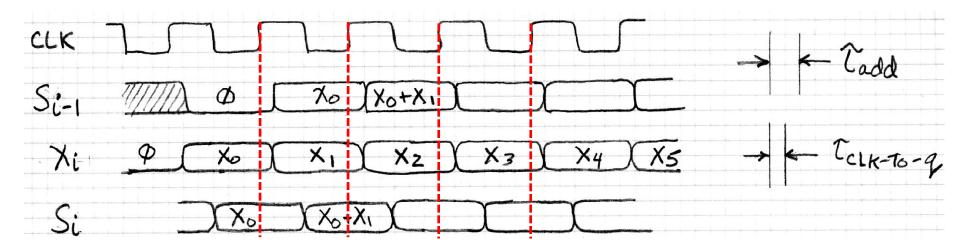

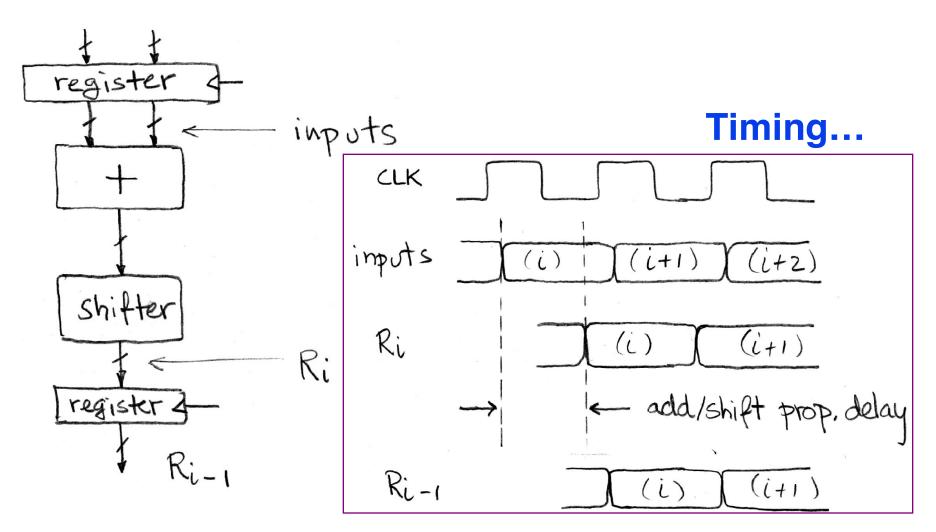

## Accumulator Timing 1/2

- Reset input to register is used to force it to all zeros (takes priority over D input).

- S<sub>i-1</sub> holds the result of the i<sup>th</sup>-1 iteration.

- Analyze circuit timing starting at the output of the register.

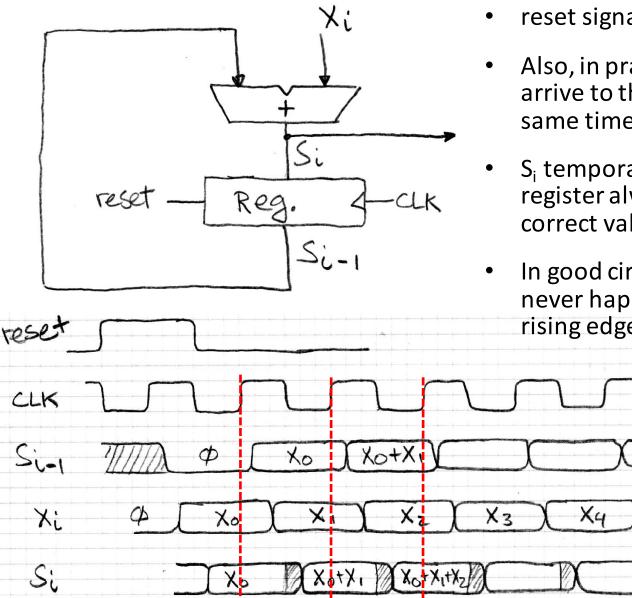

## Accumulator Timing 2/2

- reset signal shown.

- Also, in practice X might not arrive to the adder at the same time as S<sub>i-1</sub>

- S<sub>i</sub> temporarily is wrong, but register always captures correct value.

- In good circuits, instability never happens around rising edge of clk.

Ladd

LCLK-TO-9

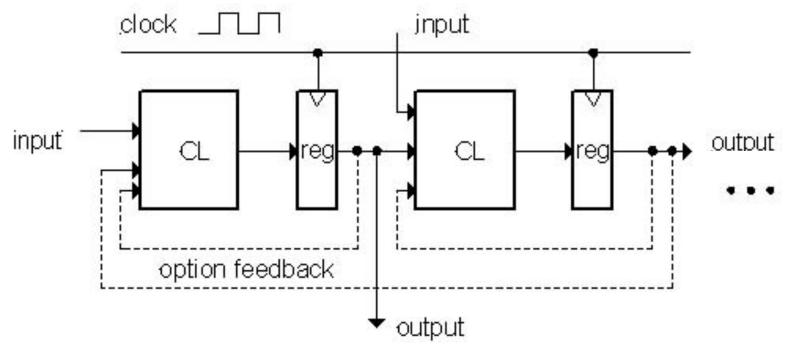

# Model for Synchronous Systems

- Collection of Combinational Logic blocks separated by registers

- Feedback is optional

- Clock signal(s) connects only to clock input of registers

- Clock (CLK): steady square wave that synchronizes the system

- Register: several bits of state that samples on rising edge of CLK (positive edge-triggered) or falling edge (negative edge-triggered)

## Maximum Clock Frequency

• What is the maximum frequency of this circuit?

Period = Max Delay = CLK-to-Q Delay + CL Delay + Setup Time

#### **Critical Paths**

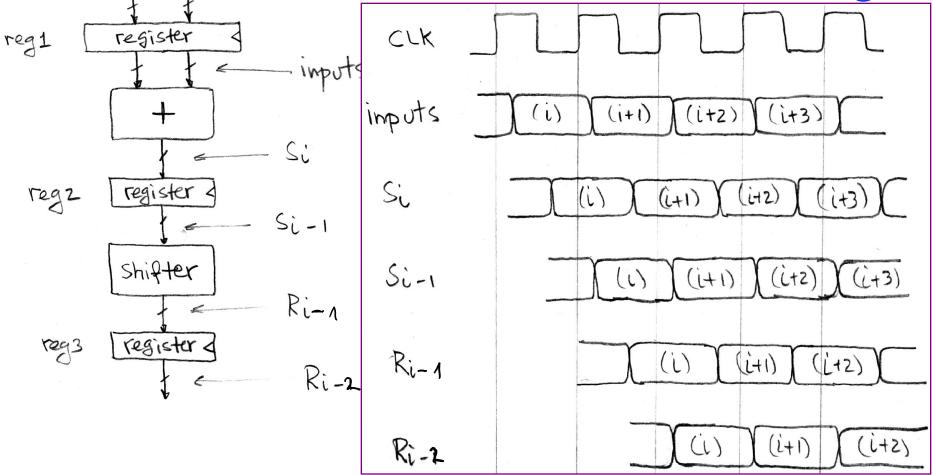

Note: delay of 1 clock cycle from input to output. Clock period limited by propagation delay of adder/shifter.

#### Pipelining to improve performance Timing...

- Insertion of register allows higher clock frequency

- More outputs per second (higher bandwidth)

- But each individual result takes longer (greater latency)

#### **Recap of Timing Terms**

- Clock (CLK) steady square wave that synchronizes system

- Setup Time when the input must be stable <u>before</u> the rising edge of the CLK

- Hold Time when the input must be stable <u>after</u> the rising edge of the CLK

- "CLK-to-Q" Delay how long it takes the output to change, measured from the rising edge of the CLK

- Flip-flop one bit of state that samples every rising edge of the CLK (positive edge-triggered)

- Register several bits of state that samples on rising edge of CLK or on LOAD (positive edge-triggered)

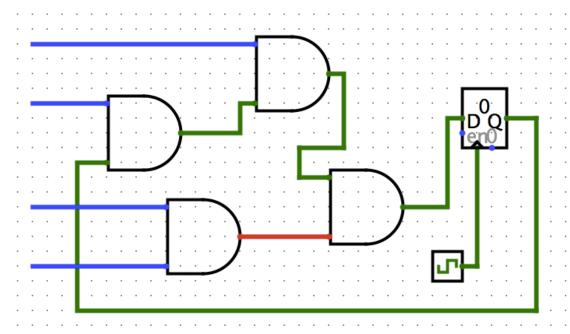

## **Clickers/Peer Instruction**

Clock->Q 1ns Setup 1ns Hold 1ns AND delay 1ns

What is maximum clock frequency? (assume all unconnected inputs come from some register)

- A: 5 GHz

- B: 200 MHz

- C: 500 MHz

- D: 1/7 GHz

- E: 1/6 GHz

# Administrivia

- No lecture on Wed study for midterm

- Midterm 1 is on Thu 2/25

- Time 6-8pm

- Location

- 2050 VLSB(aa-lz)

- 1 Pimentel(ma-zz)

- Covers up to and including 02/17 lecture (CALL 2)

- 1 handwritten, double sided, 8.5"x11" cheat sheet

We'll give you MIPS green sheet

- Emails sent-out to students requiring special accommodation for the exam please respond

# **Study Advice**

- 1. Review slides, book, worksheets, etc. and add to your cheatsheet as you do so

- a. <u>This step is not the end</u>

- 2. Take a mock exam in the allotted time, using only your cheatsheet

- 3. Go over solutions, look at *why* the answers are what they are (especially for questions you answered incorrectly)

- 4. Update cheatsheet as necessary

- 5. if (!perfect) goto 2;