| <ul> <li>I/O Speed: byte<br/>(from mouse to</li> </ul> |          | •       |                  |

|--------------------------------------------------------|----------|---------|------------------|

| <ul> <li>Device</li> </ul>                             | Behavior | Partner | Data Rate (KB/s) |

| Keyboard                                               | Input    | Human   | 0.01             |

| Mouse                                                  | Input    | Human   | 0.02             |

| Voice output                                           | Output   | Human   | 5.00             |

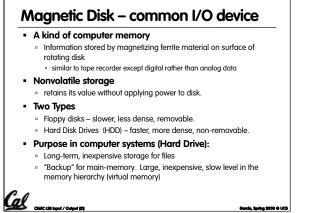

| Floppy disk                                            | Storage  | Machine | 50.00            |

| Laser Printer                                          | Output   | Human   | 100.00           |

| Magnetic Disk                                          | Storage  | Machine | 10,000.00        |

| Wireless Network                                       | l or O   | Machine | 10,000.00        |

| Graphics Display                                       | Output   | Human   | 30,000.00        |

| Wired LAN Network                                      | l or O   | Machine | 125,000.00       |

### Processor-I/O Speed Mismatch

- 1GHz microprocessor can execute 1 billion load or store instructions per second, or 4,000,000 KB/s data rate

- I/O devices data rates range from 0.01 KB/s to 125,000 KB/s

- Input: device may not be ready to send data as fast as the processor loads it • Also, might be waiting for human to act

- Output: device not be ready to accept data as fast as processor stores it

- What to do?

al

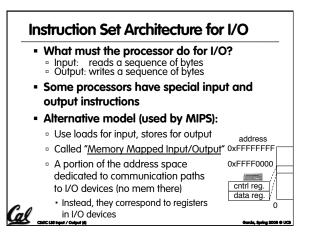

## **Processor Checks Status before Acting**

- Path to device generally has 2 registers:

- <u>Control Register</u>, says it's OK to read/write

- (I/O ready) [think of a flagman on a road]

- Data Register, contains data

- Processor reads from Control Register in loop, spins while waiting for device to set Ready bit in Control reg ( $0 \Rightarrow 1$ ) to say its OK

- Processor then loads from (input) or writes to (output) data register

- Load from or Store into Data Register resets Ready bit (1)  $\Rightarrow$  0) of Control Register

- This is called "Polling"

Cal

# What is the alternative to polling? Wasteful to have processor spend most of its time "spin-waiting" for I/O to be ready Would like an unplanned procedure call that would be invoked only when I/O

device is ready Solution: use exception mechanism to help I/O. Interrupt program when I/O ready,

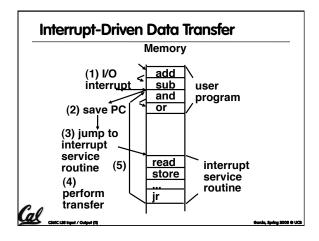

## I/O Interrupt

Cal

#### An I/O interrupt is like overflow exceptions except:

- An I/O interrupt is "asynchronous"

- More information needs to be conveyed

- An I/O interrupt is asynchronous with respect to instruction execution:

- I/O interrupt is not associated with any instruction, but it can happen in the middle of any given instruction

- I/O interrupt does not prevent any instruction from completion

cia, Spring 2008 © UCB

| Week #                                                      | Mon                          | Wed                               | Thu Lab  | Fri                                               |

|-------------------------------------------------------------|------------------------------|-----------------------------------|----------|---------------------------------------------------|

| #13<br>This week                                            |                              | I/O<br>P3 out                     | VM       | Performance                                       |

| #14<br>Last week<br>o' classes                              | Inter-machine<br>Parallelism | Summary,<br>Review,<br>Evaluation | Parallel | Intra-machine<br>Parallelism<br>(Scott)<br>P3 due |

| #15<br>RRR Week                                             |                              |                                   |          | Perf comp<br>due 11:59pm                          |

| #16<br>Finals Week<br>Review Sun<br>May 9 3-6pm<br>10 Evans |                              |                                   |          | Final Exam<br>8-11am in<br>Hearst Gym             |

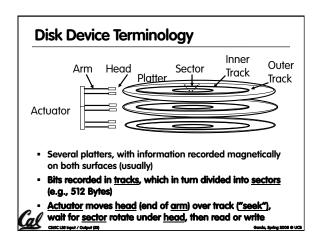

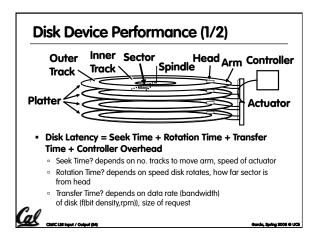

- Average distance of sector from head?

- 1/2 time of a rotation

Cal

- □ 7200 Revolutions Per Minute  $\Rightarrow$  120 Rev/sec

- $\circ~$  1 revolution = 1/120 sec  $\Rightarrow$  8.33 milliseconds

- 1/2 rotation (revolution)  $\Rightarrow$  4.17 ms

- Average no. tracks to move arm?

- Disk industry standard benchmark:

- Sum all time for all possible seek distances from all possible tracks / # possible

- Assumes average seek distance is random

- Size of Disk cache can strongly affect perf!

Cache built into disk system, OS knows nothing

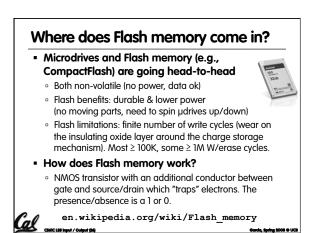

en.wikipedia.org/wiki/lpod www.apple.com/ipod What does Apple put in its iPods? Samsung flash 4, 8GB Toshiba flash Toshiba 1.8-inch HDD Toshiba flash 1, 2GB 80, 160GB 8, 16, 32GB 22 🔲 16 🗖 S II 🐼 shuffle, classic, touch nano Cal

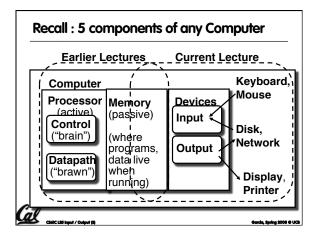

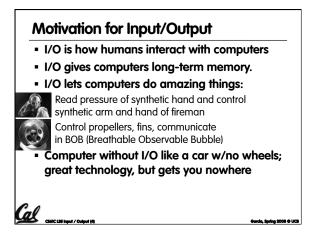

| <ul> <li>I/O gives computers their 5 set</li> </ul>                                         | enses       |

|---------------------------------------------------------------------------------------------|-------------|

| I/O speed range is 100-million                                                              | n to one    |

| <ul> <li>Processor speed means must<br/>with I/O devices before use</li> </ul>              | synchronize |

| Polling works, but expensive                                                                |             |

| processor repeatedly queries dev                                                            | vices       |

| Interrupts works, more compl                                                                | ex          |

| <ul> <li>devices causes an exception, can<br/>OS to run and deal with the device</li> </ul> | 5           |

| I/O control leads to Operating                                                              | - Sustana   |