www.neoseeker.com/news/13615-very-rareatari-2600-air-raid-game-sells-for-31-600-usd/

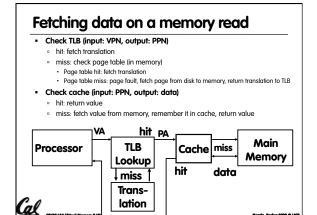

## What if not in TLB?

Cal CHELLA VINNE

- Option 1: Hardware checks page table and loads new Page Table Entry into TLB

- Option 2: Hardware traps to OS, up to OS to decide what to do

- MIPS follows Option 2: Hardware knows nothing about page table

- A trap is a synchronous exception in a user process, often resulting in the OS taking over and performing some action before returning to the program.

arcia, Spring 2010 © UCB

- More about exceptions next lecture

Cal

- We load the page off the disk into a free block of memory, using a DMA transfer (Direct Memory Access – special hardware support to avoid processor)

- Meantime we switch to some other process waiting to be run

- When the DMA is complete, we get an interrupt and update the process's page table

- So when we switch back to the task, the desired data will be in memory

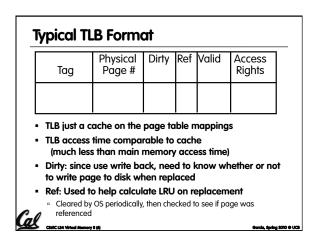

## What if we don't have enough memory?

- We chose some other page belonging to a program and transfer it onto the disk if it is dirty

- If clean (disk copy is up-to-date), just overwrite that data in memory

- We chose the page to evict based on replacement

- policy (e.g., LRU)

- And update that program's page table to reflect the fact that its memory moved somewhere else

- If continuously swap between disk and

- memory, called Thrashing

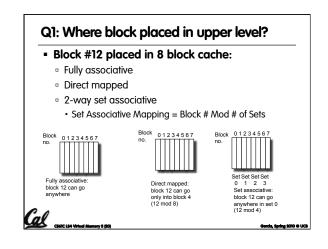

| Easy for             | r Direct   | Mappe   | ed     |          |      |       |

|----------------------|------------|---------|--------|----------|------|-------|

| •Set Ass             | ociative   | or Full | y Asso | ciative: |      |       |

| 🛛 Rana               | dom        |         |        |          |      |       |

| □ LRU                | (Least Red | ently U | sed)   |          |      |       |

| Miss Rat             | es         |         |        |          |      |       |

| Associativity: 2-way |            | 4-way   |        | 8-way    |      |       |

| Size                 | LRU        | Ran     | LRU    | Ran      | LRU  | Ran   |

| 16 KB                | 5.2%       | 5.7%    | 4.7%   | 5.3%     | 4.4% | 5.0%  |

| 64 KB                | 1.9%       | 2.0%    | 1.5%   | 1.7%     | 1.4% | 1.5%  |

| 256 KB               | 1.15%      | 1.17%   | 1.13%  | 1.13%    | 112% | 1.12% |

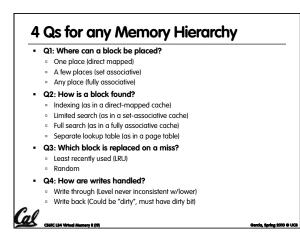

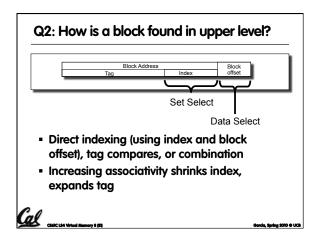

## Q4: What to do on a write hit? Write-through

• update the word in cache block and corresponding word in memory

## Write-back

- update word in cache block

- allow memory word to be "stale"

- => add 'dirty' bit to each line indicating that memory be updated when block is replaced => OS flushes cache before I/O !!!

## Performance trade-offs?

- WT: read misses cannot result in writes

- WB: no writes of repeated writes

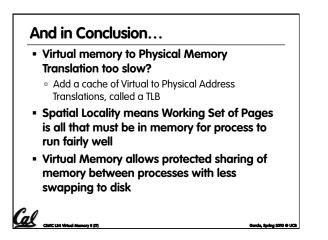

Three Advantages of Virtual Memory

#### I) Translation:

Cal CARCEDA Viewal

rcia, Spring 2010 © UCB

- Program can be given consistent view of memory, even though physical memory is scrambled

- Makes multiple processes reasonable

- Only the most important part of program ("Working Set") must be in physical memory

- Contiguous structures (like stacks) use only as much physical memory as necessary yet still grow later

Barcla, Spring 2010 © UCB

## Three Advantages of Virtual Memory

#### 2) Protection:

- Different processes protected from each other

- Different pages can be given special behavior

- (Read Only, Invisible to user programs, etc).

- Kernel data protected from User programs

- Very important for protection from malicious programs  $\Rightarrow$  Far more "viruses" under Microsoft Windows

- Special Mode in processor ("Kernel mode") allows processor to change page table/TLB

#### 3) Sharing:

al

Can map same physical page to multiple users ("Shared memory")

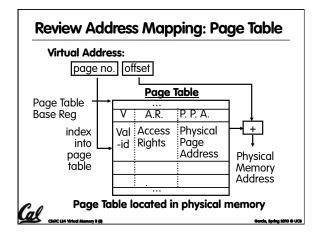

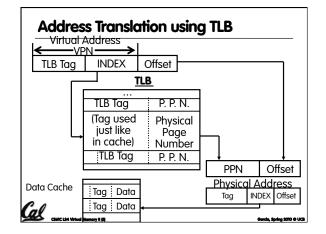

## Why Translation Lookaside Buffer (TLB)?

- Paging is most popular implementation of virtual memory (vs. base/bounds)

- Every paged virtual memory access must be checked against Entry of Page Table in memory to provide protection / indirection

- Cache of Page Table Entries (TLB) makes address translation possible without memory access in common case to make fast

# Bonus slide: Virtual Memory Overview (1/3)

### • User program view of memory:

- Contiguous

- Start from some set address

- Infinitely large

- Is the only running program

- Reality:

- Non-contiauous

- Start wherever available memory is

- Finite size

Implementation:

Call Call Call Vitual Memory II (29)

Cal

Many programs running at a time

Bonus slide: Virtual Memory Overview (3/3)

virtual addresses into physical addresses • Think of memory as a cache for disk • TLB is a cache for the page table

• Operating system controls page table that maps

Divide memory into "chunks" (pages)

### Bonus slide: Virtual Memory Overview (2/3)

## Virtual memory provides:

illusion of contiguous memory

Call CARC LAA Vited Memory 1 (84)

- all programs starting at same set address

- illusion of ~ infinite memory (232 or 264 bytes)

- protection

Cal

#### Address Map, Mathematically $\begin{array}{l} V = \{0,\,1,\,\ldots\,,\,n-1\} & virtual \ address \ space \ (n > m) \\ M = \{0,\,1,\,\ldots\,,\,m-1\} & physical \ address \ space \\ MAP: \ V \dashrightarrow M \ U \ \{\theta\} & address \ mapping \ function \end{array}$ MAP(a) = a' if data at virtual address <u>a</u> is present in physical address <u>a'</u> and <u>a'</u> in M = $\theta$ if data at virtual address a is not present in M page fault Name Space V OS fault Processor handler Addr Trans 0 Main Disk Mechanism Memory а physical OS performs Cal CARE LEA Viewel AV this transfer Garda, Spring 2000 & UCS address