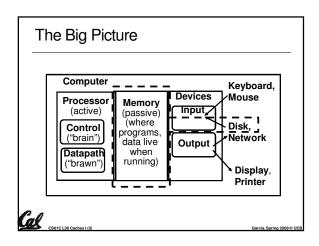

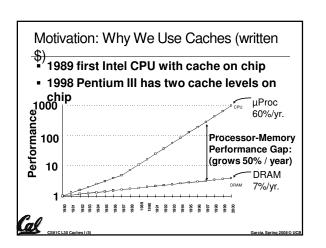

- Mismatch between processor and memory speeds leads us to add a new level: a memory cache

- Implemented with same IC processing technology as the CPU (usually integrated on same chip): faster but more expensive than DRAM memory.

- Cache is a copy of a subset of main memory.

- Most processors have separate caches

- for instructions and data.

Memory Hierarchy Analogy: Library (1/2)

- You're writing a term paper (Processor) at a table in Doe

- Doe Library is equivalent to disk

- essentially limitless capacity

- very slow to retrieve a book

Cal

- Table is main memory

- smaller capacity: means you must return book when table fills up

- easier and faster to find a book there once you've already retrieved it

# Memory Hierarchy Analogy: Library (2/2)

- Open books on table are cache

- smaller capacity: can have very few open books fit on table; again, when table fills up, you must close a book

- much, much faster to retrieve data

- Illusion created: whole library open on the tabletop

- Keep as many recently used books open on table as possible since likely to use again

- Also keep as many books on table as possible, since faster than going to library

#### Memory Hierarchy Basis

- Cache contains copies of data in memory that are being used.

- Memory contains copies of data on disk that are being used.

- Caches work on the principles of temporal and spatial locality.

- Temporal Locality: if we use it now, chances are we'll want to use it again soon.

- Spatial Locality: if we use a piece of memory, chances are we'll use the neighboring pieces soon.

## Cache Design

Cal

Cal (SATE LAD

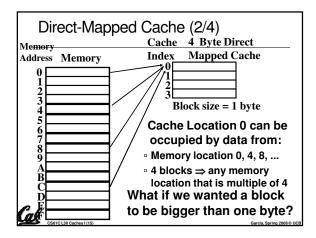

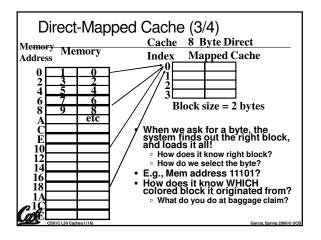

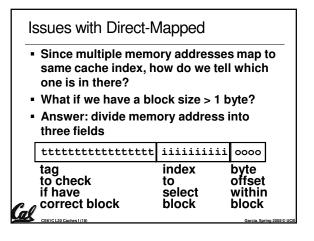

- How do we organize cache?

- Where does each memory address map to?

- (Remember that cache is subset of memory, so multiple memory addresses map to the same cache location.)

- How do we know which elements are in cache?

- How do we quickly locate them?

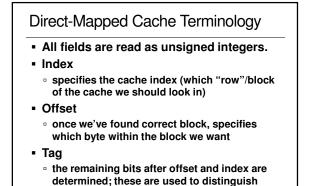

between all the memory addresses that map

to the same location

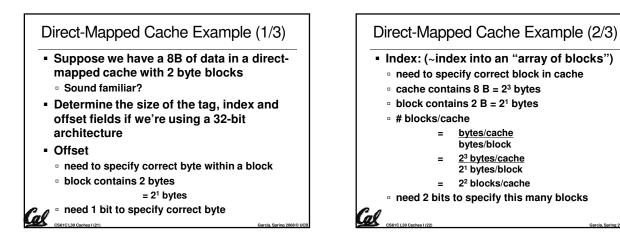

# Direct-Mapped Cache Example (3/3)

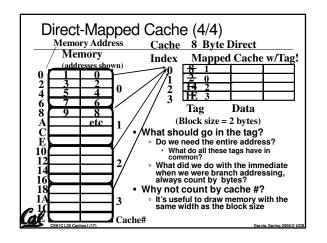

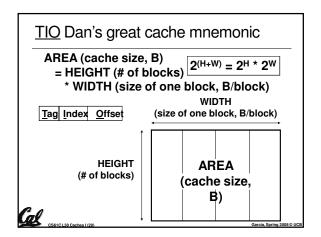

- Tag: use remaining bits as tag

- tag length = addr length offset index

= 32 1 2 bits

= 29 bits

- so tag is leftmost 29 bits of memory address

- Why not full 32 bit address as tag?

Cal

- All bytes within block need same address (4b)

- Index must be same for every address within a block, so it's redundant in tag check, thus can leave off to save memory (here 10 bits)

### And in Conclusion...

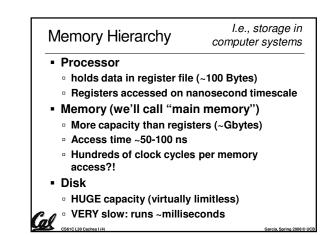

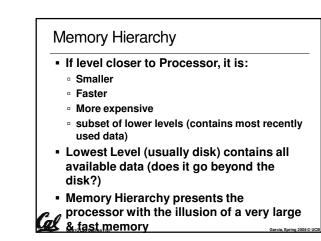

- We would like to have the capacity of disk at the speed of the processor: unfortunately this is not feasible.

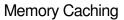

- So we create a memory hierarchy:

- each successively lower level contains "most used" data from next higher level

- exploits temporal & spatial locality

- do the common case fast, worry less about the exceptions (design principle of MIPS)

- Locality of reference is a Big Idea