### **Today**

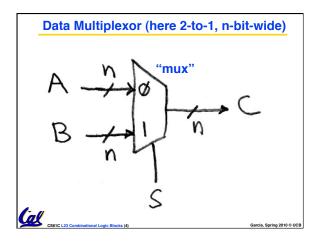

- Data Multiplexors

- Arithmetic and Logic Unit

- Adder/Subtractor

#### **Administrivia**

- · Midterm discussion, moving forward

- If you want a regrade for your midterm, staple a paper with your explanation (clearly indicating on what question you want more points) to your exam and turn it in to your TA in lab this week

- We'll regrade the exam and your score MIGHT go down...

Sarcia, Spring 2010 © L

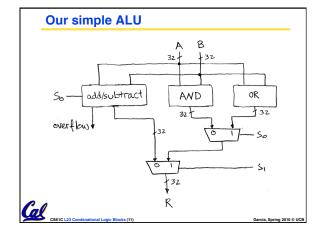

# **Arithmetic and Logic Unit**

- Most processors contain a special logic block called "Arithmetic and Logic Unit" (ALU)

- We'll show you an easy one that does ADD, SUB, bitwise AND, bitwise OR

when S=00, R=A+B when S=01, R=A-B when S=10, R=A AND B when S=11, R=A OR B

Garcia, Spring 2010 © UC

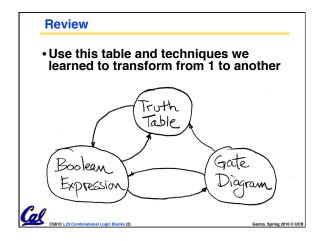

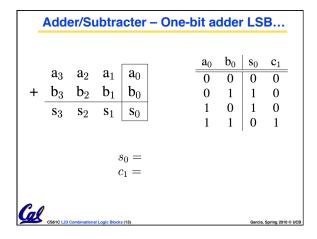

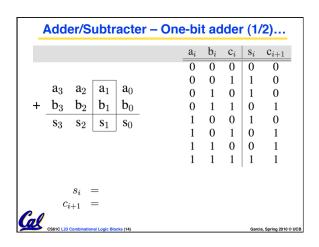

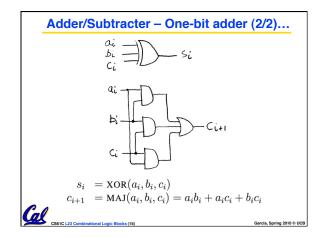

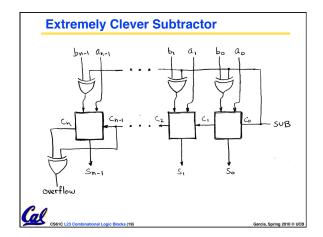

## Adder/Subtracter Design -- how?

- Truth-table, then determine canonical form, then minimize and implement as we've seen before

- Look at breaking the problem down into smaller pieces that we can cascade or hierarchically layer

Garcia, Spring 2010 © UCB

### **Peer Instruction**

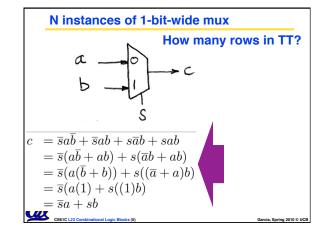

1) Truth table for mux with 4-bits of signals has 24 rows

12 a) FF b) FT c) TF d) TT

2) We could cascade N 1-bit shifters to make 1 N-bit shifter for sll, srl

#### **Peer Instruction Answer**

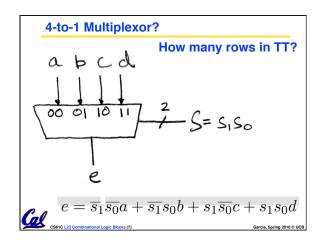

- 1) Truth table for mux with 4-bits of signals controls 16 inputs, for a total of 20 inputs, so truth table is 2<sup>20</sup> rows...FALSE

- 2) We could cascade N 1-bit shifters to make 1 N-bit shifter for sll, srl ... TRUE

- 1) Truth table for mux with 4-bits of signals is 24 rows long

2) We could cascade N 1-bit shifters to make 1 N-bit shifter for sll, srl

(S61C L23 C

## "And In conclusion..."

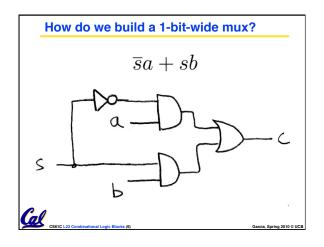

- Use muxes to select among input

- ·S input bits selects 2<sup>S</sup> inputs

- Each input can be n-bits wide, indep of S

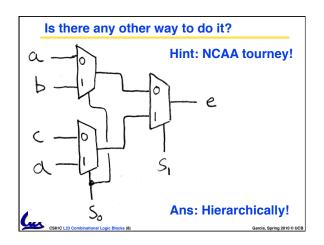

- Can implement muxes hierarchically

- ALU can be implemented using a mux

- · Coupled with basic block elements

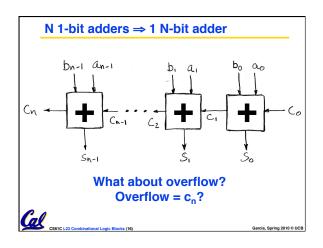

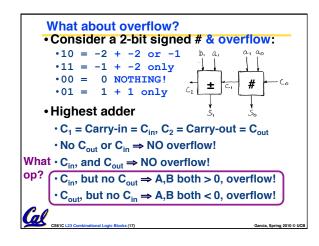

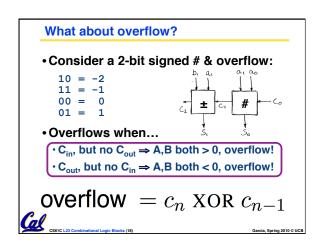

- N-bit adder-subtractor done using N 1-bit adders with XOR gates on input

- · XOR serves as conditional inverter