#### **CS61C Final Review** David Poll, David Jacobs, Michael Le

#### "What's with all these 1s and 0s?" David Jacobs

##

They're a two's complement integer!

"What's with all these 1s and 0s?" 1001 0010 0000 1000 It's negative! 1111 1111 1111 1111 Invert bits and add 1 0110 1101 1111 0111

(-1)x(6x16^7+11x16^6+15x16^5+7x16^4+

**0000 0000 0000 0001** ox16^3+ ox16^2+ ox16^1 + 1x16^o)

They're a floating point number!

#### "What's with all these 1s and 0s?"

$(-1)^{1} \times 20001000111...b \times 2^{(36-127)}$ = -4.323×10^(-28) Expressed in binary

| Exponent | Significand | Object        |

|----------|-------------|---------------|

| 0        | 0           | 0             |

| 0        | nonzero     | Denorm        |

| 1-254    | anything    | +/- fl. pt. # |

| 255      | 0           | +/- ∞         |

| 255      | nonzero     | NaN           |

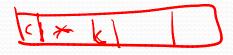

They're a MIPS instruction!

It's an I-type!

According to your green sheet... opcode 36  $\rightarrow$  lbu \$rt, imm(\$rs) \$16 is \$so and \$8 is \$to  $\int_{LO}$ lbu \$so, -1(\$to)

They're 32 separate logical values!

#### "What's with all these 1s and 0s?" The disk isn't I showered today ready to be read. The stove is on Interrupts are enabled

#### If there's one thing you learn...

# N bits can represent 2^N things

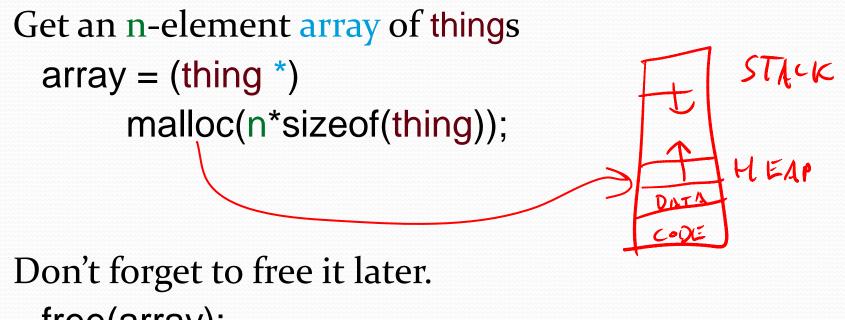

free(array);

#### Problem!

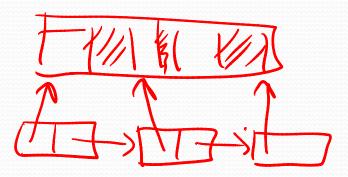

typedef struct node {

int value;

struct node\* next;

} ent;

}

typedef ent \* stack;

int peek(stack s){ l'return value }

stack push(stack s,int val){

1/ reserve space 11 set values 11 return new mode

stack pop(stack s, int \* val){ // change /

}

## Problem!

typedef struct node {

int value;

struct node\* next;

} ent;

```

stack push(stack s,int val){

ent * new = (ent *)

malloc (sizeof(ent));

new->value = val;

new->next = s;

return new;

```

}

```

typedef ent * stack;

int peek(stack s){

return s->value;

}

ent tem,

stack pop(stack s, int * val){

ent * temp = s->next;

*val = s->value;

free(s);

return temp;

}

```

#### Memory Management

- First fit

- Allocate the first available chunk big enough

- Next fit

- Allocate the first chunk after the last one allocated

- Best fit

- Allocate the smallest chunk capable of satisfying the request

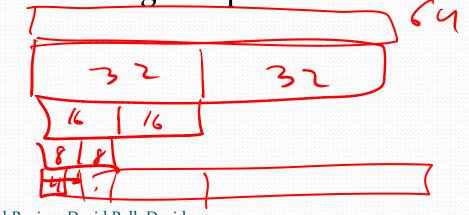

#### Memory Management

- Free List

- Linked list of free chunks, use first/next/best fit

- Slab Allocator

- Fixed number of 2<sup>n</sup> sized chunks, can use a bitmap to track. Free list for larger requests.

- Buddy Allocator

- 2<sup>n</sup> chunks can merge with their "buddy" to make a 2<sup>(n+1)</sup> chunk. Free list for larger requests.

#### Automatic Memory Management

- Reference Counting

- Keep track of pointers to each malloc'd chunk. Free when references = o.

- Mark and Sweep

- Recursively follow "root set" of pointers, marking accessible chunks. Free unreachable chunks in place.

- Copying

- Split memory into two pieces. Mark reachable chunks as above, then copy and defragment into other half.

#### MIPS

Prologue

Body

Epilogue

Sum: addiu \$sp, \$sp, -8 sw \$ra, 0(\$sp) Saved registers sw \$s0, 4(\$sp) add \$s0, \$a0, \$0 Argument registers addiu \$a0, \$a0, -1 jal Sum add \$v0, \$v0, \$s0 Return lw \$s0, 4(\$sp) value lw \$ra, 0(\$sp) addiu \$sp, \$sp, 8 jr \$ra Return address

## Problem! typedef struct node {

int value; // offset 0

Push:

```

struct node* next; //offset 4

} ent;

stack push(stack s, int val){

ent * new = (ent *)

malloc (sizeof(ent));

new->value = val;

new->next = s;

```

return new;

}

```

li $a0, 8

jal malloc

```

```

"I heektties!"

-Dave jr $ra

Fall 2006 CS61C Final Review, David Poll, David

```

Jacobs, Michael Le

#### Problem!

typedef struct node {

int value; // offset 0

struct node\* next; //offset 4

} ent;

stack push(stack s, int val){

ent \* new = (ent \*)

malloc (sizeof(ent));

new->value = val;

new->next = s;

return new;

}

addiu \$sp, \$sp, -12 Push: sw \$ra, 0(\$sp) sw \$a0, 4(\$sp) sw \$a1, 8(\$sp) li \$a0, 8 jal malloc lw \$a0, 4(\$sp) lw \$a1, 8(\$sp) sw \$a0, 4(\$v0) sw \$a1, 0(\$v0) lw \$ra, 0(\$sp) addiu \$sp, \$sp, 12 jr \$ra

# Ok, I get it. But how does it work?!

Michael Le

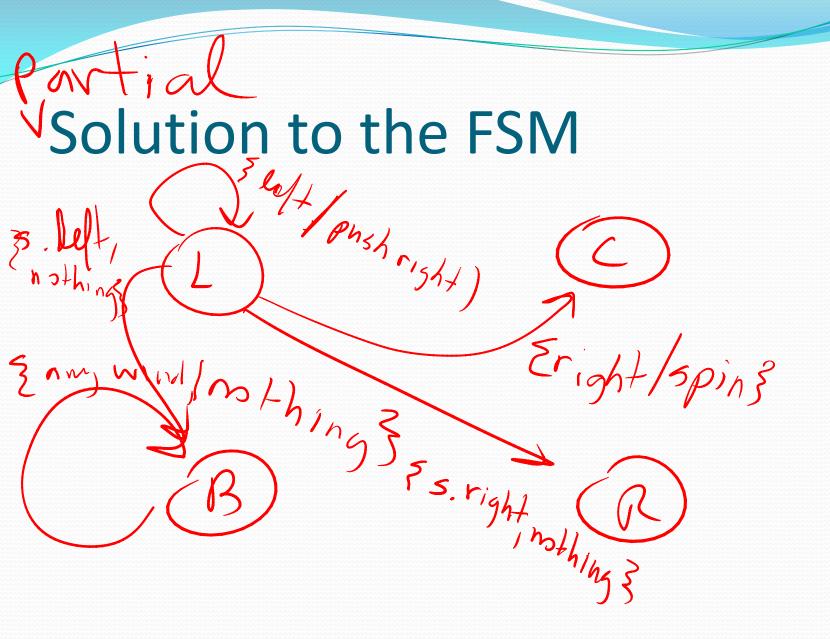

#### Problem

You have been hired to build a plate spinning controller for a robot. The robot can only handle the following orientations of a plate:

#### lean left, balanced, lean right, broken

In addition, there is a wind factor: strong left, left, right, strong right

Depending on the situation, the robot will respond by pushing the plate **left** or **right**, **spin** the plate, or do **nothing**.

How would you begin designing this circuit?

**Finite State Machine**

A general approach to designing one

Identify the states

orientation

Identify the inputs 2.

3.

wind, currorient ation Identify the outputs new orientation, action

run through every seongrio Identify the 4. transitions

#### Finite State Machine A general approach to designing one

**1**. Identify the states

Orientation

2. Identify the inputs

3. Identify the outputs

Identify the transitions

Wind, Current State

**Action**, Next State

Find all possible combos

## **Additional Problem Information**

The robot will respond as follows:

- If the wind is strong, the orientation shifts two steps.

- This means, Left + Strong Left = Broken Plate

- Robot spins plate only when plate returns to the balanced state due to the wind

• Once plate is **broken**, controller does nothing

## What does the FSM look like?

#### <u>Inputs</u>

- CurrentState

- Left, Right, Balance, Broken

- Wind

- Strong Left, Left, Right, Strong Right

#### <u>Outputs</u>

- NextState

- Left, Right, Balance, Broken

- Action

- Push left, spin, push right, do nothing

The robot will respond as follows:

- If the wind is strong, the orientation shifts two steps.

- This means, Left + Strong Left is a Broken Plate

- Robot spins plate only when plate returns to the balanced state due to the wind

- Once plate is broken, controller does nothing

#### What Next?

• Now that we have an FSM, what do we do now?

## **Building Truth Tables**

#### Two general methods

- Running through every combination of the inputs

- If an input/output is multiple bits, break treat each bit as an individual input

- Follow all the transition arcs of your FSM

#### Solution to the Truth Table

State 10 - L 11 - C 01-R 00-B Wind 10 - 5, L11-5,6 20 - L 01-12

|   | Currl | Curr0 | Windl | Wind0 | Nextl | Next0 | Outl | Out/A | 42                          |

|---|-------|-------|-------|-------|-------|-------|------|-------|-----------------------------|

|   | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0     | 0                           |

|   | 0     | 0     | 0     | 1     | 0     | 0     | 0    | 0     |                             |

|   | 0     | 0     | 1     | 0     | 0     | 0     | 0    | 0     | A-1                         |

|   | 0     | 0     | 1     | 1     | 0     | 0     | 0    | 0     |                             |

|   | 0     | 1     | 0     | 0     | 1     | 1     | 1    | 1     | OI-push<br>right<br>10-push |

|   | 0     | 1     | 0     | 1     | 1     | 1     | 1    | 0     | Ol-mal                      |

|   | 0     | 1     | 1     | 0     | 1     | 0     | 0    | 0     | (rws)                       |

|   | 0     | 1     | 1     | 1     | 0     | 0     | 0    | 0     | right                       |

|   | 1     | 0     | 0     | 0     | 1     | 1     | 0    | 1     | 10                          |

|   | 1     | 0     | 0     | 1     | 1     | 1     | 1    | 1     | 10-Dwel                     |

|   | 1     | 0     | 1     | 0     | 0     | 0     | 0    | 0     | 5                           |

|   | 1     | 0     | 1     | 1     | 0     | 1     | 0    | 0     | right<br>12 - Push<br>left  |

| L | 1     | 1     | 0     | 0     | 1     | 0     | 0    | 0     |                             |

|   | 1     | 1     | 0     | 1     | 0     | 1     | 0    | 0     | ) 1-spin                    |

| R | 1     | 1     | 1     | 0     | 0     | 0     | 0    | 0     |                             |

|   | 1     | 1     | 1     | 1     | 0     | 0     | 0    | 0     | 00-nothing                  |

|   |       |       |       |       |       |       |      |       |                             |

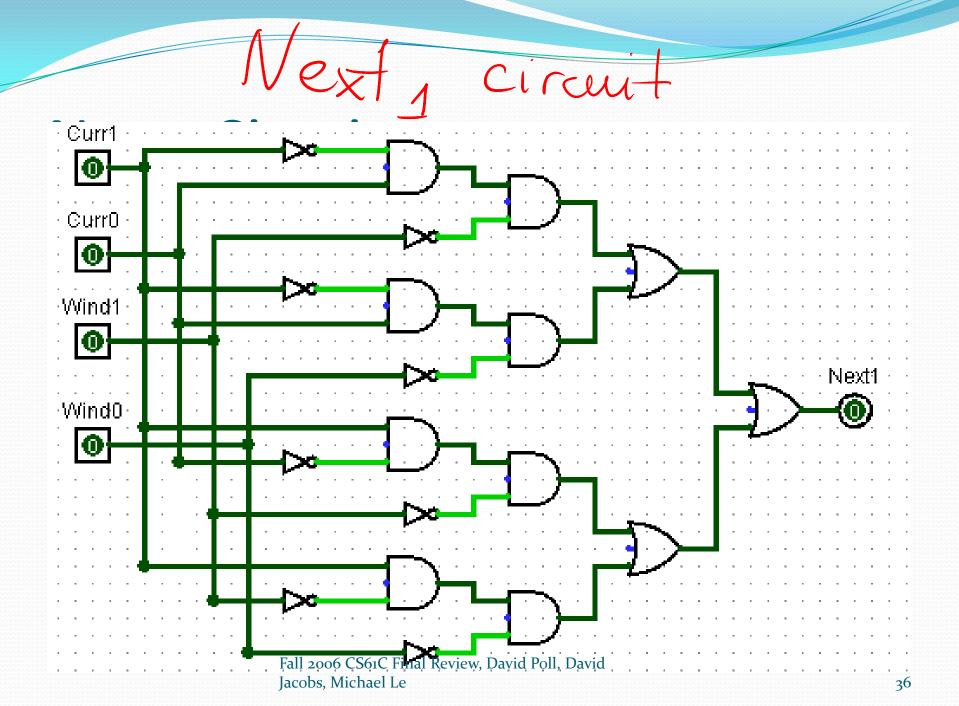

#### Going from Truth Table to Circuit

- Canonical Sums of Products

- For each output, **OR** every combination that produces a true value

- Each combination depends on **AND**'ed inputs

- Commonly known as the Brute-Force method otherwise

- For example, for majority circuit

## ABC ABC ABC $Maj(A,B,C) = A \cdot B + B \cdot C + A \cdot C + A \cdot B \cdot C$

#### **Develop your Expressions**

Using your truth table, determine the expressions for Next<sub>1</sub>, Next<sub>0</sub>, Act<sub>1</sub>, and Act<sub>0</sub>.

#### **Brute Force Result**

$Next_{1} = \overline{C_{1}}C_{0}\overline{W_{1}}\overline{W_{0}} + \overline{C_{1}}C_{0}\overline{W_{1}}W_{0} + \overline{C_{1}}C_{0}W_{1}\overline{W_{0}} + C_{1}\overline{C_{0}}W_{1}\overline{W_{0}} + C_{1}\overline{C_{0}}\overline{W_{1}}W_{0} + C_{1}\overline{C_{0}}\overline{W_{1}}W_{0} + C_{1}C_{0}\overline{W_{1}}\overline{W_{0}} + C_{1}\overline{C_{0}}\overline{W_{1}}\overline{W_{0}} + C_{$

$Next_{0} = \overline{C_{1}}C_{0}\overline{W_{1}}\overline{W_{0}} + \overline{C_{1}}C_{0}\overline{W_{1}}W_{0} + C_{1}\overline{C_{0}}\overline{W_{1}}\overline{W_{0}} + C_{1}\overline{C_{0}}\overline{W_{1}}W_{0} + C_{1}\overline{C_{0}}\overline{W_{1}}W_{0}$

$\operatorname{Act}_{1} = \overline{C_{1}}C_{0}\overline{W_{1}}\overline{W_{0}} + \overline{C_{1}}C_{0}\overline{W_{1}}W_{0} + C_{1}\overline{C_{0}}\overline{W_{1}}W_{0}$

Act<sub>0</sub> =  $\overline{C_1}C_0\overline{W_1}\overline{W_0} + C_1\overline{C_0}\overline{W_1}\overline{W_0} + C_1\overline{C_0}\overline{W_1}W_0$

## **Reflecting on Brute Force**

- Easy, but ugly.

- Sometimes not the optimal solution

- What can we do to get a more elegant result?

#### **Boolean Algebra: Elegant Solution**

Use Boolean Algebra and simplify your expressions!  $x \cdot \overline{x} = 0$  $x + \overline{x} = 1$  $x \cdot 0 = 0$ x + 1 = 1x + 0 = x $x \cdot 1 = x$  $x \cdot x = x$ x + x = x $x \cdot y = y \cdot x$ x + y = y + x(x+y) + z = x + (y+z)(xy)z = x(yz)x(y+z) = xy + xzx + yz = (x + y)(x + z)(x+y)x = xxy + x = x $(x+y) = \overline{x} \cdot \overline{y}$  $\overline{x \cdot y} = \overline{x} + \overline{y}$

complementarity laws of 0's and 1's identities idempotent law commutativity associativity distribution uniting theorem DeMorgan's Law

Elegant Solution

Next<sub>1</sub> =

$$\overline{C_1}C_0\overline{W_1}\overline{W_0} + \overline{C_1}C_0\overline{W_1}W_0 + \overline{C_1}C_0W_1\overline{W_0} + C_1\overline{C_0}\overline{W_1}\overline{W_0} + C_1\overline{C_0}\overline{W_1}W_0 + C_1\overline{C_0}\overline{W_1}\overline{W_0}$$

Next<sub>0</sub> =  $\overline{C_1}C_0\overline{W_1}\overline{W_0} + \overline{C_1}C_0\overline{W_1}W_0 + C_1\overline{C_0}\overline{W_1}\overline{W_0} + C_1\overline{C_0}\overline{W_1}W_0 + C_1\overline{C_0}\overline{W_1}W_0$

Brute Force

\_\_\_\_\_

Simplified

$$\operatorname{Next}_{1} = \overline{C_{1}}C_{0} \overline{W_{1}} + \overline{C_{1}}C_{0} \overline{W_{0}} + C_{1}\overline{C_{0}}\overline{W_{1}} + C_{1}\overline{W_{1}}W_{0}$$

$$\operatorname{Next}_{0} = \overline{C_{1}}C_{0} \overline{W_{1}} + C_{0}\overline{W_{1}}W_{0} + C_{1}\overline{W_{1}}\overline{W_{0}} + C_{1}\overline{C_{0}}W_{0}$$

## **Elegant Solution**

Act

$$_1 = \overline{C_1}C_0\overline{W_1}\overline{W_0} + \overline{C_1}C_0\overline{W_1}W_0 + C_1\overline{C_0}\overline{W_1}W_0$$

Act<sub>0</sub> =

$$\overline{C_1}C_0\overline{W_1}\overline{W_0} + C_1\overline{C_0}\overline{W_1}\overline{W_0} + C_1\overline{C_0}\overline{W_1}W_0$$

Brute Force

Simplified

Act<sub>1</sub> =

$$\overline{C_1}C_0 \overline{W_1} + C_1\overline{C_0}\overline{W_1}W_0$$

Act<sub>0</sub> =  $\overline{C_1}C_0\overline{W_1}\overline{W_0} + C_1\overline{C_0}\overline{W_1}$

#### **Expressions to Gates**

- With your expressions, conversion to gates is mechanical using the sums of products approach

- Each term becomes an AND gate

- Collect the output of the appropriate AND gate into an OR

#### The remaining circuits...

- They are quite trivial and I'm sure you didn't want me to draw them for you

- · Don't forget about registers? - they are used to hold state

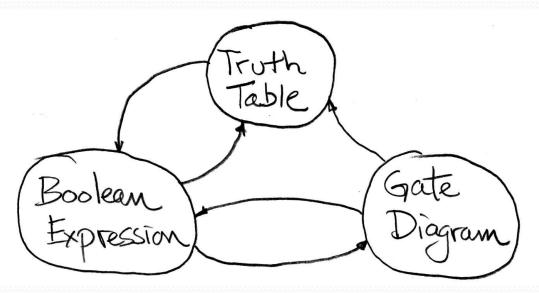

#### **SDS Review**

#### Master SDS is all about mastering the Trifecta<sup>®</sup>

It is possible to transition from any state to any other state. However, the ease of this transition is dependent on the complexity of the problem

# Single Cycle CPU Design

#### Tasks a CPU must do

- Fetch an instruction

- Decode the instruction

- Get values from registers and set control lines

- Execute instruction (arithemetic) A

- Meddle with Memory, if necessary

- Record result of instruction

- a.k.a. register write back

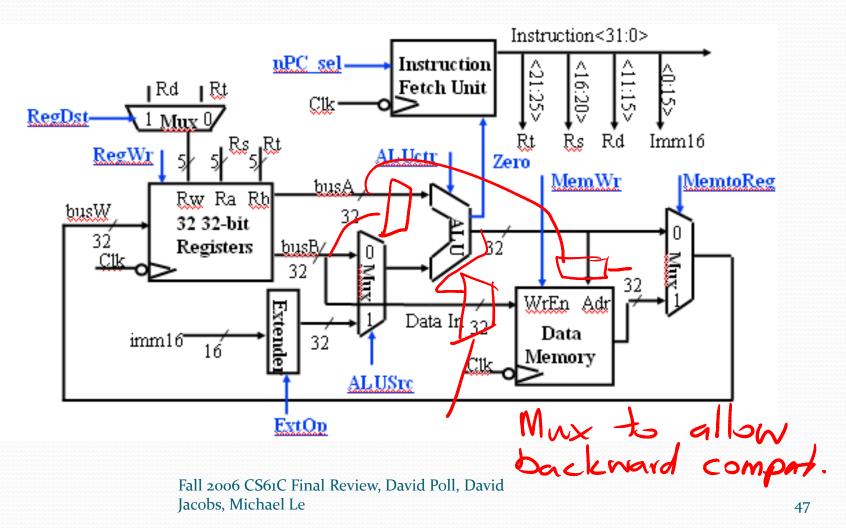

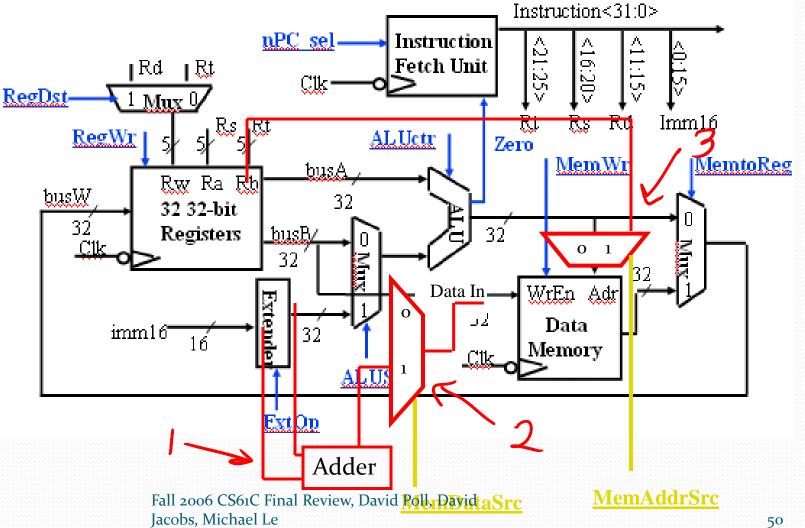

#### Building/Extending a CPU Datapath

- 1. Determine what function you want to do

- I want to support adding of two registers

- 2. Determine what you have to work with

- I have registers, muxes, gates, and lots of wires

- Formulate a plan of bringing data from where it is <sup>★</sup>

found to where it is needed

- I need to move data from registers to an ALU

- **4.** Execute your plan

- 5. Determine Control Signals

# **Applying Those Steps**

#### If I have the following C code:

\*p = z + 4;

#### Converting it to MIPS would produce

addi \$t0, z, 4 sw \$t0, 0(p)

Let's suppose you want to do this in <u>1</u> instruction

#### Step 1 – Determine function

#### Step 1 – Determine function

I want to add two values and store them into memory

#### Step 1 – Determine function

I want to add two values and store them into memory

As a guidance, lets layout what the datapath must do 5 Mem[R[rs]] = R[rt] + SignExtImmedRTL = register + ranslation language

#### Step 2 – Determine what is available

#### Step 2 – Determine what is available

#### Step 3 – Formulate Plan

# Step 3 – Formulate Plan

- 1. Add R[rt] to SignExtImmed

- 2. Send R[rt]+SignExtImmed to Memory Data

- **3**. Send R[rs] to Memory Addr

#### Step 4 – Execute Plan

# Step 5 – Set Control Lines

| Control  | Value                             | Control    | Value |

|----------|-----------------------------------|------------|-------|

| nPC_sel  | normal                            | ExtOp      | Sign  |

| RegDst   | X                                 | MemWr      | 1     |

| RegWrite | 0                                 | MemToReg   | Х     |

| ALUCtrl  | Х                                 | MemDataSrc | 1     |

| ALUSrc   | X<br>Fall 2006 CS6rC Final Review | MemAddrSrc | 1     |

rall 2000 CSOIC Final Keview, David Poll, David

Jacobs, Michael Le

# Things to Keep in Mind

- There is more than one way to modify datapath to produce same result

- If you split a line leading into an input, you need to use a mux.

- Send original line into o

- Send new line into 1

# Pipelining

# **Pipelining Problems**

- Hazards

- Structural: Using some type of circuit two different ways, at the same time

- Data: Instruction depends on result of prior instruction

- Control: Later instruction fetches delayed to wait for result of branch

# **Solving Hazards**

- Structural

- add hardware, use other properties

- Control

- do things earlier such as with branches

- delay slot compromise

- Data

Data • use forwarding, interlocking at worst case

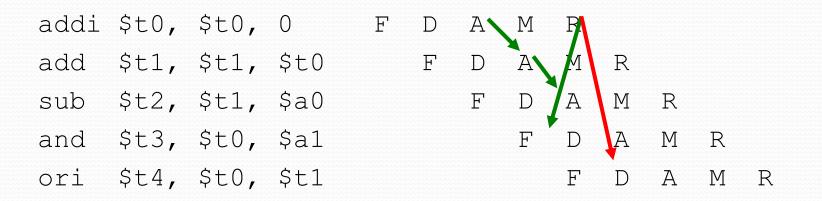

#### **Data Dependencies and Forwarding**

- Data Dependency

- Needing data at decode when updated data has not reached register write back

- Forwarding

- moving data from one stage to another

- Exception is R to D not considered forwarding because no new wire is laid down

because monomorphic forwarding because no

FDAMR

Fall 2006 CS61C Final Review, David Poll, David Jacobs, Michael Le

) is that Forwarding?

wire laid dawn

# Two methods for determining data dependencies and forwarding

- If arrows are drawn starting from end (right side) of R to stage where data is needed in a later instruction, then the arrow represents <u>data</u> <u>dependency</u>

- 2. If arrows are draw starting from when data is first available (right side of stage) to where data is absolutely needed (left side of stage), arrow represents <u>data dependency and forwarding</u> <u>possibility</u>

#### Arrow Drawing Guidelines (for method 2)

- Only draw arrow only if R of updated value of register does not line up on top to the left of D

- Arrows should never span more than 3 instructions (red arrow bad)

# Pitfalls in arrow drawing

- Pay attention to how registers are used

- Not all instructions update registers (i.e. sw)

- Some instructions use registers two different ways

- lw/sw uses one register for address, the other for data

- Method #1 generally has arrows going left

- Arrow going to the right means no data dependency

- Method #2 generally has arrows going right;

- Arrow going to the left for #2 means forwarding won't help; meaning you must stall the pipeline (i.e. do interlock)

### **Branch Delay Slot**

- Any instruction that follows a branch instruction occupies that slot

- That instruction is executed **100%** of the time, unless we have advanced pipelining logic (pipeline flushing, out of order execution, etc).

- Unless we tell you otherwise, there is NO advanced pipeline logic.

### Infamous Example

How many clock cycles would it take to run the following code at left, if the pipelined MIPS CPU had all solutions to control and data hazards as discussed in class (branch delay slot, load interlock, register forwarding)?

|       | addi | \$1,         | \$0,         | 2    |

|-------|------|--------------|--------------|------|

| loop: | add  | \$0,         | \$0,         | \$0  |

|       | beq  | \$1,         | \$0,         | done |

|       | add  | \$4 <b>,</b> | \$3,         | \$2  |

|       | add  | \$5 <b>,</b> | \$4,         | \$3  |

|       | add  | \$6,         | \$5,         | \$4  |

|       | addi | \$1,         | \$1,         | -1   |

|       | beq  | \$0 <b>,</b> | \$0,         | loop |

|       | addi | \$1,         | \$1,         | -1   |

| done: | beq  | \$0,         | \$0,         | exit |

|       | addi | \$1,         | \$0,         | 3    |

| exit: | addi | \$1,         | \$0 <b>,</b> | 1    |

#### Infamous Example

|       | addi | \$1,         | \$0 <b>,</b> | 2    | 1  |     |     |     |     |    |

|-------|------|--------------|--------------|------|----|-----|-----|-----|-----|----|

| loop: | add  | \$0 <b>,</b> | \$0 <b>,</b> | \$0  | 2, | 10  |     |     |     |    |

|       | beq  | \$1,         | \$0 <b>,</b> | done | 3, | 11  |     |     |     |    |

|       | add  | \$4 <b>,</b> | \$3 <b>,</b> | \$2  | 4, | 12  |     |     |     |    |

|       | add  | \$5 <b>,</b> | \$4 <b>,</b> | \$3  | 5  |     |     |     |     |    |

|       | add  | \$6,         | \$5,         | \$4  | 6  |     |     |     |     |    |

|       | addi | \$1,         | \$1,         | -1   | 7  |     |     |     |     |    |

|       | beq  | \$0,         | \$0,         | loop | 8  |     |     |     |     |    |

|       | addi | \$1,         | \$1,         | -1   | 9  |     |     |     |     |    |

| done: | beq  | \$0,         | \$0,         | exit |    | 13  |     |     |     |    |

|       | addi | \$1,         | \$0,         | 3    |    | 14  |     |     |     |    |

| exit: | addi | \$1,         | \$0 <b>,</b> | 1    |    | 15, | 16, | 17, | 18, | 19 |

#### Infamous Example

|       | addi | \$1,         | \$0 <b>,</b> | 2                   | 1     |            |                  |

|-------|------|--------------|--------------|---------------------|-------|------------|------------------|

| loop: | add  | \$0,         | \$0 <b>,</b> | \$0                 | 2,    | 10         |                  |

|       | beq  | \$1,         | \$0,         | done                | З,    | 11         |                  |

|       | add  | \$4 <b>,</b> | \$3 <b>,</b> | \$2                 | 4,    | 12         |                  |

|       | add  | \$5,         | \$4,         | \$3                 | 5     |            | <b>7</b> 1       |

|       | add  | \$6,         | \$5,         | \$4                 | 6     |            | <b>19 Cycles</b> |

|       | addi | \$1,         | \$1 <b>,</b> | -1                  | 7     |            |                  |

|       | beq  | \$0,         | \$0,         | loop                | 8     |            |                  |

|       | addi | \$1,         | \$1,         | -1                  | 9     |            |                  |

| done: | beq  | \$0,         | \$0,         | exit                |       | 13         |                  |

|       | addi | \$1,         | \$0,         | 3                   |       | 14         |                  |

| exit: | addi | \$1,         | \$0,         | 1                   |       | 15,        | 16, 17, 18, 19   |

|       |      |              |              | Pipeline Dra        | ain – |            |                  |

|       |      | F            | all 2006 (   | CS61C Final Review, | David | Poll, Davi | d                |

Jacobs, Michael Le

# **More Pipelining Practice**

loop:

[4]

[1] add \$a0, \$a0, \$t1

[2] lw \$a1, 0(\$a0) [3] add \$a1, \$a1, \$t1

[5] add \$t1, \$t1, -1

[6] bne \$0, \$0, end

[7] add \$t9, \$t9, 1

sw \$a1, 0(\$t1)

- How many cycles are needed to execute the following code:

- CPU has

- no forwarding units

- will interlock on any hazard

- no delayed branch

- 2nd stage branch compare

- instructions are not fetched until compare happens

- memory CAN be read/written on the same cycle

- same registers CAN be read/written on the same cycle

#### More Pipelining Practice

|     |   |   |   |   |   |   |   |   | Ρ |   |   |   |   | - |   |   |   |          |  |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------|--|

|     |   |   |   |   |   |   |   |   |   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1        |  |

|     | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 0 | 1 | 2 | З | 4 | 5 | 6 | 7 | 8        |  |

| [1] | F | D | A | M | R |   |   |   |   |   |   |   |   |   |   |   |   |          |  |

| [2] |   | F | D | D | D | A | M | R |   |   |   |   |   |   |   |   |   |          |  |

| [3] |   |   | F |   |   |   |   | D | A | M | R |   |   |   |   |   |   |          |  |

| [4] |   |   |   |   |   |   |   | F |   |   | D | A | М | R |   |   |   |          |  |

| [5] |   |   |   |   |   |   |   |   |   |   | F | D | Α | М | R |   |   |          |  |

| [6] |   |   |   |   |   |   |   |   |   |   |   | F | D | А | М | R |   |          |  |

| [7] |   |   |   |   |   |   |   |   |   |   |   |   |   | F | D | A | M | $ _{R} $ |  |

### **More Pipelining Practice**

loop:

[2]

[3]

[4]

[5]

[6]

[7]

[1]

add \$a0, \$a0, \$t1

add \$a1, \$a1, \$t1

lw \$a1, 0(\$a0)

sw \$a1, 0(\$t1)

add \$t1, \$t1, -1

bne \$0, \$0, end

add \$t9, \$t9, 1

- How many cycles are needed to execute the following code:

- CPU has

- all forwarding units

- will interlock on any hazard

- delayed branch

- 2nd stage branch compare

memory CAN be read/written on the same cycle

- same registers CAN be read/written on the same cycle

| Mo  | re | ן ב | Pi | p | e | lir | hi | n            | bD | P | ra | C | tice |

|-----|----|-----|----|---|---|-----|----|--------------|----|---|----|---|------|

|     |    |     |    |   |   |     |    |              |    | 1 | 1  | 1 |      |

|     | 1  | 2   | 3  | 4 | 5 | 6   | 7  | 8            | 9  | 0 | 1  | 2 |      |

| [1] | F  | D   | A  | M | R |     |    |              |    |   |    |   |      |

| [2] |    | F   | D  | A | M | R   |    |              |    |   |    |   |      |

| [3] |    |     | F  |   | D | A   | M  | R            |    |   |    |   |      |

| [4] |    |     |    |   | F | D   | A  | M            | R  |   |    |   |      |

| [5] |    |     |    |   |   | F   | D  | A            | M  | R |    |   |      |

| [6] |    |     |    |   |   |     | F  | D            | A  | М | R  |   |      |

| [7] |    |     |    |   |   |     |    | <sub>F</sub> | D  | A | M  | R |      |

# What else?

David Poll

### Example

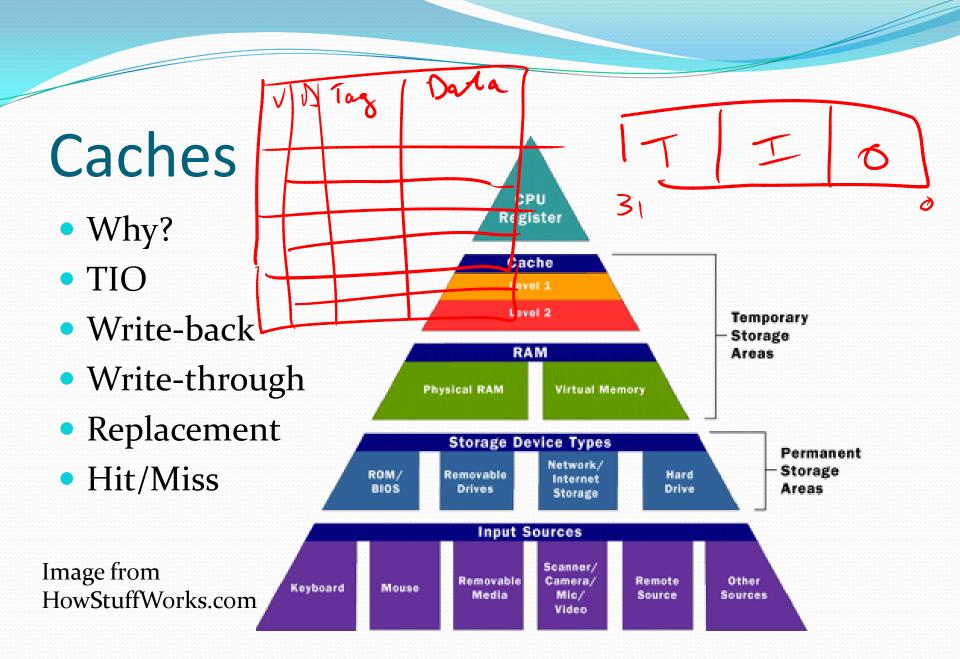

#### VM

Cache

Fall 2006 CS61C Final Review, David Poll, David Jacobs, Michael Le

Index

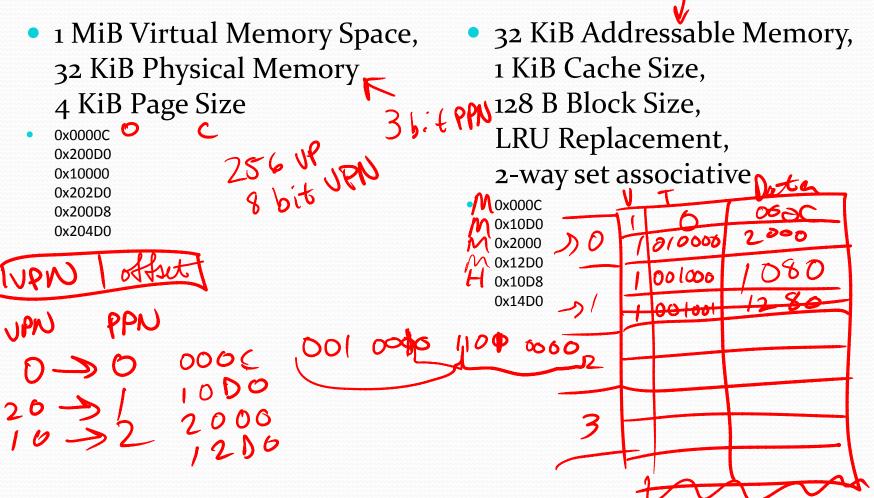

# VM

- Why?

- VPN vs. PPN

- Page Fault

- Page in, Page out

# VM/Caches

- What happens when we switch processes?

- Problem with Page Tables? (where are they?)

- AMAT

- AMAT = Hit Time + (Miss %) x (AMAT for Miss)

- Give an expression for AMAT of a system with VM (with TLB) and Cache

#### Performance

- CPU Time (CPI)

- Example:

- Memory Read 10%, CPI = 18 🌫 1, 8

- Memory Write 15%, CPI = 20 3,0

- ALU 30%, CPI = 1

- Branch 45%, CPI = 2

- Overall CPI?

- CPU Speed = 1 GHz, 1 Million instructions, CPU Time?

- Cache added. Memory Read/Write halved. Improvement?

pms . Time

les/instruction

- Megahertz Myth

- What determines performance?

# 1/0

- Polling

- Are we there yet?

- Interrupts

- Wake me when we get there.

- Memory Mapped I/O

#### Networks

- Sharing vs. Switching

- Half-duplex vs. Full-duplex

- Packets

- Header

- Payload

- Trailer

- Ack?

- TCP/IP

#### Packet - E-mail Example

| Header  | Sender's IP address<br>Receiver's IP address<br>Protocol<br>Packet number | 96 bits  |  |  |  |  |

|---------|---------------------------------------------------------------------------|----------|--|--|--|--|

| Payload | Data                                                                      | 896 bits |  |  |  |  |

| Trailer | Data to show end<br>of packet<br>Error correction                         | 32 bits  |  |  |  |  |

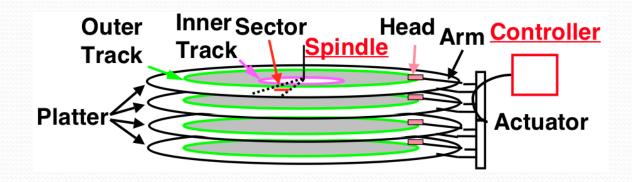

### Disks

- Latency:

- Seek Time + Rotation Time + Transfer Time + Controller Overhead

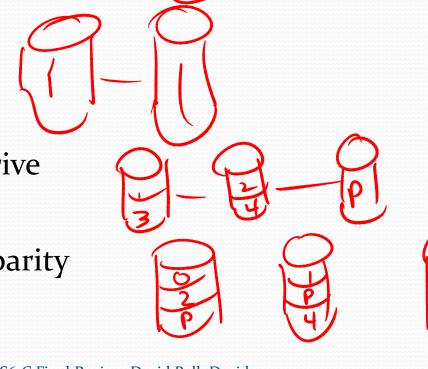

### RAID

- RAID-o

- Striped

- RAID-1

- Mirrored

- RAID-4

- Striped, parity drive

- RAID-5

- Striped, striped parity

### Parallelization

- Why?

- Distributed Computing

- Parallel Processing

- Amdahl's law

- Time >= s + 1/p

- Speedup <= 1/s

# Conclusion

Questions on the Sp-04 Final?