## Today

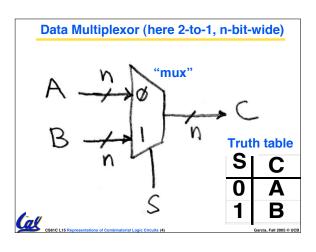

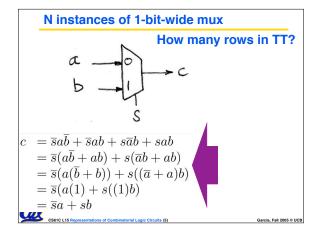

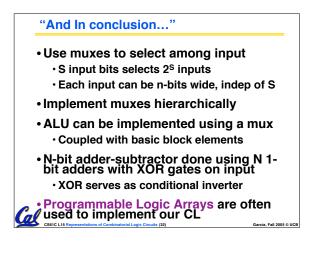

- Data Multiplexors

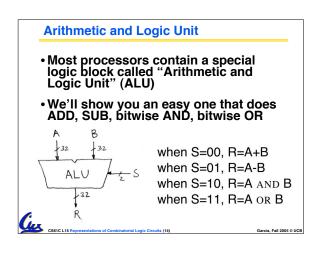

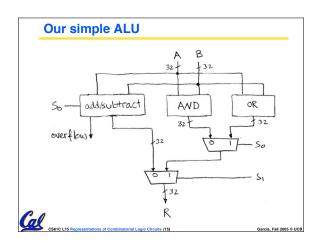

- Arithmetic and Logic Unit

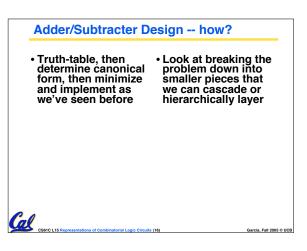

- Adder/Subtractor

Cal

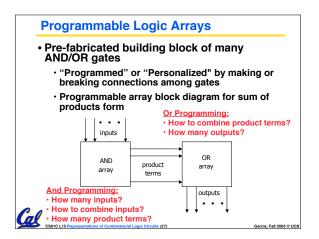

Programmable Logic Arrays

Garcia, Fall 2005 © UCB

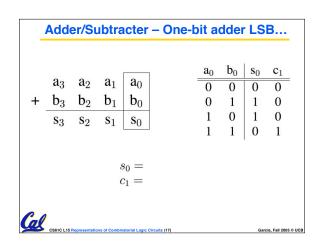

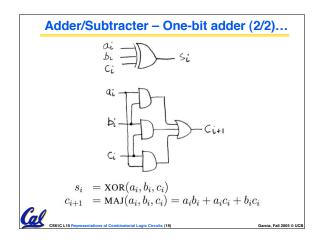

| Adder/Subtracter – One-bit adder (1/2) |            |                       |                |                                |                       |                |    |    |                   |

|----------------------------------------|------------|-----------------------|----------------|--------------------------------|-----------------------|----------------|----|----|-------------------|

|                                        |            |                       |                |                                | <u>a</u> <sub>i</sub> | b <sub>i</sub> | ci | Si | $c_{i+1}$         |

|                                        |            |                       |                |                                | 0                     | 0              | 0  | 0  | 0                 |

|                                        | $a_3$      | $a_2$                 | $a_1$          | $a_0$                          | 0                     | 0              | 1  | 1  | 0                 |

|                                        |            | _                     | 1              |                                | 0                     | 1              | 0  | 1  | 0                 |

| +                                      | $b_3$      | $b_2$                 | $b_1$          | $\mathbf{b}_0$                 | 0                     | 1              | 1  | 0  | 1                 |

|                                        | <b>S</b> 3 | <b>S</b> <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub>                 | 1                     | 0              | 0  | 1  | 0                 |

|                                        | ~0         | -2                    | -1             | 20                             | 1                     | 0              | 1  | 0  | 1                 |

|                                        |            |                       |                |                                | 1                     | 1              | 0  | 0  | 1                 |

|                                        |            |                       |                |                                | 1                     | 1              | 1  | 1  | 1                 |

|                                        |            | $s_i$                 | _              |                                |                       |                |    |    |                   |

| , _                                    |            | +1                    | =              |                                |                       |                |    |    |                   |

| Ľ                                      | CS61C   15 |                       |                | pinatorial Logic Circuits (18) |                       |                |    | ~  | rcia. Fall 2005 @ |

Garcia, Fall 2005 © UCE

|    | Peer Instruction                                                     |                |                   |

|----|----------------------------------------------------------------------|----------------|-------------------|

|    |                                                                      |                |                   |

|    |                                                                      |                |                   |

|    |                                                                      |                |                   |

| Α. | SW can peek at HW (past ISA abstraction boundary) for optimizations  | 1:             | ABC<br>FFF        |

| В. | SW can depend on particular HW<br>implementation of ISA              | 2:<br>3:<br>4: | FFT<br>FTF<br>FTT |

| C. | Timing diagrams serve as a critical debugging tool in the EE toolkit | 5:<br>6:       | TFF<br>TFT        |

| Ca | C551C L15 Representations of Combinatorial Logic Circuits (33)       | 7:<br>8:       |                   |

| _  | Peer Instruction                                                                                 |      |            |

|----|--------------------------------------------------------------------------------------------------|------|------------|

|    |                                                                                                  |      |            |

|    |                                                                                                  |      |            |

|    |                                                                                                  |      |            |

| Δ. | HW feedback akin to SW recursion                                                                 |      | ABC        |

| _  |                                                                                                  | 1:   | FFF<br>FFT |

|    | We can implement a D-Q flipflop<br>as simple CL (And, Or, Not gates)                             | 3:   | FTF        |

|    | as simple $OL$ (And, $OI$ , Not gates)                                                           | 4:   | FTT<br>TFF |

| C. |                                                                                                  |      | 122        |

|    | You can build a FSM to signal                                                                    | 6:   | TFT        |

|    | You can build a FSM to signal<br>when an equal number of 0s and<br>1s has appeared in the input. | 1.2. | TFT<br>TTF |

|    | Peer Instruction                                                      |           |                |

|----|-----------------------------------------------------------------------|-----------|----------------|

|    |                                                                       |           |                |

|    |                                                                       |           |                |

|    |                                                                       |           |                |

|    |                                                                       |           |                |

| Α. | (a+b)• (ā+b) = b                                                      | 1.        | ABC            |

| В. | N-input gates can be thought of cascaded 2-                           | 2:        | FFF            |

|    | input gates. I.e.,                                                    | 2:        | FTF            |

|    | $(a \Delta bc \Delta d \Delta e) = a \Delta (bc \Delta (d \Delta e))$ | Δ·        | FTT            |

|    | where $\Delta$ is one of AND, OR, XOR, NAND                           | 5 :       | TFF            |

| C. | You can use NOR(s) with clever wiring to                              | 6:        | TFT            |

|    | simulate AND, OR, & NOT                                               | 7:        | TTF            |

| (a | /                                                                     | 8:        | TTT            |

| 1  | S CS61C L15 Representations of Combinatorial Logic Circuits (36)      | Garcia, F | all 2005 © UCB |

|          | Peer Instruction                                                    |          |                 |

|----------|---------------------------------------------------------------------|----------|-----------------|

|          |                                                                     |          |                 |

|          |                                                                     |          |                 |

|          |                                                                     |          |                 |

|          |                                                                     |          |                 |

|          |                                                                     |          |                 |

|          |                                                                     |          |                 |

| Α.       | Truth table for mux with 4-bits of                                  | 1.       | ABC             |

|          | signals has 2 <sup>4</sup> rows                                     | 2:       | FFT             |

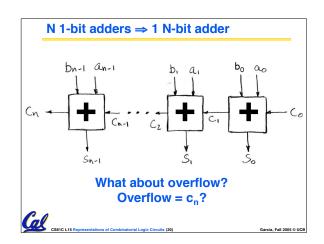

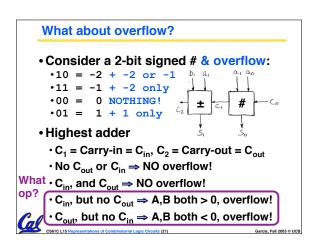

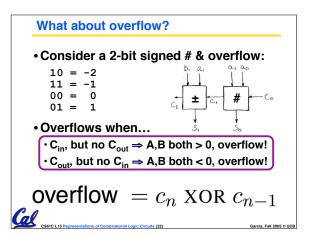

| В.       | We could cascade N 1-bit shifters                                   | 3:       | FTF<br>FTT      |

|          | to make 1 N-bit shifter for sll, srl                                | 4:<br>5: | TFF             |

| c        | If 1-bit adder delay is T the N-bit                                 | 6:       | TFT             |

| <u>،</u> | If 1-bit adder delay is T, the N-bit<br>adder delay would also be T | 7:       | TTF<br>TTT      |

| _        | CS61C L15 Representations of Combinatorial Logic Circuits (40)      | Garcia,  | Fall 2005 © UCB |