#### **Review**

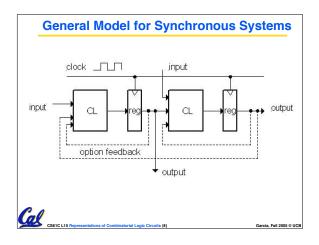

- We use feedback to maintain state

- Register files used to build memories

- D-FlipFlops used to build Register files

- Clocks tell us when D-FlipFlops change

- · Setup and Hold times important

- TODAY

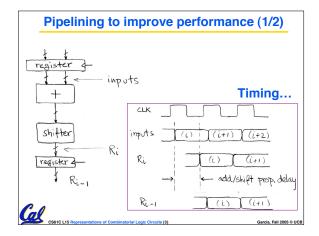

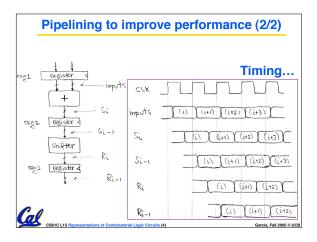

- Technique to be able to increase clock speed

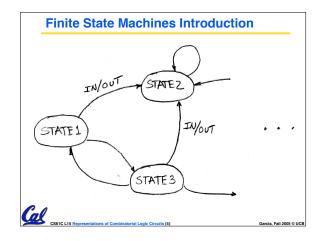

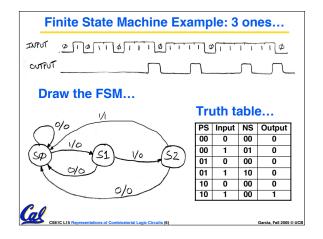

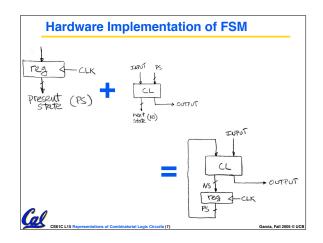

- · Finite State Machines

- · Representation of CL Circuits

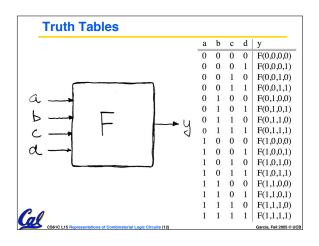

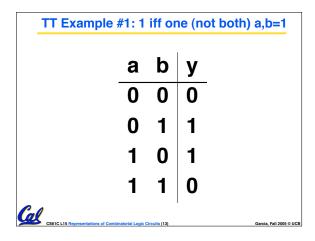

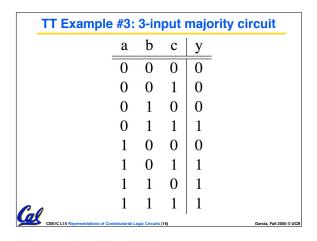

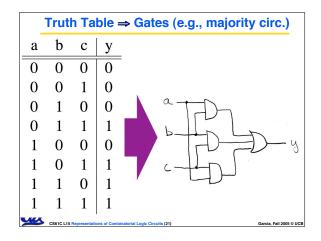

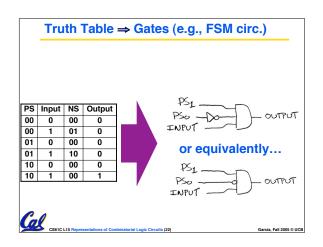

- Truth Tables

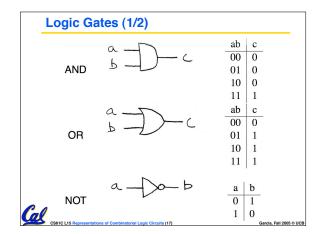

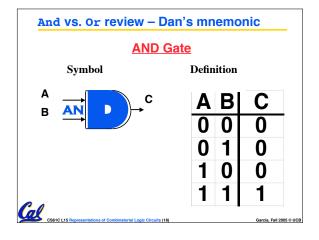

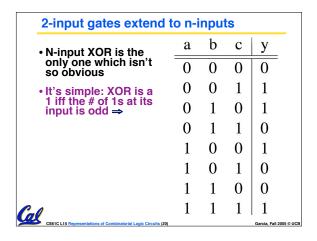

- Logic Gates

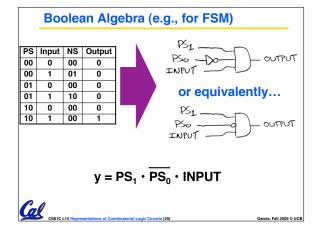

- Boolean Algebra

Garcia, Fall 2005 © I

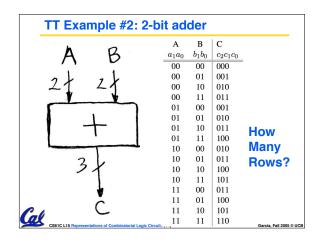

|   | TT Example #3: 32-bit unsigned adder |                                 |                         |  |  |

|---|--------------------------------------|---------------------------------|-------------------------|--|--|

|   | A                                    | В                               | C                       |  |  |

| ' | 000 0                                | 000 0                           | 000 00                  |  |  |

|   | 000 0                                | 000 1                           | 000 01                  |  |  |

|   | •                                    | •                               | · How                   |  |  |

|   |                                      |                                 | Many<br>Rows?           |  |  |

|   | •                                    | •                               | •                       |  |  |

|   | 111 1                                | 111 1                           | 111 10                  |  |  |

| G | CS61C L15 Representations of Com     | nbinatorial Logic Circuits (15) | Garcia, Fall 2005 ⊗ UCB |  |  |

| Logic Ga                 | Logic Gates (2/2)                        |                |                         |  |  |

|--------------------------|------------------------------------------|----------------|-------------------------|--|--|

| XOR                      | a — ) — c                                | ab 00          | 0                       |  |  |

| XOR                      |                                          | 01<br>10<br>11 | 1<br>1<br>0             |  |  |

| NAND                     | a -Do-c                                  | ab<br>00<br>01 | 1<br>1                  |  |  |

| NAIND                    |                                          | 10<br>11       | 1 1 0                   |  |  |

|                          | a                                        | ab 00          | <u>c</u>                |  |  |

| NOR                      |                                          | 01<br>10<br>11 | 0 0 0                   |  |  |

| CS61C L15 Representation | ons of Combinatorial Logic Circuits (19) | 11             | Garcia, Fall 2005 © UCB |  |  |

### **Boolean Algebra**

- George Boole, 19<sup>th</sup> Century mathematician

- Developed a mathematical system (algebra) involving logic

- · later known as "Boolean Algebra"

- Primitive functions: AND, OR and NOT

- The power of BA is there's a one-to-one correspondence between circuits made up of AND, OR and NOT gates and equations in BA

- + means OR,• means AND, x means NOT

Boolean Algebra (e.g., for majority fun.)  $y = a \cdot b + a \cdot c + b \cdot c$  y = ab + ac + bc

## **Laws of Boolean Algebra**

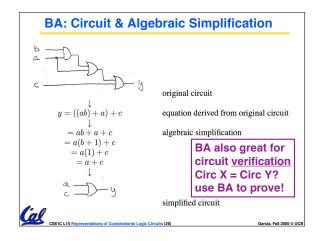

## **Boolean Algebraic Simplification Example**

$$y = ab + a + c$$

=  $a(b+1) + c$  distribution, identity

=  $a(1) + c$  law of 1's

=  $a + c$  identity

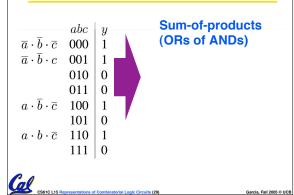

## Canonical forms (1/2)

# Canonical forms (2/2)

$$y = \overline{a}\overline{b}\overline{c} + \overline{a}\overline{b}c + a\overline{b}\overline{c} + ab\overline{c}$$

$$= \overline{a}\overline{b}(\overline{c} + c) + a\overline{c}(\overline{b} + b) \qquad distribution$$

$$= \overline{a}\overline{b}(1) + a\overline{c}(1) \qquad complementarity$$

$$= \overline{a}\overline{b} + a\overline{c} \qquad identity$$

#### "And In conclusion..."

Cal

- Pipeline big-delay CL for faster clock

- Finite State Machines extremely useful · You'll see them again in 150, 152 & 164

- Use this table and techniques we learned to transform from 1 to another