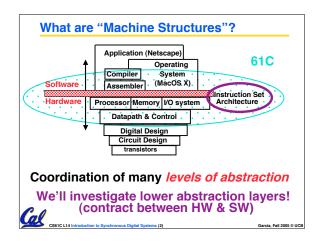

### **Logic Design**

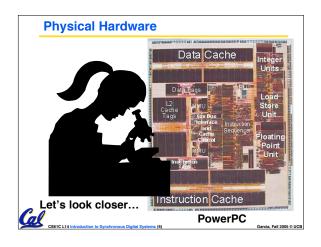

- Next 2 weeks: we'll study how a modern processor is built starting with basic logic elements as building blocks.

- Why study logic design?

- Understand what processors can do fast and what they can't do fast (avoid slow things if you want your code to run fast!)

- Background for more detailed hardware courses (CS 150, CS 152)

Samia Eall 2005 © HC

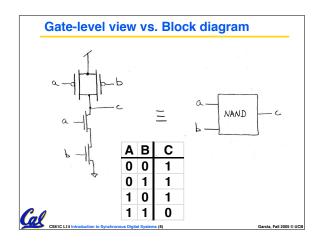

### **Logic Gates**

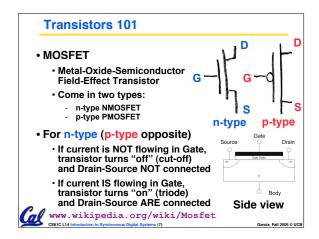

- Basic building blocks are logic gates.

- In the beginning, did ad hoc designs, and then saw patterns repeated, gave names

- Can build gates with transistors and resistors

- Then found theoretical basis for design

- Can represent and reason about gates with truth tables and Boolean algebra

- Assume know truth tables and Boolean algebra from a math or circuits course.

- · Section B.2 in the textbook has a review

### **Combinational Logic**

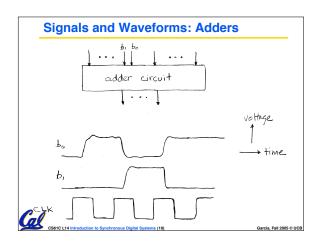

- Complex logic blocks are built from basic AND, OR, NOT building blocks we'll see shortly.

- A combinational logic block is one in which the output is a function only of its current input.

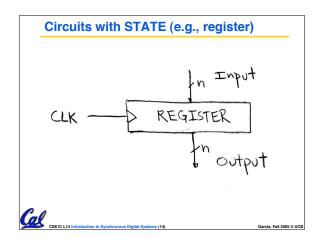

- Combinational logic cannot have memory (e.g., a register is not a combinational unit).

### And in semi conclusion...

- •ISA is very important abstraction layer

- Contract between HW and SW

- Basic building blocks are logic gates

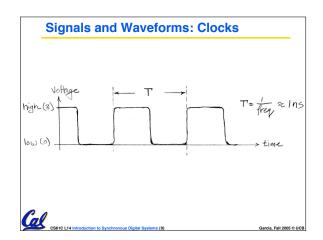

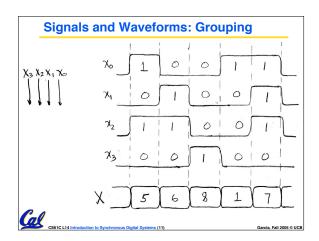

- Clocks control pulse of our circuits

- Voltages are analog, quantized to 0/1

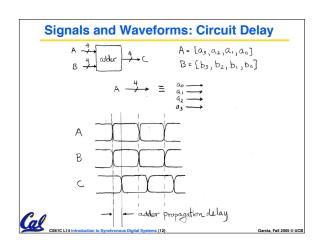

- · Circuit delays are fact of life

- Two types

- Stateless Combinational Logic (&,I,~)

- State circuits (e.g., registers)

# Administrivia - Midterm 2005Sp Your TAs and readers stayed up until 4am to get your exams back to you! • x̄: 47, Median: 48, σ: 14.4 UCB CS61C 2005Sp Midterm mean=47, median=48, stdev=14

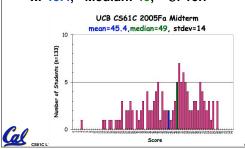

# Administrivia - Midterm 2005Fa

- Your TAs and readers stayed up until 4am to get your exams back to you!

- $\bar{x}$ : 45.4, Median: 49,  $\sigma$ : 13.7

### **Administrivia**

- If you want an exam regrade, simply staple a note to the front of your exam and turn it in to your TA or Dan.

- · We'll collect them until the end of Monday's lecture and then regrade all.

- · Remember that your grade can go down.

- Project 1 is graded; you have one week to request a regrade there too...

## "And In conclusion..."

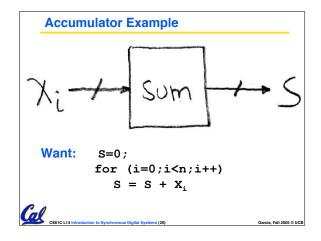

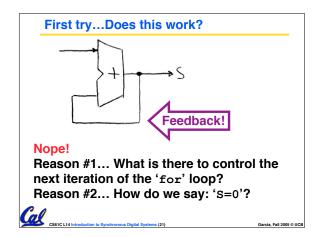

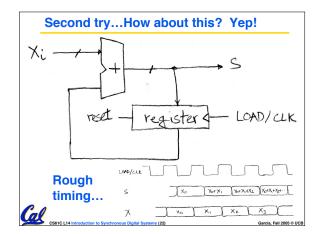

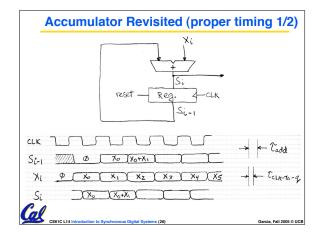

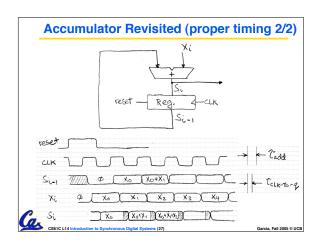

- We use feedback to maintain state

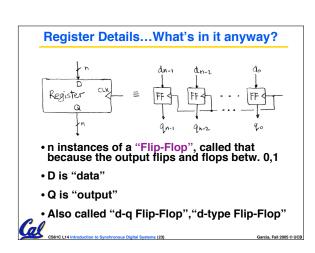

- Register files used to build memories

- D-FlipFlops used to build Register files

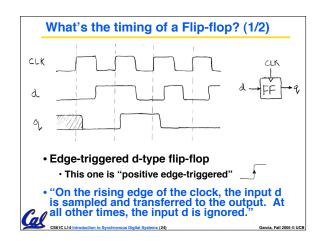

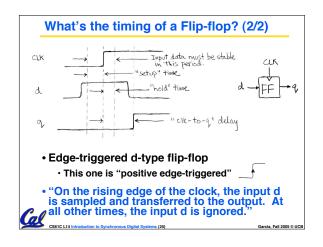

- Clocks tell us when D-FlipFlops change

- · Setup and Hold times important

CS81C L14 Introduction to Synchronous Digital Systems (28)

Garcia, Fall 2005 © U