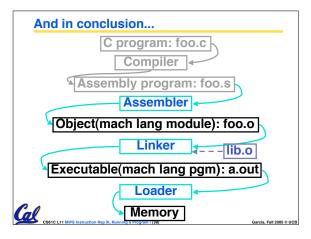

- How do we convert 1s and 0s to C code?

Machine language ⇒ C?

- For each 32 bits:

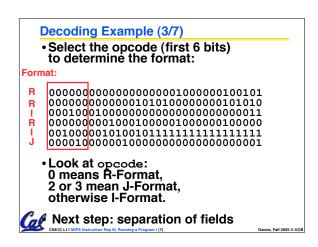

- Look at opcode: 0 means R-Format, 2 or 3 mean J-Format, otherwise I-Format.

- Use instruction type to determine which fields exist.

- Write out MIPS assembly code, converting each field to name, register number/name, or decimal/hex number.

• Logically convert this MIPS code into valid C code. Always possible? Unique?

# Decoding Example (1/7)

a

al

- Here are six machine language

instructions in hexadecimal:

- $\begin{array}{c} 00001025_{hex} \\ 0005402A_{hex} \\ 11000003_{hex} \\ 00441020_{hex} \\ 20A5FFFF_{hex} \\ 08100001_{hex} \end{array}$

• Let the first instruction be at address  $4,194,304_{ten}$  (0x00400000<sub>hex</sub>).

Next step: convert hex to binary

##

Next step: identify opcode and format

| R   | 0                     | rs                    | rt                 | rd     | shamt  | funct            |

|-----|-----------------------|-----------------------|--------------------|--------|--------|------------------|

| I   | 1, 4-31               | rs                    | rt                 | ir     | nmedia | te               |

| J   | 2 or 3                |                       | targe              | et add | ress   |                  |

| Cal | CS61C L11 MIPS Instru | uction Rep III, Runni | ng a Program I (6) |        |        | Garcia, Fall 200 |

### **Decoding Example (4/7)**

• Fields separated based on format/opcode: Format:

| R  | 0 | 0 | 0 | 2      | 0  | 37 |

|----|---|---|---|--------|----|----|

| R  | 0 | 0 | 5 | 8      | 0  | 42 |

| I. | 4 | 8 | 0 |        | +3 |    |

| R  | 0 | 2 | 4 | 2      | 0  | 32 |

| L  | 8 | 5 | 5 |        | -1 |    |

| J  | 2 |   | 1 | ,048,5 | 77 |    |

Next step: translate ("disassemble") to MIPS assembly instructions

Garcia, Fall 2005 © UCB

ning a Program I (8)

| Decoding Exam                                                                    | ple (5/7)                            | )                                                                                |                         |

|----------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------|-------------------------|

| MIPS Assemb                                                                      | ly (Part <sup>·</sup>                | 1):                                                                              |                         |

| Address:                                                                         | Assen                                | nbly instruction                                                                 | ons:                    |

| 0x00400000<br>0x00400004<br>0x00400008<br>0x0040000c<br>0x00400010<br>0x00400014 | or<br>slt<br>beq<br>add<br>addi<br>j | \$2,\$0,\$0<br>\$8,\$0,\$5<br>\$8,\$0,3<br>\$2,\$2,\$4<br>\$5,\$5,-1<br>0x100001 |                         |

| <ul> <li>Better solution<br/>meaningful MI<br/>branch/jump a</li> </ul>          | PS instr                             | uctions (fix                                                                     | the<br>ters)            |

| CS61C L11 MIPS Instruction Rep III, Running                                      | g a Program I (9)                    |                                                                                  | Garcia, Fall 2005 © UCB |

| Decoding Ex                    | ample ( | 6/7)                           |                         |

|--------------------------------|---------|--------------------------------|-------------------------|

| • MIPS Asser                   | mbly (P | art 2):                        |                         |

| Loop:                          | addi    | \$v0,\$v0,\$a0<br>\$a1,\$a1,-1 |                         |

| Exit:                          | j       | Loop                           |                         |

| • Next step: 1<br>(be creative | e!)     |                                | Garcia, Fall 2005 ⊕ UCB |

| -                                 |                                       |                                                                                      |                                                                                              |

|-----------------------------------|---------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Before<br>00001<br>00054<br>11000 | .025 <sub>h</sub><br>02A <sub>h</sub> | \$v0:<br>** \$a0:<br>** \$a1:                                                        | code (Mapping below)<br>product<br>multiplicand<br>multiplier                                |

| 00441<br>20A5E<br>08100           | .020 <sub>h</sub>                     | product<br>** while (<br>** prod                                                     | <pre>:= 0;<br/>multiplier &gt; 0) {<br/>huct += multiplicand;<br/>iplier -= 1;</pre>         |

|                                   | beq                                   | <pre>\$v0,\$0,\$0 \$t0,\$0,\$a1 \$t0,\$0,Exit \$v0,\$v0,\$a0 \$a1,\$a1,-1 Loop</pre> | Demonstrated Big 61C<br>Idea: Instructions are<br>just numbers, code is<br>treated like data |

| Exit:                             |                                       |                                                                                      |                                                                                              |

| • | Project 2 due Wednesday (ok, Friday)                                                                                                                               |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Midterm 2005-10-17 @ 5:30-8:30pm Here!                                                                                                                             |

| • | Covers labs,hw,proj,lec up through 7th wk                                                                                                                          |

| • | Prev sem midterm + answers on HKN                                                                                                                                  |

| • | Bring                                                                                                                                                              |

|   | NO backpacks, cells, calculators, pagers, PDAs                                                                                                                     |

|   | <ul> <li>2 writing implements (we'll provide write-in<br/>exam booklets) – pencils ok!</li> </ul>                                                                  |

|   | One handwritten (both sides) 8.5"x11" paper                                                                                                                        |

|   | <ul> <li>One green sheet (corrections below to bugs<br/>from "Core Instruction Set")</li> </ul>                                                                    |

|   | <ol> <li>Opcode wrong for Load Word.<br/>It should say 23hex, not 0 / 23hex.</li> </ol>                                                                            |

|   | <pre>2) sll and srl should shift values in R[rt], not R[rs]<br/>i.e. sll/srl:R[rd] = R[rt] &lt;&lt; shamt<br/>Sticitit MPS hearders Rep. Manuage Program (J)</pre> |

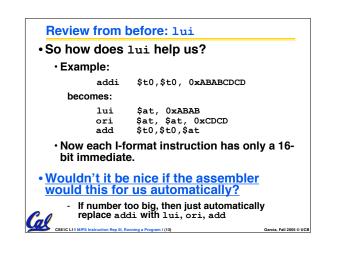

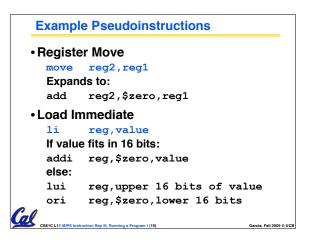

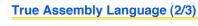

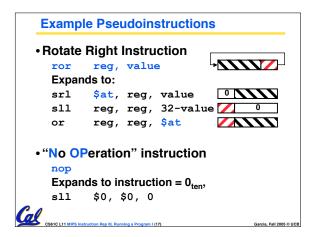

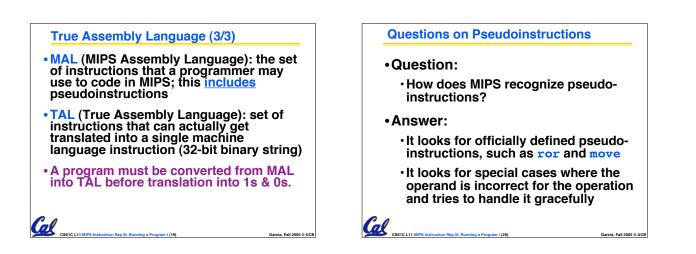

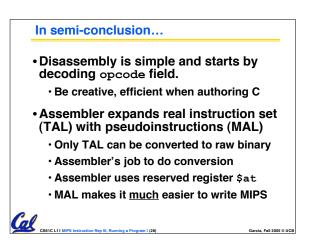

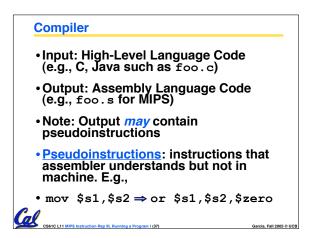

#### • Problem:

- When breaking up a pseudoinstruction, the assembler may need to use an extra reg.

- If it uses any regular register, it'll overwrite whatever the program has put into it.

### Solution:

CS61C L11 MIPS Instruct

- Reserve a register (\$1, called \$at for "assembler temporary") that assembler will use to break up pseudo-instructions.

- Since the assembler may use this at any time, it's not safe to code with it.

Garcia, Fall 2005 © UCB

n Rep III, Running a Program I (16)

| Rewrite TAL                                   | as MAL                               |                |  |

|-----------------------------------------------|--------------------------------------|----------------|--|

| •TAL:                                         |                                      |                |  |

| Loop:<br>Exit:                                | or<br>slt<br>beq<br>add<br>addi<br>j | \$v0,\$v0,\$a0 |  |

| • This time c                                 | onvert f                             | o MAL          |  |

| <ul> <li>It's OK for<br/>make up M</li> </ul> |                                      |                |  |

| Rewrite TAL    | as MAL                          | . (Answer)   |                         |

|----------------|---------------------------------|--------------|-------------------------|

| •TAL:<br>Loop: | or<br>slt<br>beq<br>add<br>addi | \$a1,\$a1,-1 |                         |

| Exit:          | j                               | Loop         |                         |

| •MAL:          |                                 |              |                         |

| Loop:          | li<br>bge<br>add<br>decr        | 1 , 1 , 1    | t                       |

| Exit:          | j<br>Running a Program I (      |              | Garcia, Fall 2005 © UCB |

| F   | Peer Instruction                                               |                                   |

|-----|----------------------------------------------------------------|-----------------------------------|

|     |                                                                |                                   |

|     |                                                                |                                   |

|     |                                                                |                                   |

| 1.  | Converting float -> int -> float<br>produces same float number | ABC<br>1: FFF                     |

| 2.  | Converting int -> float -> int produces<br>same int number     | 2: FFT<br>3: FTF<br>4: FTT        |

| 3.  | FP add is associative:<br>(x+y)+z = x+(y+z)                    | 5: TFF<br>6: TFT<br>7: TTF        |

| Cal | CS61C L11 MIPS Instruction Rep III, Running a Program I (23)   | 8: TTT<br>Garcia, Fall 2005 © UCB |

|    | Pee      | r Instr            | uctio              | n              |           |         |           |                |

|----|----------|--------------------|--------------------|----------------|-----------|---------|-----------|----------------|

|    |          |                    |                    |                |           |         |           | _              |

|    |          |                    |                    |                |           |         |           |                |

|    |          |                    |                    |                |           |         |           |                |

|    |          |                    |                    |                |           |         |           |                |

|    |          |                    |                    |                |           |         |           |                |

|    |          |                    |                    |                |           |         |           |                |

|    |          |                    |                    |                |           |         |           |                |

|    |          |                    |                    |                |           |         |           |                |

|    | W        | nich of t          | he instr           | uctions        | s below a | are MAL |           | ABC            |

|    | an       | d which            | are TA             | L?             |           |         |           | MMM<br>MMT     |

|    | Α.       | addi               | \$t0,              | \$t1,          | 40000     | )       | 3:        | MTM            |

|    | в        | beq                | \$=0               | 10             | Rwi+      |         |           | MTT<br>TMM     |

|    |          | -                  |                    |                |           |         |           | TMT            |

| •  | C.       | sub                | ŞtO,               | Şt1,           | 1         |         | 1         | TTM            |

| Ca | /        |                    |                    |                |           |         | 8:        | TTT            |

|    | CS61C L1 | 1 MIPS Instruction | Rep III, Running a | Program I (25) |           |         | Garcia, F | all 2005 © UCB |

| Week #                                                        | Mon                                             | Wed                   | Thurs Lab          |

|---------------------------------------------------------------|-------------------------------------------------|-----------------------|--------------------|

| #7<br>This<br>week                                            | MIPS III<br>Running<br>Program I                | Running<br>Program II | Running<br>Program |

| #8<br>Midterm<br>week<br>(review<br>Sun @<br>2pm 10<br>Evans) | Midterm @<br>5:30-8:30pm<br>Here!<br>(155 Dwin) | Intro to<br>SDS I     | SDS                |

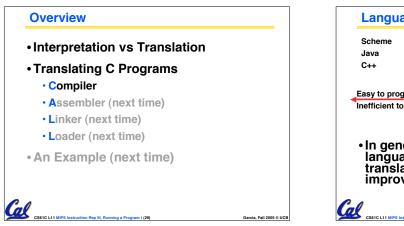

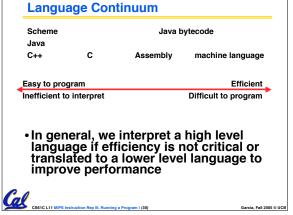

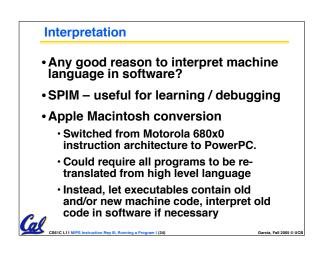

interpret old code in software if necessary

Cal