| Review                                                                                                                                                                       |                     |                       |                        |           |       |                         |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------|-----------|-------|-------------------------|--|--|

| Logical and Shift Instructions                                                                                                                                               |                     |                       |                        |           |       |                         |  |  |

| Operate on individual bits (arithmetic operate on entire word)                                                                                                               |                     |                       |                        |           |       |                         |  |  |

| Use to isolate fields, either by masking or by shifting back & forth     Use shift left logical, s11, for multiplication by powers of 2                                      |                     |                       |                        |           |       |                         |  |  |

| Use <u>shift right arithmetic</u> , sra, for division by powers of 2                                                                                                         |                     |                       |                        |           |       |                         |  |  |

| <ul> <li>Simplifying MIPS: Define instructions to be same size as<br/>data word (one word) so that they can use the same<br/>memory (compiler can use 1w and sw).</li> </ul> |                     |                       |                        |           |       |                         |  |  |

| Computer actually stores programs as a series of these     32-bit numbers.                                                                                                   |                     |                       |                        |           |       |                         |  |  |

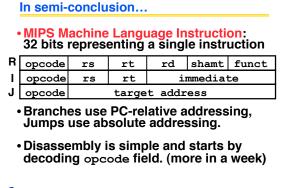

| MIPS Machine Language Instruction:<br>32 bits representing a single instruction                                                                                              |                     |                       |                        |           |       |                         |  |  |

| R                                                                                                                                                                            | opcode              | rs                    | rt                     | rd        | shamt | funct                   |  |  |

| I                                                                                                                                                                            | opcode              | rs                    | rt                     | immediate |       |                         |  |  |

| P                                                                                                                                                                            | opcode              | target address        |                        |           |       |                         |  |  |

|                                                                                                                                                                              | CS61C L10 MIPS Inst | ruction Representatio | n II, Floating Point I | (2)       |       | Garcia, Fall 2005 © UCB |  |  |

ng Point I (2)

Garcia, Fall 2005 © U

cia. Fall 2005 © UCB

### I-Format Problems (0/3)

### Problem 0: Unsigned # sign-extended?

•addiu, sltiu, sign-extends immediates to 32 bits. Thus, # is a "signed" integer.

### Rationale

- addiu so that can add w/out overflow

- See K&R pp. 230, 305

•sltiu suffers so that we can have ez HW

- Does this mean we'll get wrong answers?

- Nope, it means assembler has to handle any unsigned immediate  $2^{15} \le n < 2^{16}$  (i.e., with a 1 in the 15th bit and 0s in the upper 2 bytes) as it does for numbers that are too large.  $\Rightarrow$ **G**

### I-Format Problems (2/3)

- Solution to Problem 1:

- · Handle it in software + new instruction

- Don't change the current instructions: instead, add a new instruction to help out

### • New instruction:

lui register, immediate

- stands for Load Upper Immediate

- takes 16-bit immediate and puts these bits in the upper half (high order half) of the specified register

### sets lower half to 0s Cal

### Solution to Problem 1 (continued): • So how does lui help us? • Example: addi \$t0,\$t0, 0xABABCDCD becomes: lui \$at, 0xABAB \$at, \$at, 0xCDCD \$t0,\$t0,\$at ori add Now each I-format instruction has only a 16bit immediate. · Wouldn't it be nice if the assembler would this for us automatically? (later)

## I-Format Problems (1/3)

I-Format Problems (3/3)

### • Problem 1:

Cal

Cal "

CS61C L10

- · Chances are that addi, lw, sw and slti will use immediates small enough to fit in the immediate field.

- · We need a way to deal with a 32-bit

- •...but what if it's too big?

- immediate in any I-format instruction.

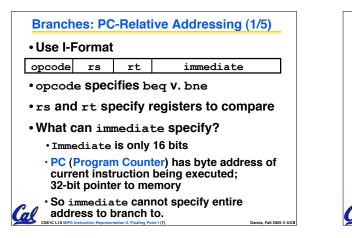

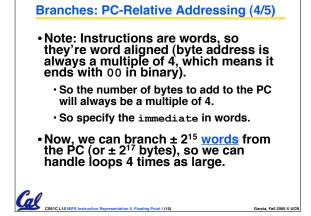

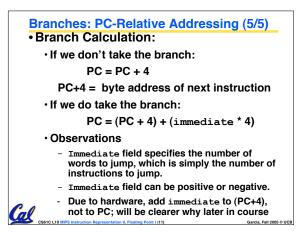

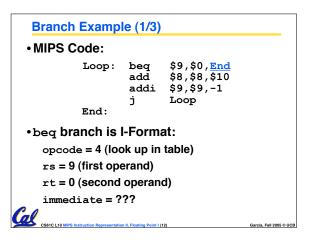

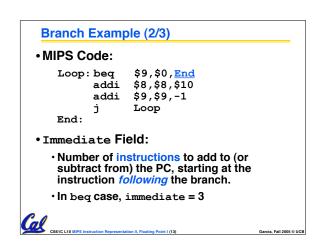

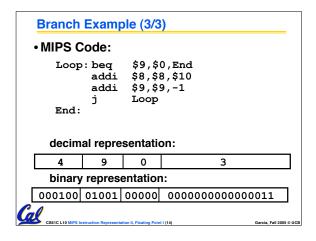

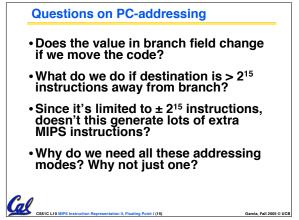

# Branches: PC-Relative Addressing (2/5) How do we usually use branches? Answer: if-else, while, for Loops are generally small: typically up to 50 instructions Function calls and unconditional jumps are done using jump instructions (j and jal), not the branches. Conclusion: may want to branch to anywhere in memory, but a branch often changes PC by a small amount

# Branches: PC-Relative Addressing (3/5)

- Solution to branches in a 32-bit instruction: PC-Relative Addressing

- Let the 16-bit immediate field be a signed two's complement integer to be *added* to the PC if we take the branch.

- Now we can branch ± 2<sup>15</sup> bytes from the PC, which should be enough to cover almost any loop.

- Any ideas to further optimize this?

CS61C L10 MIPS

| Week # Mon        |                                      | Wed                | Thu Lab             |  |

|-------------------|--------------------------------------|--------------------|---------------------|--|

| #6                | MIPS Inst<br>Format II /             | Floating<br>Pt II  | Floating            |  |

| This<br>week      | Floating Pt I                        | (No Dan OH)        | Pt                  |  |

| #7<br>Next        | MIPS Inst<br>Format III /<br>Running | Running<br>Program | Running<br>Program  |  |

| week              | Program I                            | (Proj 2 due)       | (Proj 2 really due) |  |

| #8                | Exam                                 |                    |                     |  |

| Midterm<br>week   | Midterm<br>5:30-                     | SDS I              | SDS                 |  |

| Sun 2pm<br>Review | 8:30pm<br>Here!                      |                    |                     |  |

| Define "fields" of the following number of bits each:                   |                |  |  |  |  |  |

|-------------------------------------------------------------------------|----------------|--|--|--|--|--|

| 6 bits                                                                  | 26 bits        |  |  |  |  |  |

| •As usual, each field has a name:                                       |                |  |  |  |  |  |

| opcode                                                                  | target address |  |  |  |  |  |

| Key Concepts                                                            |                |  |  |  |  |  |

| • Keep opcode field identical to R-format and I-format for consistency. |                |  |  |  |  |  |

| • Combine all other fields to make room for large target address.       |                |  |  |  |  |  |

# For branches, we assumed that we

CSSIC L10 MIPS Instruction Representation II, Floating Point I (18)

- won't want to branch too far, so we can specify change in PC.

- For general jumps (j and jal), we may jump to anywhere in memory.

- · Ideally, we could specify a 32-bit memory address to jump to.

- Unfortunately, we can't fit both a 6-bit opcode and a 32-bit address into a single 32-bit word, so we compromise.

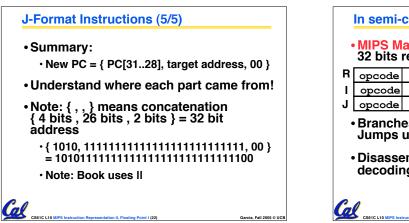

J-Format Instructions (1/5)

Garcia, Fall 2005 © UCB

### J-Format Instructions (3/5)

- For now, we can specify 26 bits of the 32-bit bit address.

- Optimization:

**G** CS61C L10 M

- Note that, just like with branches, jumps will only jump to word aligned addresses, so last two bits are always 00 (in binary).

- So let's just take this for granted and not even specify them.

# J-Format Instructions (4/5) Now specify 28 bits of a 32-bit address Where do we get the other 4 bits? By definition, take the 4 highest order bits from the PC. Technically, this means that we cannot jump to anywhere in memory, but it's adequate 99.9999...% of the time, since programs aren't that long only if straddle a 256 MB boundary If we absolutely need to specify a 32-bit address, we can always put it in a register and use the jr instruction.

Garcia, Fall 2005 © UCB

Garcia, Fall 2005 © UCB

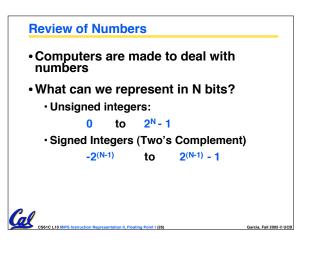

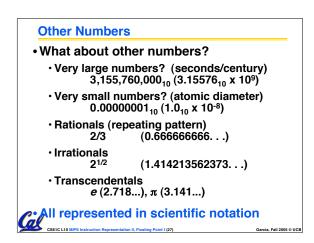

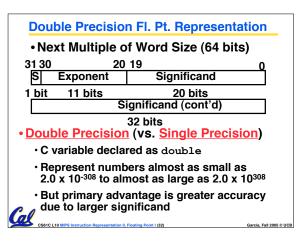

- Next Multiple of Word Size (128 bits)

- Unbelievable range of numbers

- Unbelievable precision (accuracy)

- This is currently being worked on

- The current version has 15 bits for the exponent and 112 bits for the significand

- Oct-Precision? That's just silly! It's been implemented before...

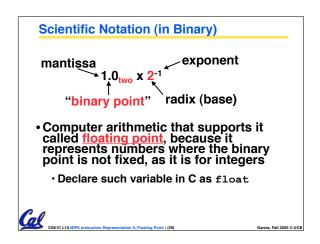

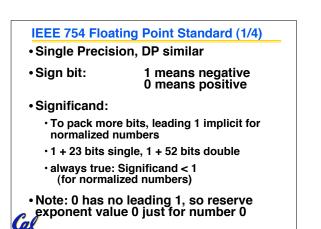

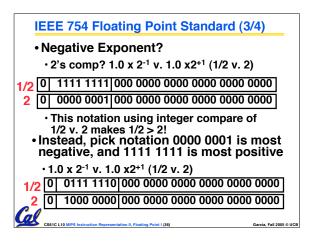

## IEEE 754 Floating Point Standard (2/4)

- Kahan wanted FP numbers to be used even if no FP hardware; e.g., sort records with FP numbers using integer compares

- Could break FP number into 3 parts: compare signs, then compare exponents, then compare significands

- Wanted it to be faster, single compare if possible, especially if positive numbers

- Then want order:

al

Cal con

- Highest order bit is sign ( negative < positive)</li>

- Exponent next, so big exponent => bigger #

Significand last: exponents same => bigger #

10 MIPS Instruction Representation II, Floating Point I (35) Garcia,

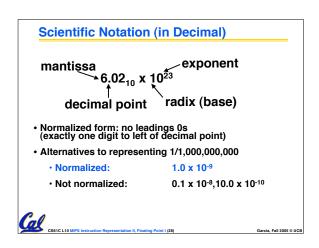

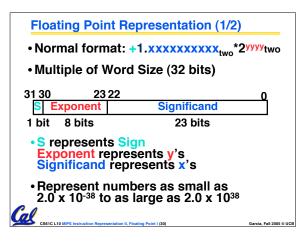

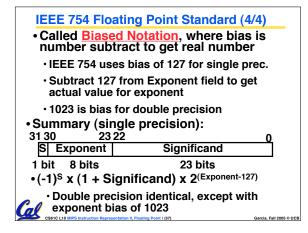

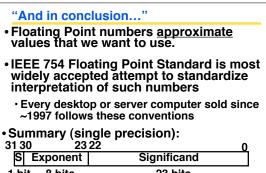

| 1   | bit | 8 bits | 23 bits                                 |     |

|-----|-----|--------|-----------------------------------------|-----|

|     |     |        | Significand) x 2(Exponent-1             |     |

| Cal | ۰Do | uble p | recision identical, bias of 1           | 023 |

|     |     |        | Consecutation II. Election Daint I (40) |     |