#### University of California, Berkeley - College of Engineering

Department of Electrical Engineering and Computer Sciences

Fall 2003

Instructor: Dave Patterson

2003-10-8

# CS 152 Exam #1

#### **Personal Information**

| First and Last Name                                                                                                                                          |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Your Login                                                                                                                                                   | cs152         |

| Lab/Discussion Section Time & Location you attend                                                                                                            |               |

| "All the work is my own. I have no prior knowledge<br>of the exam contents nor will I share the contents<br>with others in CS152 who have not taken it yet." | (Please sign) |

#### Instructions

- Partial credit may be given for incomplete answers, so please write down as much of the solution as you can.

- Please write legibly! If we can't read it from 3 feet away, we won't grade it!

- Put your name and login on each page.

- This exam will count for 16% of your grade.

#### **Grading Results**

| Question | Max.<br>Points | Points<br>Earned |

|----------|----------------|------------------|

| 1        | 30             |                  |

| 2        | 35             |                  |

| 3        | 35             |                  |

| Total    | 100            |                  |

#### **Question 1: Pipelined Processors (John's Question)**

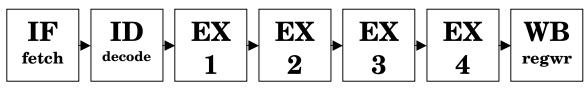

## Suppose we design a 7 stage pipelined processor with 4 execution/memory stages (EX1 through EX4) and hardware interlocks:

Assume an integer ALU latency of 0 and branches are still delayed and calculated in the decode stage (like in the 5-stage pipeline). Additionally, assume that the register file is designed so that when a value is written then it will be ready later in that same cycle.

Stage usage for R-type integer instructions:

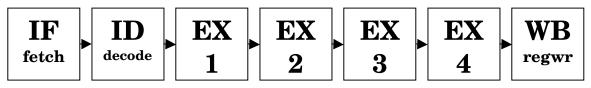

Suppose that data memory accesses take 2 EX cycles: one cycle to calculate the effective address (*addrc*), and one cycle to access the result (*mem*) (like the 5-stage pipeline) for both floating-point stores and integer stores.

Stage usage for memory access instructions:

We have additional the additional stages (EX3 and EX4) because our processor supports floating-point operations.

| Name: |

|-------|

|-------|

#### **Question 1: Pipelined Processors [continued]**

**1a**: Suppose that this processor requires a 2-cycle latency between the following instructions:

add.d F4, F0, F2 s.d F4, 0(R1)

(add.d is a floating-point addition instruction, and s.d is a floating-point store. F0, F2, F4 refer to floating point registers, and R1 refers to a regular integer register.)

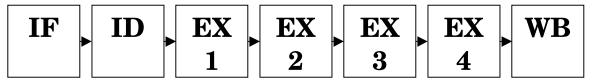

Similar to the pictures for integer and memory instructions, fill in the values for the stages used for a FLOATING POINT ALU operation. If a stage is unused, put 'nop'. If a label is not obvious (like 'fetch') please explain it.

Stages used for a floating-point ALU instruction:

**1b:** How did you figure out the stages in **1a** without us telling you? Please be brief but precise.

| Name: |

|-------|

|-------|

#### **Question 1: Pipelined Processors [continued]**

**1c:** Imagine that the following loop had just finished executing its 100<sup>th</sup> iteration on the 7-stage pipeline. How many more clock cycles will it take for the pipeline to finish the 101<sup>st</sup> iteration?

Loop: l.d F0, 0(R1) add.d F4, F0, F2 s.d F4, 0(R1) addiu R1, R1, -8 bne R1, R2, Loop

Answer:\_\_\_\_\_ clock cycles

**1d:** Reorder the instructions from question 2 so that the number of stalls is minimized. How many cycles are there between the finishing of the 100<sup>th</sup> and 101<sup>st</sup> iterations now?

#### **Reordered code:**

Answer:\_\_\_\_\_ clock cycles

## Name: Login: Question 1: Pipelined Processors [continued]

1e: A forwarding path from stage X to stage Y is written as: X to Y

This means that the register after stage X can forward some value to the beginning of stage Y (i.e. after the register between stage Y-1 and Y).

In the table below, we have listed all of the possible forwarding paths among ID, EX1, and EX2. We'd like you to tell us which ones are useful (in the sense that a forwarding circuit between the two stages will do useful work) and, if a forwarding path is useful, which values and instructions the forwarding will be used for. For this problem, you may assume that **there are four general types of instructions: integer ops, loads/stores, floating point ops, and branches**.

| Forwarding<br>Path | Useful? | If yes, which values can be forwarded? For which types of instructions? |

|--------------------|---------|-------------------------------------------------------------------------|

| ID to ID           | YES NO  |                                                                         |

| ID to EX1          | YES NO  |                                                                         |

| ID to EX2          | YES NO  |                                                                         |

|                    |         |                                                                         |

| EX1 to ID          | YES NO  |                                                                         |

| EX1 to EX1         | YES NO  |                                                                         |

| EX1 to EX2         | YES NO  |                                                                         |

|                    |         |                                                                         |

#### Name:

| JOC |  |  |

|-----|--|--|

|     |  |  |

|     |  |  |

| e | :          |        | Login: |

|---|------------|--------|--------|

|   | EX2 to ID  | YES NO |        |

|   | EX2 to EX1 | YES NO |        |

|   | EX2 to EX2 | YES NO |        |

| Nan | ne: |      |   |   |   |   | Login: |  |

|-----|-----|------|---|---|---|---|--------|--|

| ~   |     | a a. | - | ~ | - | - |        |  |

#### **Question 2: Single Cycle Processor (Jack's Question)**

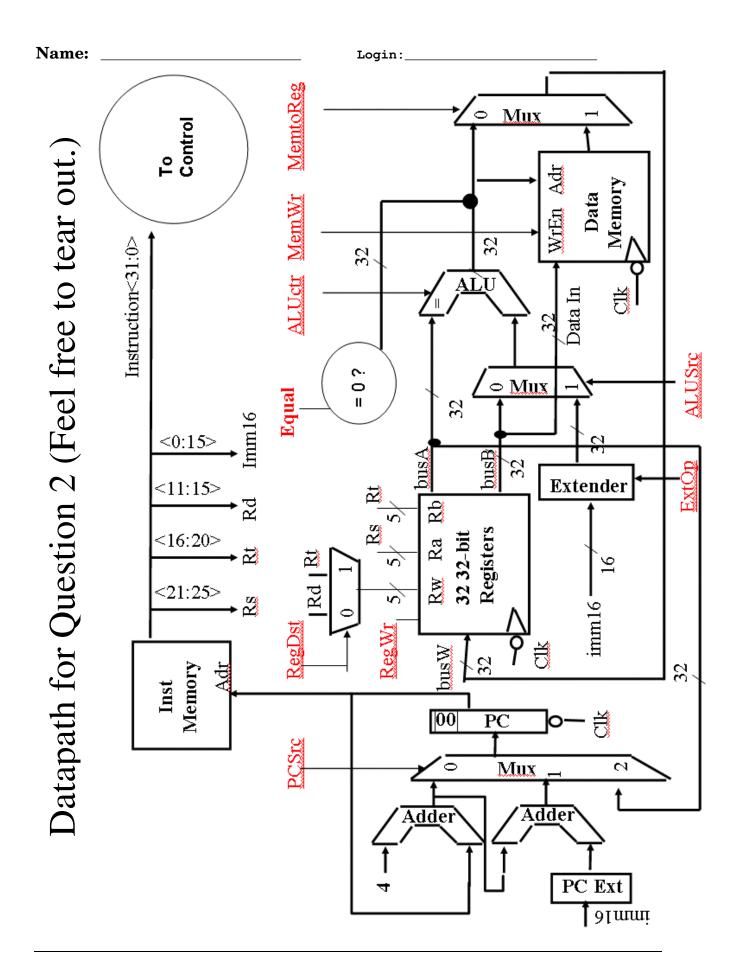

Your single-cycle processor seems to be executing random instructions. You have been chosen by your group to investigate and find out why. On the next page you will find a picture of your datapath (note that this is a **slightly different datapath** than shown in lecture), and the control table is below. You suspect that the controller may be broken. You may assume that the modules within the datapath (i.e. extender, alu) all work.

|      | PCSrc | RegDst | RegWr | ExtOp | ALUSrc | ALUctr | MemW | MemToRe |

|------|-------|--------|-------|-------|--------|--------|------|---------|

|      |       |        |       |       |        |        | r    | g       |

| addu | 0     | 0      | 1     | 1     | X      | 0      | 0    | 0       |

| subu | 0     | 1      | 1     | Х     | 0      | 0      | 0    | 0       |

| ori  | 0     | 1      | 1     | 0     | Х      | 2      | 0    | 0       |

| Lw   | 0     | 1      | 1     | 1     | 1      | 0      | 1    | 1       |

| Sw   | 0     | Х      | 0     | 0     | 1      | 0      | 1    | х       |

| beq  | Equal | Х      | 0     | Х     | 0      | 3      | 0    | x       |

| Jr   | 2     | Х      | 0     | Х     | х      | Х      | 0    | x       |

"Equal" means that PCSrc takes on the value of the equal signal coming out of the =0? module. This will either be 0 or 1.

Looking at your partners' online notebooks, you find the following (you may assume these to be correct):

- The register file (regWr) and data memory (MemWr) both write when their respective write signals are 1

- The extender will zero extend if the ExtOp bit is 0, and the extender will sign extend when the ExtOp control bit is 1.

- The data memory reads asynchronously but has synchronous writes (just like your single cycle lab).

- The =0? module will output 1 if the input to the module is 0, else it will output 0.

The ALUctr encoding is as follows:

| Control bits | Operation |

|--------------|-----------|

| 0            | add       |

| 1            | sub       |

| 2            | or        |

| 3            | Xor       |

For the following stream of instructions, what does your broken processor actually do? The first instruction has already been done for you as an example. If there is more than one possibility, please list all of them (note that this may be a different instruction, correct behavior, or an undefined instruction). If the incorrect result does not match a valid MIPS instruction, please give a sequence of instructions that correspond to the behavior. Also give a **very brief** explanation of your possibilities. For simplicity, we have used the actual register numbers rather than the names.

| Name: |

|-------|

|-------|

#### **Question 2: Single Cycle Processor [continued]**

| <b>Original Instruction</b> | Possibilities                                         |

|-----------------------------|-------------------------------------------------------|

|                             | addu \$1, \$2, \$0 (if aluSrc is 0—correct behavior)  |

| addu \$1, \$2, \$0          | addiu \$1, \$2, 33(if aluSrc is 1—incorrect behavior) |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

| subu \$4, \$5, \$6          |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

| ori \$7, \$8, 0x0025        |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

| beq \$11, \$12, 24          |                                                       |

| bey \$11, \$12, 24          |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

| sw \$10, -12(\$31)          |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

| lw \$9, -16(\$29)           |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

|                             |                                                       |

| Name: |  |

|-------|--|

|       |  |

Login:\_\_\_

| Name: | Login: |  |

|-------|--------|--|

|       | -      |  |

#### Question 3: Multicycle Processor (Kurt's Question)

We'd like to give you a feel for how microprogramming can help out with tricky CISC instructions. We'd like you to implement a new addressing mode (register indirect; i.e. register value is an address with no offset) for the sub instruction:

sub.mem \$rd \$rs \$rt # Mem[\$rd] = Mem[\$rs] - Mem[\$rt]

#### Your solutions to 3a-d will be graded, in part, on elegance!

**3a:** Please come up with a suitable machine representation for sub.mem. You may assume that opcode  $44_{hex}$  and funct  $44_{hex}$  are both unused. Make your representation clean and complementary to the MIPS datapath.

Here's an example of what we are looking for (for *nor*):

NOR

| nor rd. rs. rt | 0 | rs | rt | rd | 0 | Ox27 |

|----------------|---|----|----|----|---|------|

|                | 6 | 5  | 5  | 5  | 5 | 6    |

Now do the same for sub.mem.

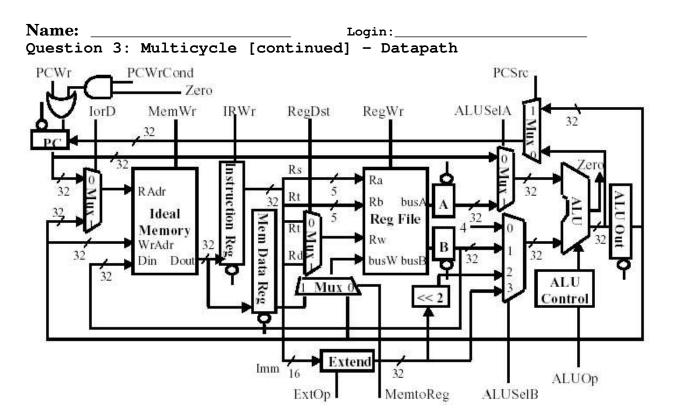

3b: Above is the multicycle datapath from lecture. Please draw below any changes to the datapath to support your sub.mem. YOU MAY NOT ADD ANY REGISTERS!!! (Do everything with muxes and simple, combinational modules.) Don't redraw the entire datapath – just circle the areas you're changing in the above diagram and then re-draw modules and muxes that you have changed (including control line names) below. DRAW LEGIBLY.

| Name:   |                               | Login:   |

|---------|-------------------------------|----------|

| Questio | n 3: Multicycle [continued] - | Datapath |

| Field Name | Values For Field | Function of Field                                          |

|------------|------------------|------------------------------------------------------------|

| ALU        | Add              | ALU Adds                                                   |

|            | Sub              | ALU subtracts                                              |

| ALU        | Func             | ALU does function code (Inst[5:0])                         |

|            | Or               | ALU does logical OR                                        |

| SRC1       | PC               | $PC \Rightarrow 1^{st} ALU input$                          |

| SKCI       | rs               | $R[rs] \Rightarrow 1^{st} ALU input$                       |

|            | 4                | $4 \Rightarrow 2^{nd} ALU input$                           |

|            | rt               | $R[rt] \Rightarrow 2^{nd} ALU input$                       |

| SRC2       | Extend           | sign ext imm16 (Inst[15:0]) $\Rightarrow 2^{nd}$ ALU input |

|            | Extend0          | zero ext imm16 (Inst[15:0]) $\Rightarrow 2^{nd}$ ALU input |

|            | ExtShft          | 2 <sup>nd</sup> ALU input = sign extended imm16 << 2       |

|            | rd-ALU           | $ALUout \Rightarrow R[rd]$                                 |

| ALU Dest   | rt-ALU           | $ALUout \Rightarrow R[rt]$                                 |

|            | rt-Mem           | Mem input $\Rightarrow$ R[rt]                              |

|            | Read-PC          | Read Memory using the PC for the address                   |

| Memory     | Read-ALU         | Read Memory using the ALUout register for the address      |

|            | Write-ALU        | Write Memory using the ALUout register for the address     |

| MemReg     | IR               | Mem input $\Rightarrow$ IR                                 |

| DC Weite   | ALU              | ALU value $\Rightarrow$ PCibm                              |

| PC Write   | ALUoutCond       | If ALU Zero is true, then ALUout $\Rightarrow$ PC          |

|            | Seq              | Go to next sequential microinstruction                     |

| Sequence   | Fetch            | Go to the first microinstruction                           |

|            | Dispatch         | Dispatch using ROM                                         |

**3c:** Above is the microassembly language description from lecture. Please describe any additions or modifications to microassembly language necessary to support sub.mem. Be sure to include the field name, the new field values, as well as **EXACTLY** which control lines are set when the field value is asserted. **Be precise and print legibly!**

| Name:                                         |      |      |         |         | Login: |        |            | _        |

|-----------------------------------------------|------|------|---------|---------|--------|--------|------------|----------|

| Question 3: Multicycle [continued] - Datapath |      |      |         |         |        |        |            |          |

| Label                                         | ALU  | SRC1 | SRC2    | ALUDest | Memory | MemReg | PCWrite    | Sequence |

| Fetch                                         | Add  | PC   | 4       |         | ReadPC | IR     | ALU        | Seq      |

|                                               | Add  | PC   | ExtShft |         |        |        |            | Dispatch |

| RType                                         | Func | rs   | rt      |         |        |        |            | Seq      |

|                                               |      |      |         | rd-ALU  |        |        |            | Fetch    |

| BEQ                                           | Sub  | rs   | rt      |         |        |        | ALUoutCond | Fetch    |

3d: Above are the implementations for a few MIPS instructions in our microassembly language. Please give a complete microcode assembly implementation for your sub.mem. You may assume that dispatch will jump to a label named 'sub.mem'.

Print legibly.

Label ALU SRC1 SRC2 ALUDest Memory MemReg PCWrite Sequence

| Name: _  |                             | Login:_    |

|----------|-----------------------------|------------|

| Question | n 3: Multicycle [continued] | - Datapath |

### **3e. EXTRA CREDIT: QUITE DIFFICULT AND NOT WORTH MANY POINTS:**

(We suggest that you finish all the other problems on the exam before you attempt this one.) 5 EC points.

Using your new datapath and control from above, please implement the Subtract and Branch if Negative (SBN) instruction in microcode:

sbn \$rs \$rt immed # **Mem[\$rs] = Mem[\$rs]-Mem[\$rt]** # if (Mem[\$rs]<0) goto PC+4+immed

Please give a machine representation (like 3a), draw any changes to the datapath (like 3b), explain any new microassembly fields and values (like 3c), and give the complete microassembly sequence (like 3d). Again: No new registers.

**Hint:** You already have the sub.mem part almost done – the hard part is figuring out how to jump.

**Machine Representation:**

#### **Datapath Changes**

(You may assume your new datapath from 3b.)

Name:

Login:

Question 3: Multicycle [continued] - Datapath

**3e continued:**

Additions to microassembly language:

SBN microassembly implementation (complete):