#### EECS150 - Digital Design

#### <u>Lecture 6 - Computer Aided Design</u> (CAD) - Part I (Logic Synthesis)

Feb 4, 2010

John Wawrzynek

Spring 2010

EECS150 - Lec06-CAD1

Page 1

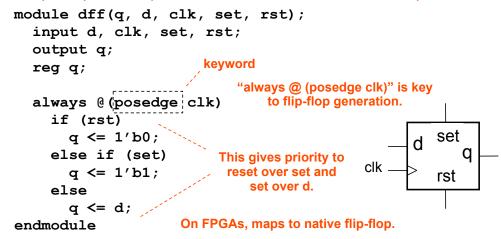

#### **State Elements**

Always blocks are the only way to specify the "behavior" of state elements. Synthesis tools will turn state element behaviors into state element instances.

D-flip-flop with synchronous set and reset example:

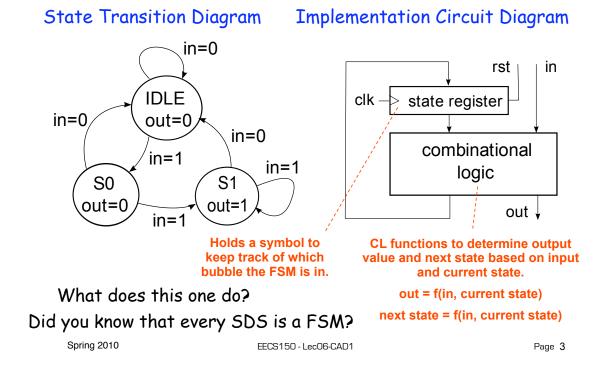

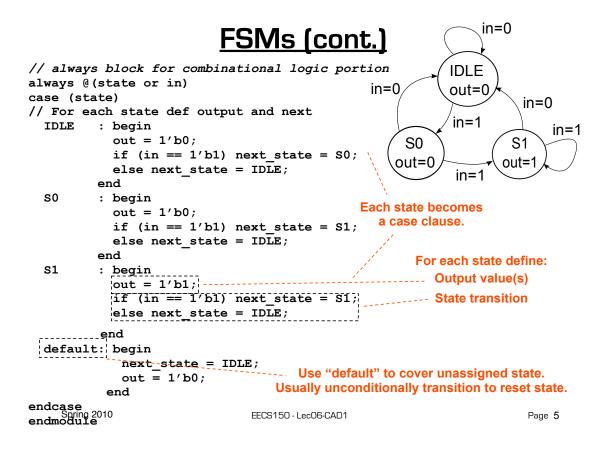

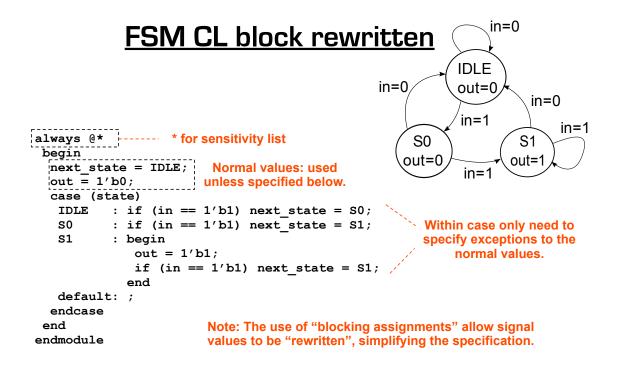

#### **Finite State Machines**

#### **Finite State Machines** in=0 module FSM1(clk, rst, in, out); IDLE input clk, rst; Must use reset to force in=0 input in; out=0 to initial state. in=0 output out; reset not always shown in STD in=1 in=1 S0 // Defined state encoding: S1 parameter IDLE = 2'b00; out=0 out=1 **Constants local** in=1 parameter S0 = 2'b01;to this module. parameter S1 = 2'b10; reg out; ----- out not a register, but assigned in always block reg [1:0] state, next state; **Combinational logic** signals for transition. THE register to hold the "state" of the FSM. // always block for state register always @(posedge clk) if (rst) state <= IDLE;</pre> else state <= next state;</pre> A separate always block should be used for combination logic part of FSM. Next state and output generation. (Always blocks in a design work in parallel.) Spring 2010 EECS150 - Lec06-CAD1 Page 4

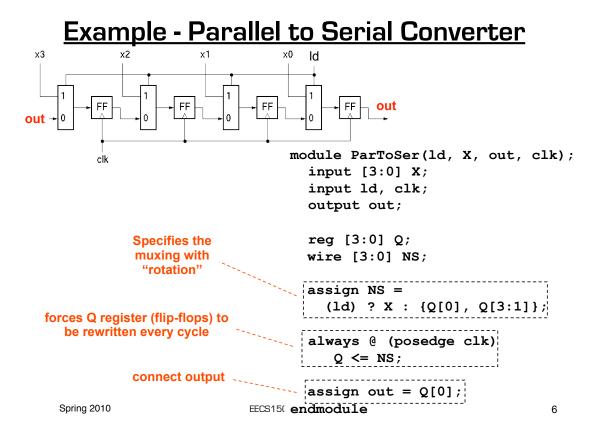

#### **Parameterized Version**

Parameters give us a way to generalize our designs. A module becomes a "generator" for different variations. Enables design/module reuse. Can simplify testing.

| parameter N = 4;<br>Declare a parameter with<br>default value.<br>Note: this is not a port.<br>Acts like a "synthesis-<br>time" constant. | <pre>nodule ParToSer(ld, X, out, CLK);<br/>input [N-1:0] X;<br/>input ld, clk;<br/>output out;<br/>reg out; Replace all occurrences<br/>reg [N-1:0] Q;<br/>wire [N-1:0] NS;</pre> |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ParToSer #(.N(8))                                                                                                                         | assign NS =                                                                                                                                                                       |

| ps8 ( );                                                                                                                                  | (ld) ? X : {Q[0], Q[ <mark>N-1</mark> :1]};                                                                                                                                       |

| ParToSer #(.N(64))                                                                                                                        | always @ (posedge clk)                                                                                                                                                            |

| ps64 ( );                                                                                                                                 | Q <= NS;                                                                                                                                                                          |

| Overwrite parameter N at<br>instantiation.<br>Spring 2010 EECS15C                                                                         | assign out = Q[0];<br>endmodule                                                                                                                                                   |

#### **Generate Loop**

Permits variable declarations, modules, user defined primitives, gate primitives, continuous assignments, initial blocks and always blocks to be instantiated multiple times using a for-loop.

| <pre>// Gray-code to binary-code converter</pre>                                                                       |                                                                           |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| <pre>module gray2bin1 (bin, gray);     parameter SIZE = 8;     output [SIZE-1:0] bin;     input [SIZE-1:0] gray;</pre> | genvar exists only in<br>the specification - not<br>in the final circuit. |

| genvar i;                                                                                                              | Keywords that denotes synthesis-time operations                           |

| <pre>generate for (i=0; i<size; begi<br="" i="i+1)">assign bin[i] = ^gray[SIZE-1:i];</size;></pre>                     | n:bit For-loop creates<br>instances of assignments                        |

| end endgenerate<br>endmodule                                                                                           | Loop must have constant bounds                                            |

generate if-else-if based on an expression that is deterministic at the time the design is synthesized.

**generate case** : selecting case expression must be deterministic at the time the design is synthesized.

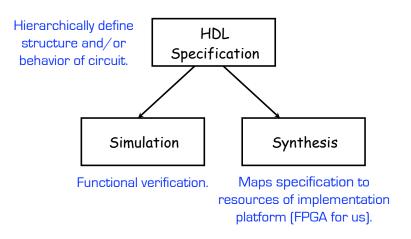

## EECS150 Design Methodology

Note: This in not the entire story. Other tools are often used analyze HDL specifications and synthesis results. More on this later.

```

Spring 2010 EECS150 - LecO6-CAD1 Page 9

```

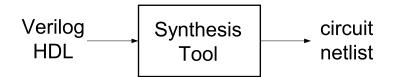

## Logic Synthesis

• Verilog and VHDL started out as simulation languages, but quickly people wrote programs to automatically convert Verilog code into low-level circuit descriptions (netlists).

- Synthesis converts Verilog (or other HDL) descriptions to implementation technology specific primitives:

- For FPGAs: LUTs, flip-flops, and RAM blocks

- For ASICs: standard cell gate and flip-flop libraries, and memory blocks.

# Why Logic Synthesis?

- 1. Automatically manages many details of the design process:

- $\Rightarrow$  Fewer bugs

- $\Rightarrow$  Improved productivity

- 2. Abstracts the design data (HDL description) from any particular implementation technology.

- Designs can be re-synthesized targeting different chip technologies. Ex: first implement in FPGA then later in ASIC.

- 3. In some cases, leads to a more optimal design than could be achieved by manual means (ex: logic optimization)

#### Why Not Logic Synthesis?

1. May lead to non-optimal designs in some cases.

Spring 2010

EECS150 - Lec06-CAD1

Page 11

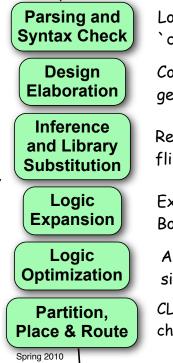

#### <u>**Main Logic Synthesis Steps</u>**</u>

foo.ncd

Load in HDL file, run macro preprocessor for `define, `include, etc..

Compute parameter expressions, process generates, create instances, connect ports.

Recognize and insert special blocks (memory, flip-flops, arithmetic structures, ...)

Expand combinational logic to primitive Boolean representation.

Apply Boolean algebra and heuristics to simplify and optimize under constraints.

CL to LUTs, map memory and state elements to chip, assign physical locations, route connections.

EECS150 - LecO5-Verilog

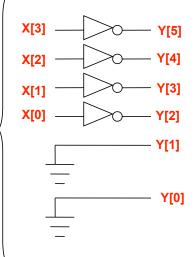

#### **Operators and Synthesis**

- Logical operators map into primitive logic gates

- Arithmetic operators map into adders, subtractors, ...

- Unsigned 2s complement

- Model carry: target is one-bit wider that source

- Watch out for \*, %, and /

- Relational operators generate comparators

- Shifts by constant amount are just wire connections

- No logic involved

- Variable shift amounts a whole different story --- shifter

- Conditional expression generates logic or MUX Spring 2010

EECS150 - LecOB-CAD1

Y = -X << 2

Page 13

#### Simple Example

| module foo (A, B, s0, s1, F);       |    |

|-------------------------------------|----|

| input [3:0] A;                      | s0 |

| input [3:0] B;                      |    |

| <pre>input s0,s1;</pre>             | si |

| output [3:0] F;                     | Α1 |

| reg F;                              | ·  |

| always @ (*)                        | В0 |

| if (!s0 && s1    s0) F=A; else F=B; |    |

| endmodule                           |    |

Should expand if-else into 4-bit wide multiplexor and optimize the control logic and ultimately to a single LUT on an FPGA:

#### More about Always blocks

Spring 2010

EECS150 - LecO6-CAD1

Page 15

#### **Combinational logic always blocks**

Make sure all signals assigned in a combinational always block are explicitly assigned values every time that the always block executes. Otherwise latches will be generated to hold the last value for the signals not assigned values.

```

module mux4to1 (out, a, b, c, d, sel);

Sel case value 2'd2 omitted.

output out;

input a, b, c, d;

input [1:0] sel;

Out is not updated when select

req out;

line has 2'd2.

always @(sel or a or b or c or d)

begin

case (sel)

Latch is added by tool to hold

2'd0: out = a;

the last value of out under this

2'd1: out = b;

condition.

2'd3: out = d;

endcase

Similar problem with if-else

end

endmodule

statements.

```

Spring 2010

#### **Combinational logic always blocks**

To avoid synthesizing a latch in this case, add the missing select line:

2'd2: out = c;

Or, in general, use the "default" case:

default: out = foo;

If you don't care about the assignment in a case (for instance you know that it will never come up) then you can assign the value "x" to the variable. Example:

default: out = 1 bx;

The x is treated as a "don't care" for synthesis and will simplify the logic.

Be careful when assigning x (don't care). If this case were to come up, then the synthesized circuit and simulation may differ.

Spring 2010

EECS150 - Lec06-CAD1

Page 17

#### **Incomplete Triggers**

Leaving out an input trigger usually results in latch generation for the missing trigger.

# Easy way to avoid incomplete triggers for combinational logic is with: always @\*

Spring 2010

#### **Procedural Assignments**

#### Verilog has two types of assignments within always blocks:

- Blocking procedural assignment "="

- In simulation the RHS is executed and the assignment is completed before the next statement is executed. Example:

- Assume A holds the value 1 ... A=2; B=A; A is left with 2, B with 2.

- Non-blocking procedural assignment "<="</li>

- In simulation the RHS is executed and all assignment take place at the same time (end of the current time step - not clock cycle). Example:

Assume A holds the value 1 ... A<=2; B<=A; A is left with 2, B with 1.

• In synthesis the difference shows up primarily when inferring state elements:

| always @ (  | posedge clk) be | gin always @ (posedge clk) begin |

|-------------|-----------------|----------------------------------|

| a = in;     | b = a;          | a <= in; b<= a;                  |

| end         |                 | end                              |

|             | b stores in     | b stores the old a               |

| Spring 2010 |                 | EECS150 - Lec06-CAD1 Page 19     |

#### **Procedural Assignments**

The sequential semantics of the blocking assignment allows variables to be multiply assigned within a single always block. Unexpected behavior can result from mixing these assignments in a single block. Standard rules:

- Use blocking assignments to model combinational logic within an always block ( "=").

- Use non-blocking assignments to implement sequential logic ("<=").</li>

- iii. Do not mix blocking and non-blocking assignments in the same always block.

- iv. Do not make assignments to the same variable from more than one always block.

```

Page 21

```

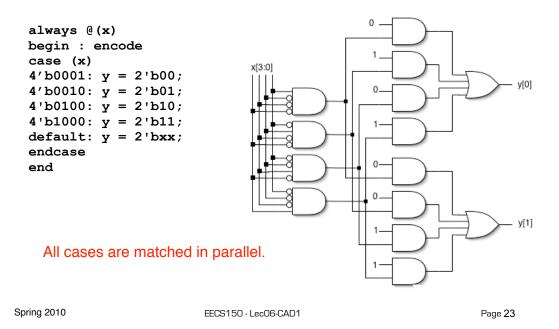

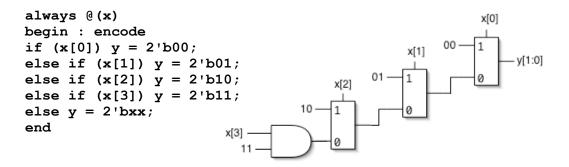

#### **Encoder Example**

Nested IF-ELSE might lead to "priority logic" Example: 4-to-2 encoder

```

always @(x)

This style of cascaded logic

begin : encode

if (x == 4'b0001) y = 2'b00;

may adversely affect the

else if (x == 4'b0010) y = 2'b01;

performance of the circuit.

else if (x == 4'b0100) y = 2'b10;

else if (x == 4'b1000) y = 2'b11;

else y = 2'bxx;

x[3:0]

end

00 -

1

y[1:0]

01

1

10

1

0

0

EECS150 - LecO6-CAD1

```

Spring 2010

#### Encoder Example (cont.)

#### To avoid "priority logic" use the case construct:

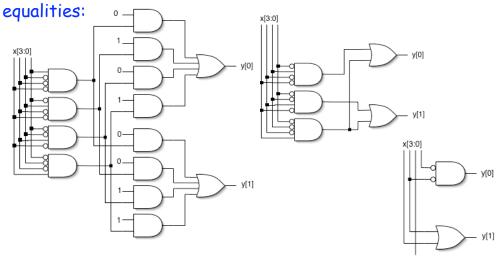

#### Encoder Example (cont.)

This circuit would be simplified during synthesis to take advantage of constant values as follows and other Boolean

A similar simplification would be applied to the if-else version also.

#### Encoder Example (cont.)

If you can guarantee that only one 1 appears in the input, then simpler logic can be generated:

If the input applied has more than one 1, then this version functions as a "priority encoder". The least significant 1 gets priority (the more significant 1's are ignored). Again the circuit will be simplified when possible.

Spring 2010

EECS150 - LecO6-CAD1

Page 25

#### Verilog in EECS150

- We use **behavior modeling** along with **instantiation** to 1) build hierarchy and, 2) map to FPGA resources not supported by synthesis.

- Primary Style Guidelines:

- Favor continuous assign and avoid always blocks unless:

- no other alternative: ex: state elements, case

- they help clarity of code & possibly circuit efficiency : ex: case vs, large nested if else

- Use named ports.

- Separate CL logic specification from state elements.

- Follow our rules for procedural assignments.

- Verilog is a big language. This is only an introduction.

- Our text book is a good source. Read and use chapter 4.

- Be careful of what you read on the web. Many bad examples out there.

- We will be introducing more useful constructs throughout the semester. Stay tuned!

#### **Final thoughts on Verilog Examples**

Verilog may look like C, but it describes hardware! (Except in simulation "test-benches" - which actually behave like programs.)

Multiple physical elements with parallel activities and temporal relationships.

A large part of digital design is knowing how to write Verilog that gets you the desired circuit. <u>First understand the circuit you</u> <u>want then figure out how to code it in Verilog</u>. If you do one of these activities without the other, you will struggle. These two activities will merge at some point for you.

Be suspicious of the synthesis tools! Check the output of the tools to make sure you get what you want.

Spring 2010

EECS150 - Lec06-CAD1

Page 27