# Structural Verilog

### EECS150 Spring2009 - Lab Lecture #2

Chris Fletcher Slides designed by Chris Fletcher

Slides: "Verilog (1)", "Verilog (2)" and "CAD + Verilog" by Greg Gibeling

1/30/2009

EECS150 Lab Lecture #2

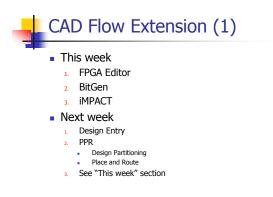

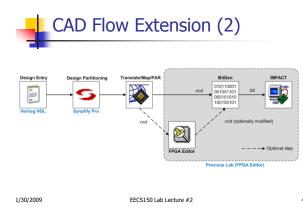

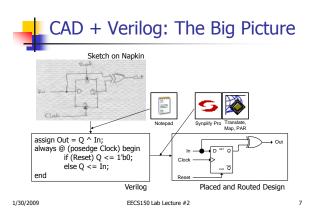

- CAD Flow Extension

- Verilog

- Structural Verilog

- Administrative Info

- Lab #2: The Structural Accumulator

- Lab2 circuit

- Lab2 testing

- Analysis of resource usage and timing

1/30/2009

EECS150 Lab Lecture #2

1/30/2009

EECS150 Lab Lecture #2

3

1

Verilog (1)

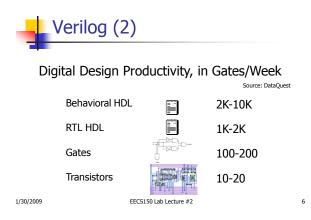

What's an HDL?

Textual Description of a Circuit

Human and Machine Readable

Hierarchical

Meaningful Naming

NOT A PROGRAM

Describe what the circuit IS

Not what it DOES

1/30/2009

EECS150 Lab Lecture #2

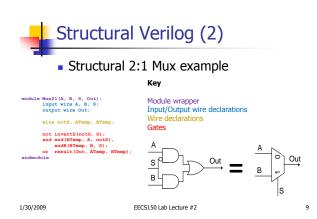

- Verilog Subsets

- Structural: primitive gates + modules

- Gate level design

- You will ONLY use Structural Verilog in this lab

8

- Dataflow: compact boolean expressions

- More compact expression of structural Verilog

- Behavioral: abstract syntax

- Timing nuances

- You will see this starting next lab

1/30/2009

EECS150 Lab Lecture #2

## Administrative Info

- Homework submission policy

- Lab lecture conflicts

- Card key access

- Check-off procedure

- Questions?

1/30/2009 EECS150 Lab Lecture #2

- Build a structural Accumulator

- Work with a real design

- Write parameterized Verilog

- Debugging

- Synplicity RTL/Technology schematic

EECS150 Lab Lecture #2

- Analysis

- Resource consumption

- Timing

1/30/2009

1/30/2009

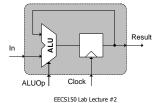

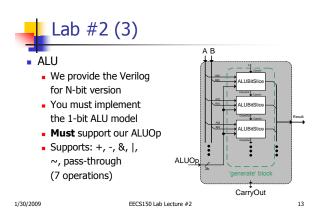

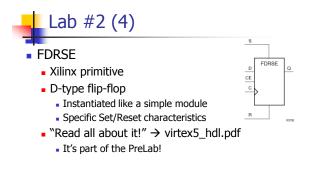

Lab #2 (2)

- Structural Accumulator

- ALU

- 'FDRSE' Xilinx primitive flip-flop

12

10

EECS150 Lab Lecture #2

Lab #2 (5)

- Accumulator

- We give you port specification

- You will implement the rest of the circuit

- Use code examples

- Mux21: Structural Verilog (gates, wires)

- ALU: generate statements

- Abide by our interfaces!

1/30/2009

15

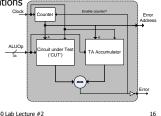

#### HW test harness

- TA Accumulator vs. your Accumulator

- Check all input combinations

- Signal error and show address if mismatch

1/30/2009

EECS150 Lab Lecture #2

### Circuit Analysis

- Resource Usage

- Accumulator(width) = how many LUTs / SLICEs?

- generate allows you to experiment

- Timing

- Locate nets → "Technology Schematic"

- Calculate delay on the nets → **FPGA Editor**

1/30/2009

EECS150 Lab Lecture #2

- PreLab

- Read specified material

- Write all of your Verilog

- Lab starts at debugging phase

- Assumption:

- you have written all of your Verilog ahead of time

1/30/2009

18