## 3.15)

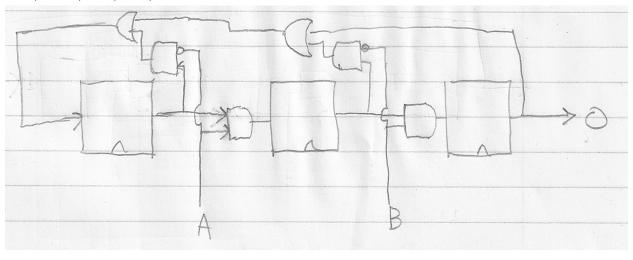

- (a) Is not a synchronous sequential circuit because there is no register.

- (b) Is not a synchronous sequential circuit because there is a combinational loop.

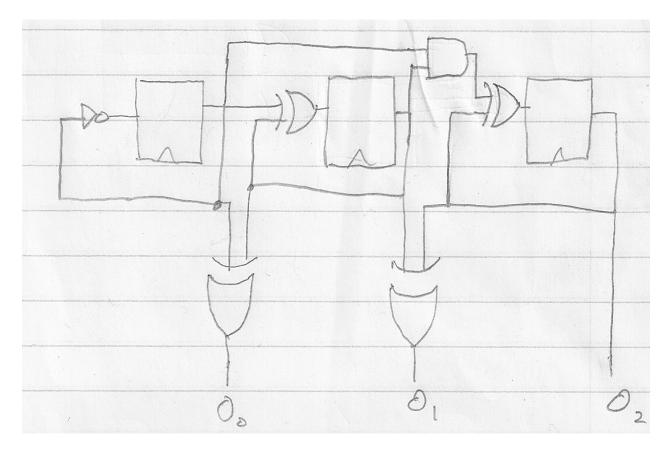

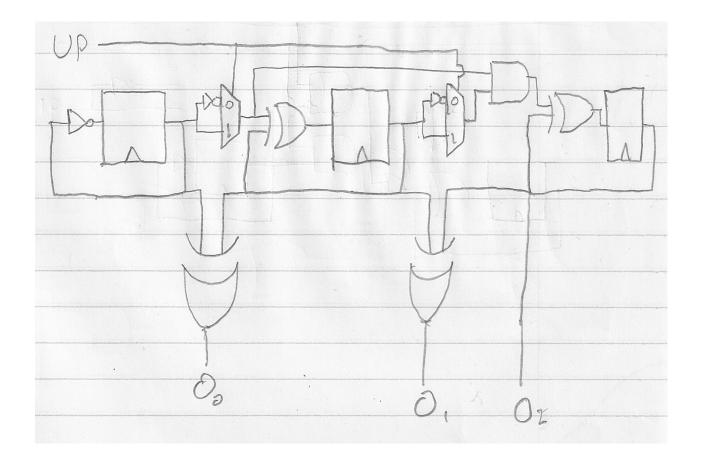

- (c) Is a synchronous sequential circuit because the feedback loop is on the other side of a register.

- (d) Is also a synchronous sequential circuit because the feedback loop is on the other side of the register.

## 3.19)

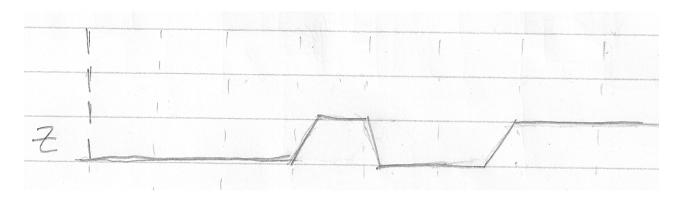

This FSM has two inputs A and B, and an output Q. Q\_n is high when  $A_{n-2}$  is high and  $B_{n-1}$  is high, otherwise it is zero.

| CS |  | NS |  | А |  | В |  | 0 |  |  |  |

|----|--|----|--|---|--|---|--|---|--|--|--|

|    |  |    |  |   |  |   |  |   |  |  |  |

| SO |  | SO |  | 0 |  | Χ |  | 0 |  |  |  |

| S0 |  | S1 |  | 1 |  | Χ |  | 0 |  |  |  |

| S1 |  | S0 |  | Χ |  | 0 |  | 0 |  |  |  |

| S1 |  | S2 |  | Χ |  | 1 |  | 0 |  |  |  |

| S2 |  | S0 |  | Χ |  | Χ |  | 1 |  |  |  |

3.25)

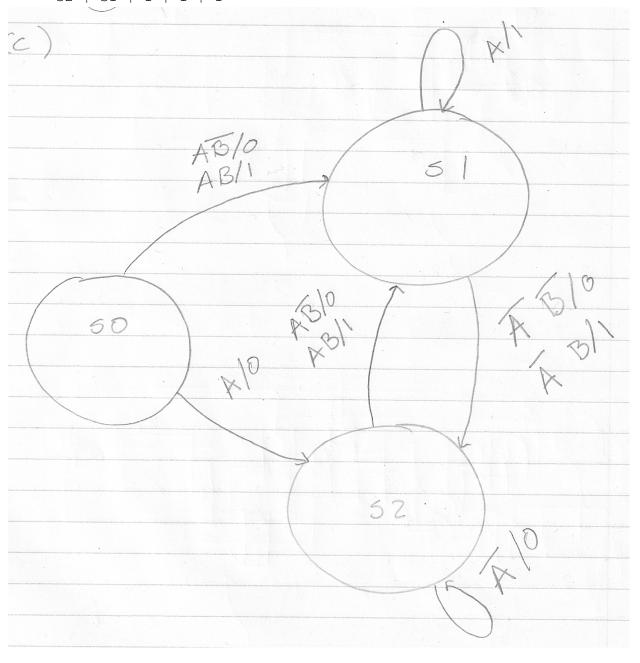

3.26) (a)

(b) Mealey

(C)

| CS |   | NS     |   | A |   | В | 1 | Z |

|----|---|--------|---|---|---|---|---|---|

| s0 |   | <br>S1 |   | 1 |   | 0 |   | 0 |

| S0 |   | S1     | Ì | 1 |   | 1 |   | 1 |

| S0 |   | S2     |   | 0 |   | Х |   | 0 |

| S1 | Ι | S2     | 1 | 0 | 1 | 0 | 1 | 0 |

```

S1 | S2 | 0 | 1 | 1

S1 | S1 | 1 | 0 | 1

S1 | S1 | 1 | 1 | 1

S2 | S2 | 0 | 0 | 0

S2 | S2 | 0 | 1 | 0

S2 | S1 | 1 | 0 | 0

S2 | S1 | 1 | 1 | 1

```

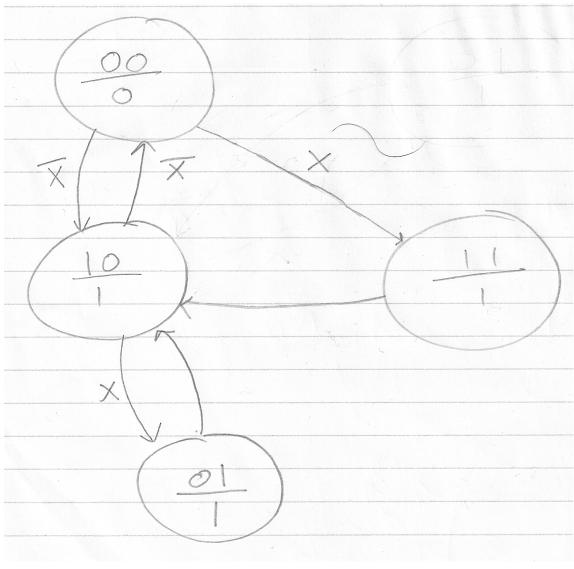

3.28)

CS | NS | X | Q

```

00 | 10 | 0 | 0

00 | 11 | 1 | 0

01 | 10 | X | 1

10 | 00 | 0 | 1

10 | 01 | 1 | 1

```

3.30)

- (b) 1 / 2 GHz = 500 psTolerable skew = 500 ps - 430 ps = 70 ps

- (c) The path through the bottom XOR gate is the

one we need to worry about. Since the contamination delay of the XOR gate is 55ps and the clock-to-Q minimum delay of the flip flop is 50ps. Therefore clock skew of up to 55ps + 50ps - 20ps = 85ps is tolerable.

(d) Here circuit is a balanced tree. It has a period of 70ps + 2 \* 100ps + 60ps = 330ps, a frequency of 3.03GHz. As for hold time violations, this new circuit adds an XOR in the shortest path, therefor the maximum tolerable skew is now, 55ps + 2 \* 50ps - 20ps = 135ps.

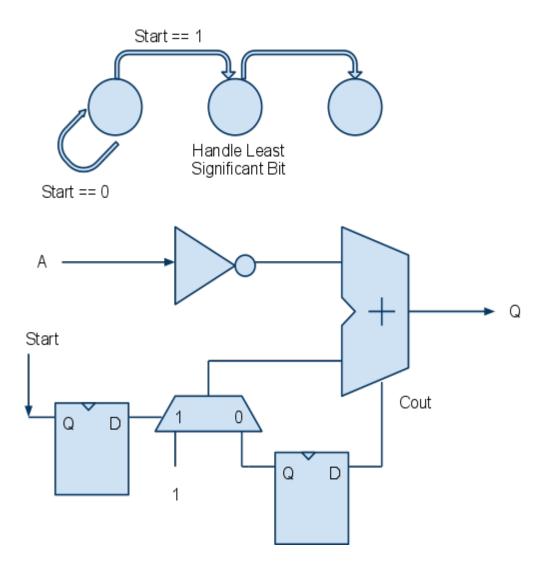

## 3.31)

OperatingFrequency = 1 / 110ps = 9.09GHz

- (b) ClockPeriod = 1 / (8GHz) = 125ps

TolerableSkew = 125ps 110ps = 15ps

- (c) Since the contamination delay of the Adder from Cin to either output is 15ps and the hold time is 10ps, there is tolerable skew of 5ps.

## 3.32)

Interview Question 3.2