| Name: |  |

|-------|--|

|       |  |

# EECS150: Components and Design Techniques for Digital Systems

University of California Dept. of Electrical Engineering and Computer Sciences Mid Term 2 – version A Fall 2004

| Last name:  | First name |

|-------------|------------|

| Student ID: | Login:     |

Lab meeting time: \_\_\_\_\_ TA's name: \_\_\_\_\_ (Sorry to ask this next question, but with 100 students packed closely together there may be a wide range of behavior.) Student to my left is \_\_\_\_\_ \_\_\_\_ Student to my right is \_\_\_\_\_\_ \_\_\_\_

No notes. No calculators! This booklet contains 9 numbered pages, including room to show your work. Please, no extra stray pieces of paper. The exam contains 5 substantive questions and 100 points, so just over 1 point per minute. Browse through the questions before you start. You have 1.5 hours, so relax, work thoughtfully and give clear answers. Good luck!

I certify that my answers to this exam are my own work. If I am taking this exam early, I certify that I shall not discuss the exam questions, the exam answers, or the content of the exam with anyone until after the scheduled exam time. If I am taking this exam in scheduled time, I certify that I have not discussed the exam with anyone who took it early.

Signature: \_\_\_\_\_

| Problem 1 [15]     |  |

|--------------------|--|

| Problem 2 [20]     |  |

| Problem 3 [15]     |  |

| Problem 4 [20]     |  |

| Problem 5 [30]     |  |

| <b>Total</b> [100] |  |

EECS150 FA04

Page 1 of 9

Name:\_\_\_\_\_

### Problem 1 (15). Arithmetic Circuit Design

- a. You are to build a POPCOUNT unit, shown below, which takes a single 8-bit input and produces a 4-bit output that is the number of bits that are 1 in the input. You are to construct it out of Full Adder (FA) and Half Adder (HA) blocks, not logic gates. Use as few FA's and HA's as possible. Clearly label your design.

- b. If you generalize your approach, how does the critical path of your design compare to that of an n-bit ripple carry adder? n-bit CLA?

in

$$\xrightarrow{8}$$

POPCOUNT  $\xrightarrow{4}$  out

$\xrightarrow{\psi \psi}$   $\xrightarrow{\psi \psi \psi}$   $\xrightarrow{\psi \psi \psi}$   $\xrightarrow{\psi \psi \psi}$   $\xrightarrow{a \ b \ ci}$   $\xrightarrow{FA}$   $\xrightarrow{co \ s}$   $\xrightarrow{\psi \psi}$   $\xrightarrow{\varphi \psi}$

Many solutions put all inputs into a Carry Propagate Adder.

The important part of the solution was to correctly combine bits with like place values. That is to say bits with a  $2^0$  significance cannot be grouped with bits with a  $2^1$  significance...

Other possible solutions involved using a balanced binary tree of 2, 2 and then 3 bit adders. However many people claimed  $O(\log(n))$  or O(n) performance, however the real performance of this tree is slightly less than  $O(\log^2(n))$

Make sure you understand what a half-adder and full-adder are. Neither is a ripple carry adder.

EECS150 FA04

Page 2 of 9

Name:\_\_\_\_

## Problem 2 (20). Circuit Delays

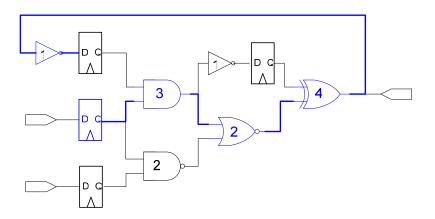

Determine the maximum clock rate for the circuit shown below. Assume the following:

- (1) The primitive inverter delay is 100 ps. All wire delays are 0.

- (2) The primitive delay of each gate is the number specified inside the gate. It is in units of primitive inverter delays.

- (3) The actual delay of a gate in the circuit is a linear function of its primitive gate delay and its fanout: Actual delay = primitive delay + 0.25 \* (# of fanouts)

- a. Any logic gate, flip-flop or output port counts as one fanout of a gate.

- b. For example, the XOR gate in the circuit below has a fanout of 2 (output port and inverter).

- c. The two inverters in the circuit have a fanout of 1 (flip-flop input).

- d. Flip-flop outputs incur fanout-related delays, just like gates.

- (4) Flip-flop setup time and clock-to-Q time is 2 inverter delays.

- (5) The maximum skew between any two clock inputs is 50 ps.

State clearly any other assumptions you make. Show your work.

Longest path: FF-AND-NOR-XOR-INV-FF Delay = 3 + 0.25(2) + 2 + 0.25(1) + 4 + 0.25(2) + 1 + 0.25(1) = 11.5 inv delays A path is defined and any series of combinational gates from any flip-flop output to any flip-flop input. This is not necessarily the delay around a loop. A path CANNOT GO THROUGH TWO FLIP-FLOPS.

FF delay = 2 + 0.25(2) + 2 = 4.5 (clock-to-Q + fanout delay + setup)

Clock skew = 0.5 Only applies if the path starts and ends at a different register.

Total delay = 11.5 + 4.5 + 0.5 = 16.5 inv delays or 1650 ps. Maximum Frequency = 1/1650ps = 606MHz

EECS150 FA04

Mid II

Page 3 of 9

Name:\_\_\_\_\_

## Problem 3 (15). Memory

Describe each of the steps involved in a DRAM read operation. (We are looking for a single brief sentence or two for each major step.)

- Prior to the read, OE\_l and WE\_l are disasserted (OE\_l = 1, WE\_l = 1) and the DRAM chip is essentially inactive.

- Row address is provided. After row address becomes valid, RAS is asserted (RAS = 1)

- Column address is provided. After Column address becomes valid, CAS is asserted (CAS = 1)

- Output enable is asserted (OE\_l = 0)

- Value of selected bits causes a small change in the precharged value on the line which is detected and amplified by the output driver or "sense amp"

- After a delay (of length specified by the data sheet), output data is latched

- Internally, the values read from the selected row are restored

- RAS and CAS are de-asserted

### Problem 4 (20). Understanding verilog

It is your job to find all 10 errors in the verilog fragment below, and suggest corrections for each error. The exact function of the FSM doesn't matter.

An error is counted as anything where a single continuous block of text is **missing or wrong**. This means that an error may span multiple lines, but there will be no correct text between the lines.

```

module ShiftRegister(Clock, Reset, SIn, POut);

Clock, SIn, Reset;

input

Comment [GDG1]: Reset was

output

[7:0] POut;

neglected as an input. This was not an

intentional mistake, but you will still

receive points for it.

reg [7:0] POut;

Comment [GDG2]: Must be declared

as a "reg" if it is to be a register later.

always @ (posedge Clock) begin

if (Reset) POut <=

8'h00;

Comment [GDG3]: Used to be

else POut <= {POut[6:0], SIn};

"Reset or Sin" which doesn't work.

We need a register.

end

endmodule

Comment [GDG4]: Reset used to

be left out. Every register needs to have a

"Reset" input.

module FSM(In, Out, OutValid, Clock, Reset);

input

In, Clock, Reset;

Comment [GDG5]: Should be non-

[7:0] Out;

output

blocking assignment. Blocking

OutValid;

assignment only works for combinational

output

always blocks.

[1:0]

CurrentState, NextState;

req

Comment [GDG6]: We forgot a

ShiftReset, OutValid;

semicolon here. This was not a

req

purposeful error on our part, but you still

get credit if you caught it.

ShiftRegister

Shifter(

.SIn(In),

.POut(Out),

Comment [GDG7]: NextState

must also be a "reg" even though it is

.Clock(Clock),

not a register. This is because it is

.Reset(ShiftReset | Reset));

assigned in an always block.

Comment [GDG8]: These

STATE_Idle =

2'h0,

parameter

connections are not in the same order as

2'h1,

STATE_A =

the port list for the ShiftRegister

STATE B =

2'h2;

module. That means you need to specify

which connection goes to which port. (Or

always @ (posedge Clock) begin

reorder the connections)

if (Reset) CurrentState <=

STATE_Idle;

else CurrentState <=

NextState;

end

always @ (CurrentStat e or Out or In) begin

Comment [GDG9]: The signals Out

CurrentState;

NextState =

and In were missing from this

OutValid =

1'b0;

sensitivity list.

ShiftReset =

1'b0;

Comment [GDG10]: Some default

value should be specified here in case a

proper value is not given later. This will

case (CurrentState)

prevent latches.

STATE Idle: begin

if (In) begin

STATE_A;

NextState =

ShiftReset =

1'b1;

end

end

STATE_A: begin

EECS150 FA04

Page 5 of 9

Mid II

```

|                             | 1                                               | Name:                      |                                                                                                                                                                                                |

|-----------------------------|-------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s                           | <pre>if (Out[0] &amp; ~Out[7]) b</pre>          | STATE_B;<br>1'b1;<br>1'b1; | <b>Comment [GDG11]:</b> Used to be<br>"Valid" which is not an actual signal                                                                                                                    |

|                             | NextState =<br>OutValid =<br>ShiftReset =<br>nd | 2'bxx;<br>1'bx;<br>1'bx;   |                                                                                                                                                                                                |

| endcase<br>end<br>endmodule | •••••t                                          |                            | <b>Comment [GDG12]:</b> FSMs must<br>always include a default block to ensure<br>that 1) there are no latches and 2) the<br>logic generated by this always block<br>can be optimized properly. |

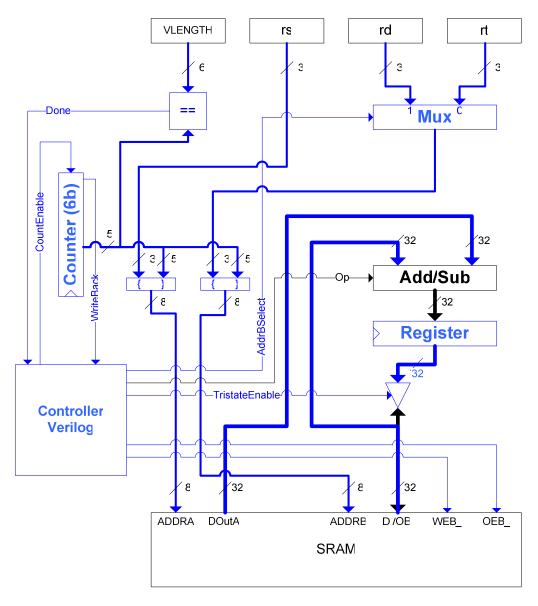

## Problem 5 (30). Controller design

In 1976 Seymore Cray introduced the Cray-1 Supercomputer that ran at an amazing 80 MHz and had all the characteristics that we associate with modern RISC processors. It also introduced the concept of vector registers, which are only beginning to appear in modern designs. In this problem you will design a portion of a vector unit.

Your machine has 8 vector registers, each containing 32 words of 32 bits in width. It has an adder unit that takes two 32-bit inputs and generates a 32-bit result. An additional VLENGTH register specifies the number of elements that are to be added. Thus the operation: VADD rd, rs, rt implements

```

FOR i from 0 to VLENGTH-1

REG[rd[i]] := REG[rs[i]] + REG[rt[i]]

```

Name:\_\_\_\_

**a.** Starting with the datapath skeleton shown below, you are to implement a controller for the VADD operation.

The vector registers are stored in a synchronous SRAM with two ports: port A is a read port and port B is a read/write port. The WriteEnable input (WEB\_) indicates whether the operation on port B is a write. The vector register numbers for the sources and destination, as well as VLENGTH, are provided to you in registers.

Complete the datapath with MUXes, tristates, wires, counters, latches, adders, flipflops or other components as required to implement the VADD operation.

EECS150 FA04

Name:\_\_\_\_

**b.** Starting with the verilog skeleton below, implement your controller for your datapath.

| module VADD(                                 | Clock, Reset,<br>WEB_, OEB_,<br>TristateEnable, Op, Add<br>WriteBack, CountEnable, |                                            |

|----------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------|

| input                                        | Clock, Reset;                                                                      |                                            |

| output<br>output<br>input<br>output<br>input | WEB_, OEB_;<br>TristateEnable, O<br>WriteBack;<br>CountEnable;<br>Done;            | p, AddrBSelect;                            |

| parameter                                    | OP_Add =<br>OP_Sub =                                                               | 1'b0,<br>1'b1;                             |

| assign<br>assign                             | WEB_ =<br>OEB_ =                                                                   | ~(WriteBack & ~Done);<br>WriteBack   Done; |

| assign<br>assign<br>assign                   | TristateEnable =<br>Op =<br>AddrBSelect =                                          | WriteBack;<br>OP_Add;<br>WriteBack;        |

| assign<br>endmodule                          | CountEnable =                                                                      | ~Done;                                     |

For this problem we accepted answers with either this simple Verilog based controller, and the more complicated datapath shown above or a similar solution but with a simpler datapath and a more complicated controller. The solution here shows the ideal division between datapath and controller, however we did not require you to divide it this way. In a real system the division would depend also on the other commands which had to be implemented on the datapath.

Those of you who took 3 cycles per addition also received full credit

| Grading Scale<br>Datapath |                       |

|---------------------------|-----------------------|

| 3 -                       | 3 Data busses to addr |

| 3 -                       | Tri-state for D/IOB   |

| 3 -                       | Concatenate addresses |

- 3 -Mux for the ADDRB line

- 1 -Correct operation (Add/Sub)

- 3 -Comparator for counter

#### Control

- Counter 3 -

- 3 -Read State/Write State

- 2 -Idle State/Done State

EECS150 FA04

Mid II

Page 9 of 9