# # The "clock" keeps the FSM synchronized. \*\*Ine "clock" keeps the FSM synchronized. \*\*Ine "clock" keeps the FSM synchronized. \*\*Clock signal "falling edge" Orange: values of combinational logic can change

- \* When the clock goes "BONG!" the FSM will change state

- # The time from one rising edge to another is called the "clock cycle" time.

5 150 - Spring '01 - Lab Lecture 2

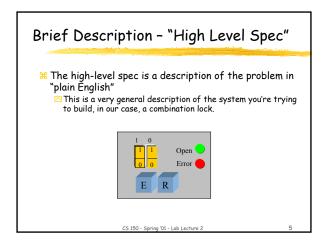

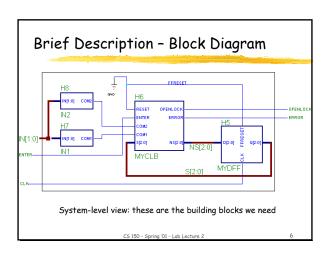

### Brief Description - MyCLB

- # CLB = Combinational Logic Block => AND, OR, INV...

- # The MyCLB block acts as the controller for our lock, it's the brains

- # Truth table and logic equations are in the printout <a>Implement this block during lab time</a>.

- ₩ KISS-Keep It Simple & Stupid

- △Use the "multi-level" equations, they're much easier to debug

CS 150 - Spring '01 - Lab Lecture 2

10

# Brief Description - FSM \*\*CONTROL OF STATE COMPLETE COMP

# Brief Description - the IN\* blocks

- # The IN1 and IN2 blocks compare the code the user inputs to the "secret" code that will open the lock.

- # Choose your own combination. Write it down.

- **X** The two combinations must be different:

- **△**Good: 01 11

- □ Bad: 10 10

- # IN1 and IN2 are very simple blocks. Just some AND gates and inverters.

CS 150 - Spring '01 - Lab Lecture 2

# ToDo's - What you need for credit

- # Enter the IN1, IN2, MyCLB schematics

- # Make a test script for your CLB. Run it. Make sure it's correct.

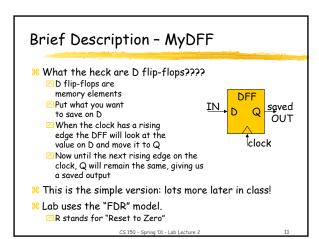

- **38** Make the MyDFF block.

- # Wire up all the individual pieces you just made.

- # Write a script to simulate scenarios on the full lock

- Successful/Unsuccessful entries of the combination

- ☐ Use of the RESET and ENTER buttons

- Do all the paths on the state diagram work correctly?

- Create a log file to show your TA

CS 150 - Spring '01 - Lab Lecture 2

12

# Hints, Tips, and Tricks

- **#** Buses are your friends.

- △CS150 buses: collections of wires that have a similar purpose

- ○Usually same wire name + a number, as in DATA7, DATA6, ... DATA1, DATA0

- ☐ Simplify, simplify, simplify...

- # Scripts are your friends.

- Note: the pipe character " | " will comment out a line.

- # Don't print things!

- # Xilinx software is buggy. When in doubt, restart it.

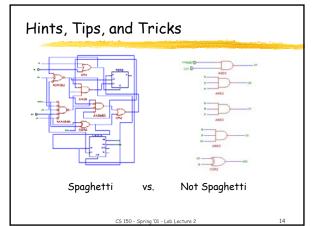

- # Don't draw spaghetti wires =>

- □ Too easy to mislabel wires

- △ Harder to debug

CS 150 - Spring '01 - Lab Lecture 2

13

The End... for now.

Ya ain't seen nuthin' yet...