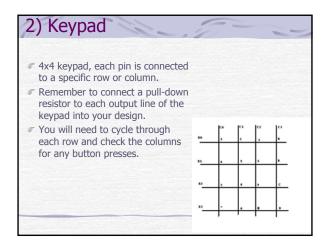

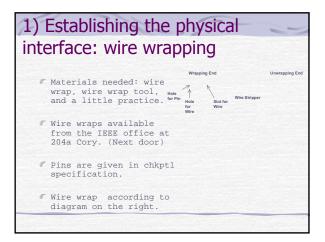

## Keypad and LCD Interface 1) Physical Interface 2) Keypad 3) LCD (Optrex DMC-24227) 4) Design Structure and FSM 5) Design implementation 6) Hints and cautions

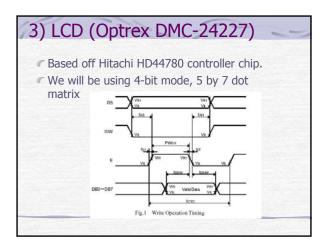

|                       | 1110                              |            |      | Vcc=5.0V±1 |      |

|-----------------------|-----------------------------------|------------|------|------------|------|

| Parameter             | Symbol                            | Conditions | Min. | Max.       | Unit |

| Enable Cycle Time     | teye                              | Fig. 1, 2  | 500  | 3          | ns   |

| Enable Pulse Width    | PWEH                              | Fig. 1, 2  | 230  | 3          | ns   |

| Enable Rise/Fall Time | t <sub>Er</sub> , t <sub>Ef</sub> | Fig. 1, 2  | 77.5 | 20         | ns   |

| Address Setup Time    | tas                               | Fig. 1, 2  | 40   | =          | ns   |

| Address Hold Time     | tan                               | Fig. 1, 2  | 10   | .=:        | ns   |

| Write Data Setup Time | t <sub>DSW</sub>                  | Fig.1      | 80   | .=:        | ns   |

| Write Data Hold Time  | $t_{\mathrm{DHW}}$                | Fig.1      | 10   | 3          | ns   |

| Read Data Delay Time  | time                              | Fig.2      | 77.0 | 160        | ns   |

| Read Data Hold Time   | tone                              | Fig.2      | 5    |            | ns   |

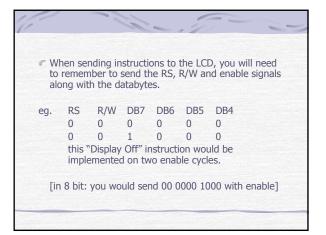

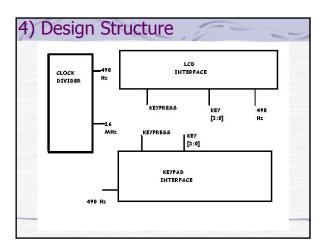

- The enable pulse can be created using a 490 Hz clock.

- In the 4-bit mode, the control bytes are sent on consecutive enable cycles. The most significant 4 bits (DB[7:4]) are sent first, followed by the remaining 4 bits of the byte (DB[3:0]).

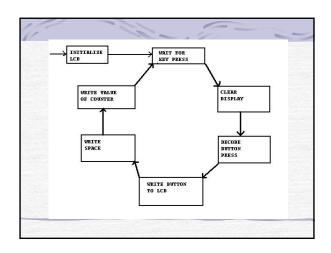

At start up, (after downloading to the Xilinx chip) the LCD must be initialized before displaying anything.

Remember to clear line whenever you give it a new input.

You can ground R/W since we are not reading from the LCD in this checkpoint.

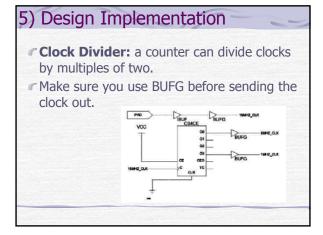

## 6) Hints and Cautions

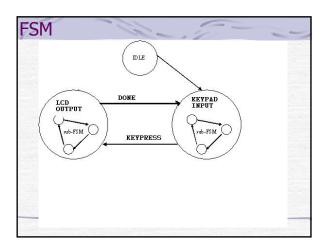

- Really sit down and plan your FSM before doing anything in Xilinx. Write it down, draw state diagrams... etc understand what's suppose to happen.

- Minimize as much as possible.

- Look at error messages.

- The oscilloscope is your friend!

- Use a potentiometer for the LCD power (if there's nothing on the screen, give the potentiometer a tweak).