|                       |                                   |            |      | Vcc=5.0V±10 |       |

|-----------------------|-----------------------------------|------------|------|-------------|-------|

| Parameter             | Symbol                            | Conditions | Min. | Max.        | Units |

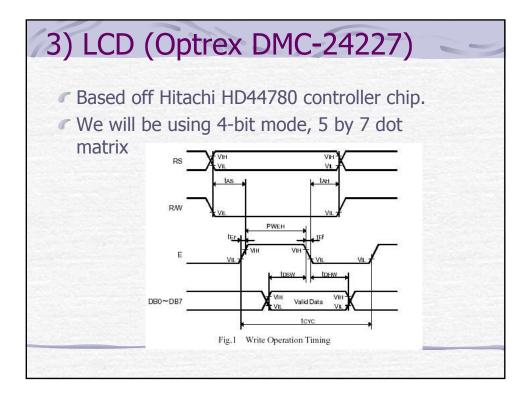

| Enable Cycle Time     | teve                              | Fig.1, 2   | 500  | -           | ns    |

| Enable Pulse Width    | PWEH                              | Fig. 1, 2  | 230  |             | ns    |

| Enable Rise/Fall Time | t <sub>Er</sub> , t <sub>Ef</sub> | Fig. 1, 2  | -    | 20          | ns    |

| Address Setup Time    | t <sub>AS</sub>                   | Fig.1, 2   | 40   |             | ns    |

| Address Hold Time     | t <sub>AH</sub>                   | Fig.1, 2   | 10   |             | ns    |

| Write Data Setup Time | t <sub>DSW</sub>                  | Fig.1      | 80   |             | ns    |

| Write Data Hold Time  | tonw                              | Fig.1      | 10   |             | ns    |

| Read Data Delay Time  | LDDR                              | Fig.2      |      | 160         | ns    |

| Read Data Hold Time   | tone                              | Fig.2      | 5    | 14.1        | ns    |

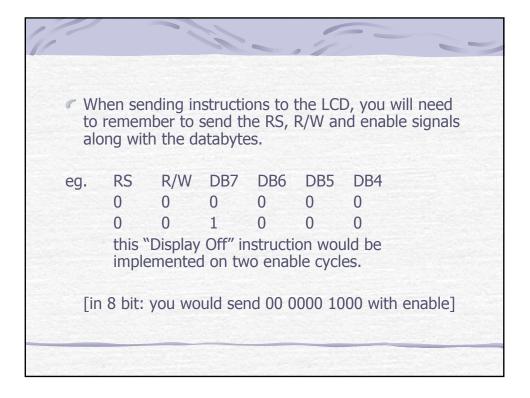

In the 4-bit mode, the control bytes are sent on consecutive enable cycles. The most significant 4 bits (DB[7:4]) are sent first, followed by the remaining 4 bits of the byte (DB[3:0]).