## Lecture 21

Today we will

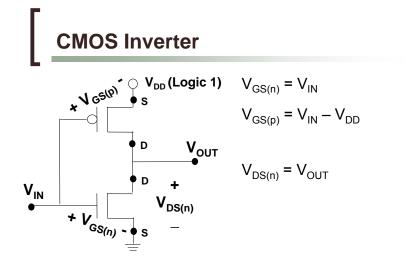

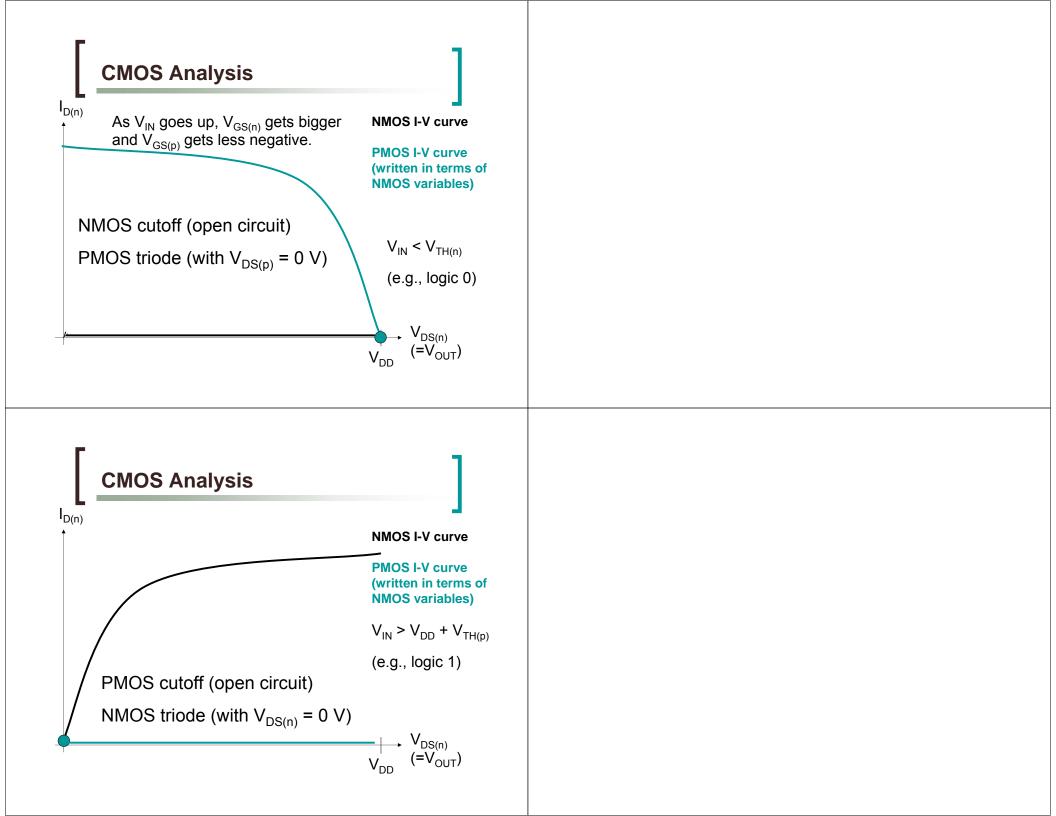

- Revisit the CMOS inverter, concentrating on logic 0 and logic 1 inputs

- Come up with an easy model for MOS transistors involved in CMOS digital computation

- Investigate the "complementary" nature of CMOS logic circuits

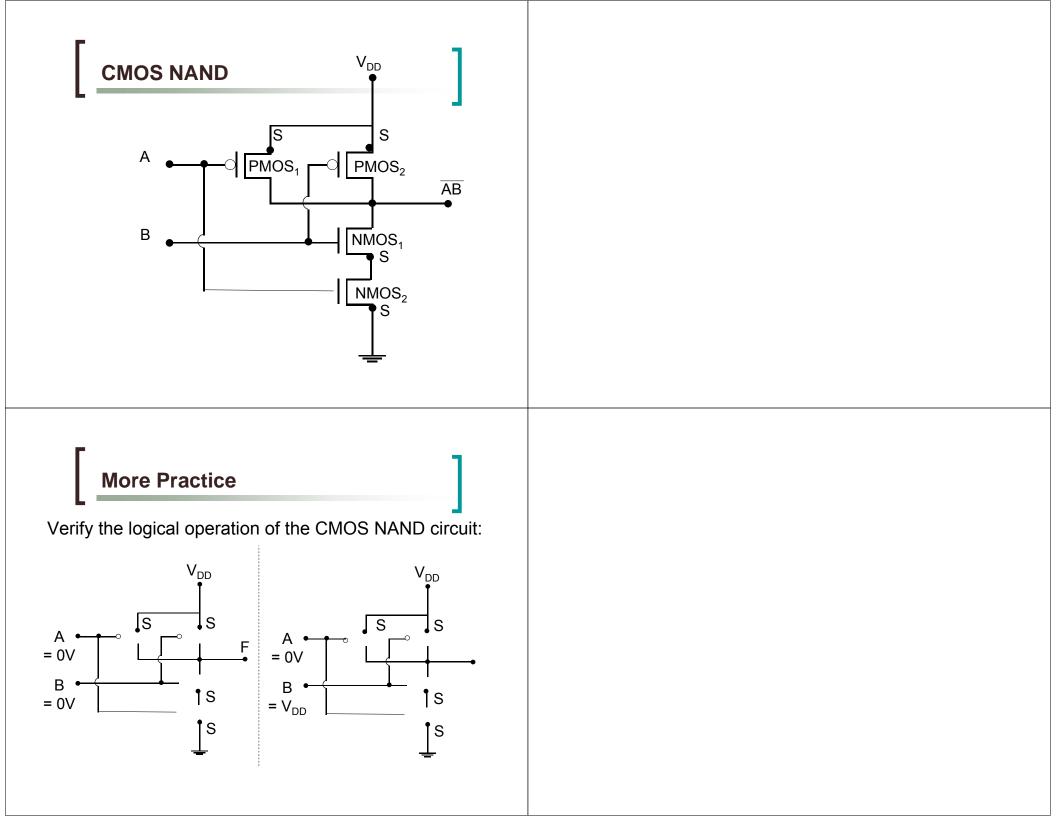

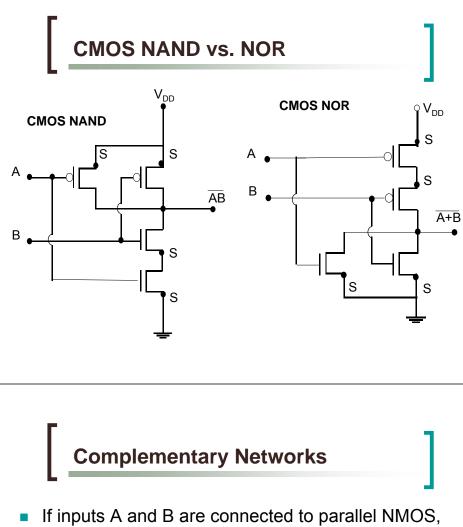

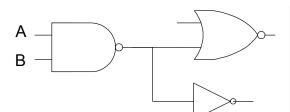

- Introduce CMOS NAND and NOR

- Determine the effective R and C for CMOS logic transitions

# Model for Digital Computation

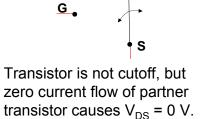

This leads us to a simpler model for transistors in CMOS circuits, when V<sub>IN</sub> is fully logic 0 or logic 1.

Transistor is cutoff. Zero current flow.

• D

$V_{GS}$  = 0 V

G

$V_{GS} = V_{DD}$  (for NMOS)  $V_{GS} = -V_{DD}$  (for PMOS)

#### Practice

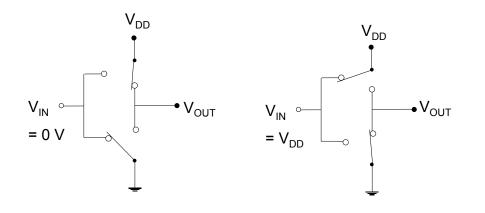

Use this model to find V<sub>OUT</sub> for the circuits below.

# **More Practice**

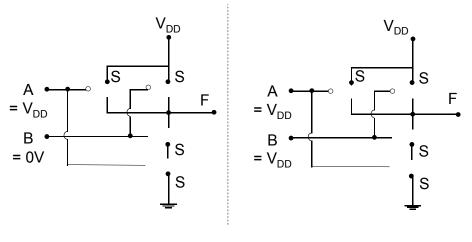

Verify the logical operation of the CMOS NAND circuit:

### **CMOS Networks**

- Notice that V<sub>OUT</sub> gets connected to either V<sub>DD</sub> or ground by "active" (not cutoff) transistors.

- We say that these active transistors are "pulling up" or "pulling down" the output.

- NMOS transistors = pull-down network

- PMOS transistors = pull-up network

- These networks had better be complementary or V<sub>OUT</sub> could be "floating"—or attached to both V<sub>DD</sub> and ground at the same time.

- A and B must be connected to series PMOS.

- The reverse is also true.

- Determining the logic function from CMOS circuit is not hard:

- Look at the NMOS half. It will tell you when the output is logic zero.

- Parallel transistors: "like or"

- Series transistors: "like and"

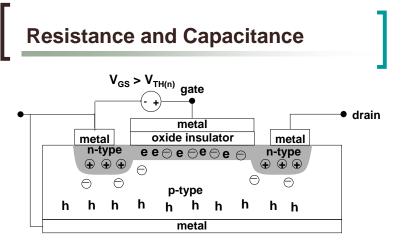

- The separation of charge by the oxide insulator creates a natural capacitance in the transistor from gate to source.

- The silicon through which I<sub>D</sub> flows has a natural resistance.

- There are other sources of capacitance and resistance too.

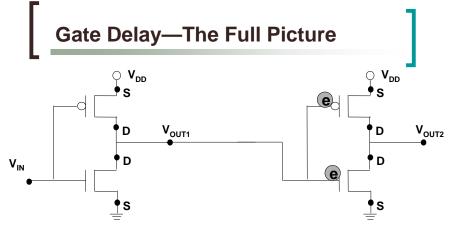

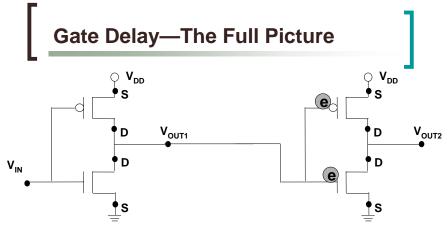

- Suppose V<sub>IN</sub> abruptly changed from logic 0 to logic 1.

- V<sub>OUT1</sub> may not change quickly, since is attached to the gates of the next inverter.

- These gates must collect/discharge electrons to change voltage.

- Each gate attached to the output contributes a capacitance.

- Where will these electrons come from/go to?

- No charges can pass through the cutoff transistor.

- Charges will go through the pull-down/pull-up transistors to ground. These transistors contribute resistance.

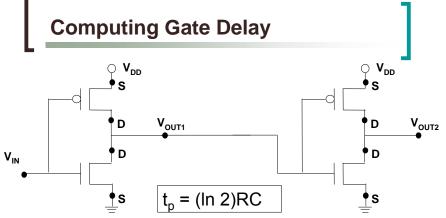

- 1. Determine the capacitance of each gate attached to the output. These combine in parallel. Higher **fan-out** = more capacitance.

- 2. Determine which transistors are pulling-up or pulling-down the output. Each contributes a resistance, and may need to be combined in series and/or parallel.

- 3. The C from 1) and R from 2) are the RC for the  $V_{\text{OUT1}}$  transition.

## Example

• Suppose we have the following circuit:

If A and B both transition from logic 1 to logic 0 at t = 0, find the voltage at the NAND output, V<sub>OUT</sub>(t), for t ≥ 0. Logic 0 = 0 V Logic 1 = 1 V NMOS resistance  $R_n = 1 k\Omega$ PMOS resistance  $R_p = 2 k\Omega$ Gate capacitance  $C_G = 50 pF$