Name Solotion

**EE 40**

# Final Exam

May 23, 2003

# PLEASE WRITE YOUR NAME ON EACH ATTACHED PAGE PLEASE SHOW YOUR WORK TO RECEIVE PARTIAL CREDIT PLEASE DO NOT LEAVE DURING LAST 30 MINUTES OF EXAM PERIOD

| TOTAL: 105 Points Possible    | <del></del> | (Yes,       | you can scor | e over 100%) |          |

|-------------------------------|-------------|-------------|--------------|--------------|----------|

|                               |             | •           |              |              |          |

| Cha                           | ice 1 (     | Choice 2    | Choice 3     | Choice 4     | Choice 5 |

| Problem 6: 45 Points Possible |             |             |              |              |          |

| Problem 5: 15 Points Possible |             |             |              |              |          |

| Problem 4: 15 Points Possible | <u> </u>    | <u> </u>    |              |              |          |

| Problem 3: 10 Points Possible | <del></del> | <del></del> |              |              |          |

| Problem 2: 10 Points Possible |             |             |              |              | •        |

| Problem 1: 10 Points Possible |             |             |              |              |          |

| Name |   |

|------|---|

|      | _ |

## Problem 1: 10 Points Possible

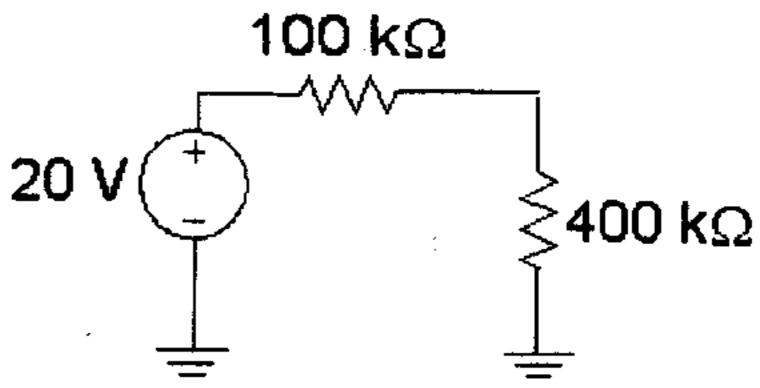

a) Suppose I measure the voltage over the 400 k $\Omega$  resistor using a voltmeter with an internal resistance of 1.2 M $\Omega$ . What is the voltage reading on the voltmeter?

Voltmeter placed in parallel with measured element:

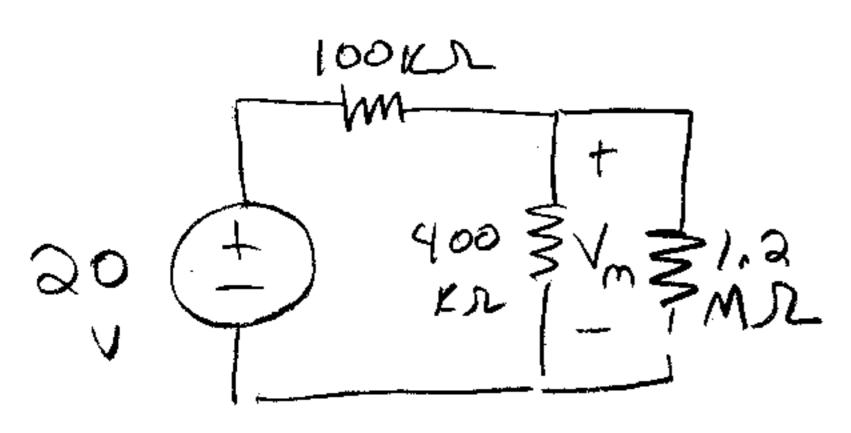

b) I have attached a diode to the output of a logic gate, so it will light up when the output is high. Assume the large signal model for the diode, with  $V_F = 1 \text{ V}$ .

Find the range of values for R that will satisfy the following condition: The diode must have between 20 mA and 50 mA of current when the logic output is between 4 V and 5 V.

| <br>        |

|-------------|

|             |

| <del></del> |

## **Problem 2:** 10 Points Possible

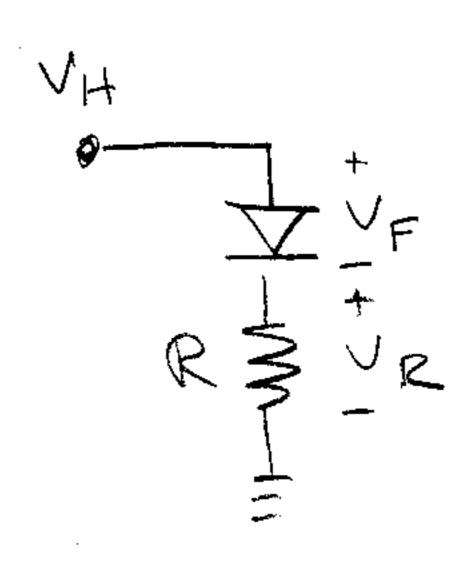

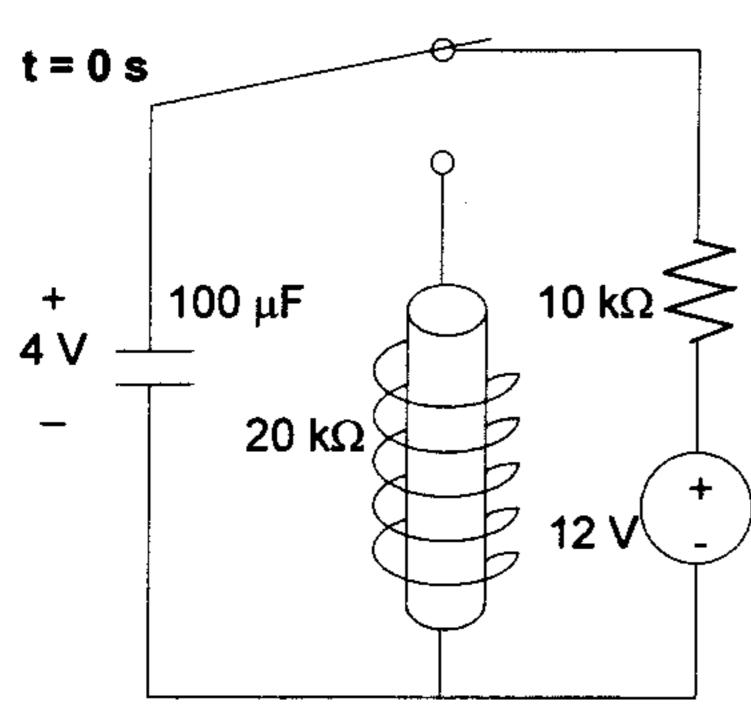

Consider the relay circuit.

The 100 µF capacitor is connected to the 12 V source and 10 k $\Omega$  resistor when the switch is up, and connected to the 20 k $\Omega$  resistor representing the electromagnet coil when the switch is down.

The electromagnet keeps the switch in the "down" position until the coil voltage drops to 4 V; at that point, the magnet releases the switch and it springs back up.

4 V with polarity shown, and the switch is up.

Suppose that at t = 0, the capacitor has voltage

At t = 1 second, I flip the switch down (and let go).

How long will the switch stay down?

Capacitor starts discharging at t= 15 What is initial capacitor voltage at t=15) Capacitor was charsing for t=0 to t=1 V(t) = 4 ve + 12 V(1-e-t/r) T=100mF - 10KS Vn (15) = 4 Vc -15 + 12 V(1-e How long does discharsing from 9.040 to 40 take? 4v = 9.04v e th T=100AF.20KR=25 t = -25.12 41 = (1.635

| Name | <br> |

|------|------|

|      | <br> |

#### Problem 3: 10 Points Possible

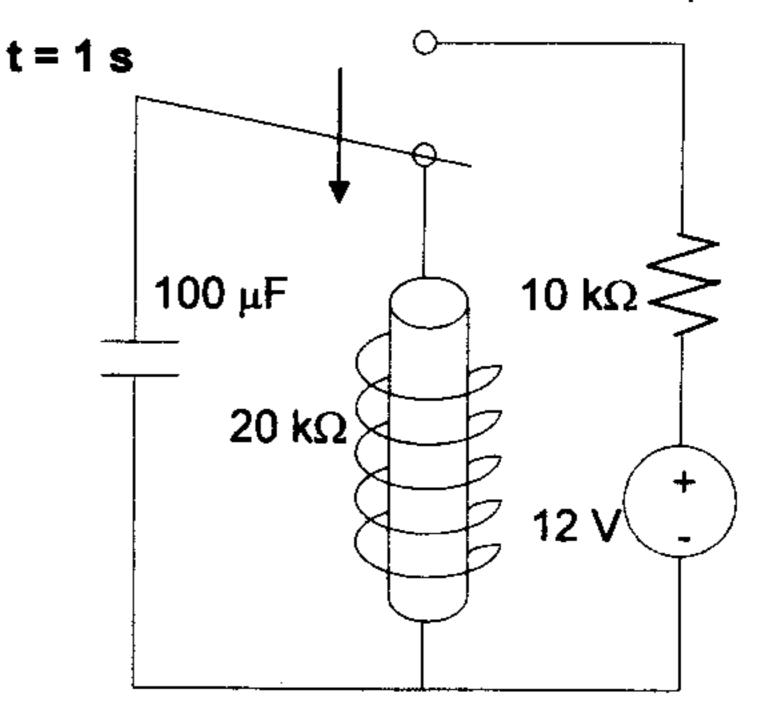

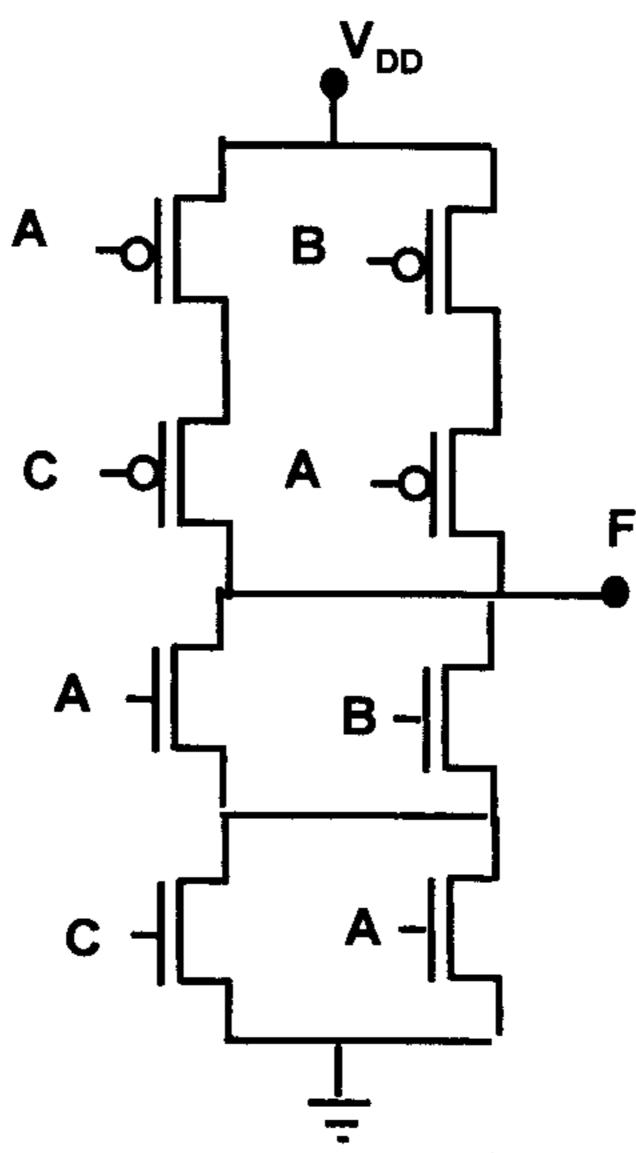

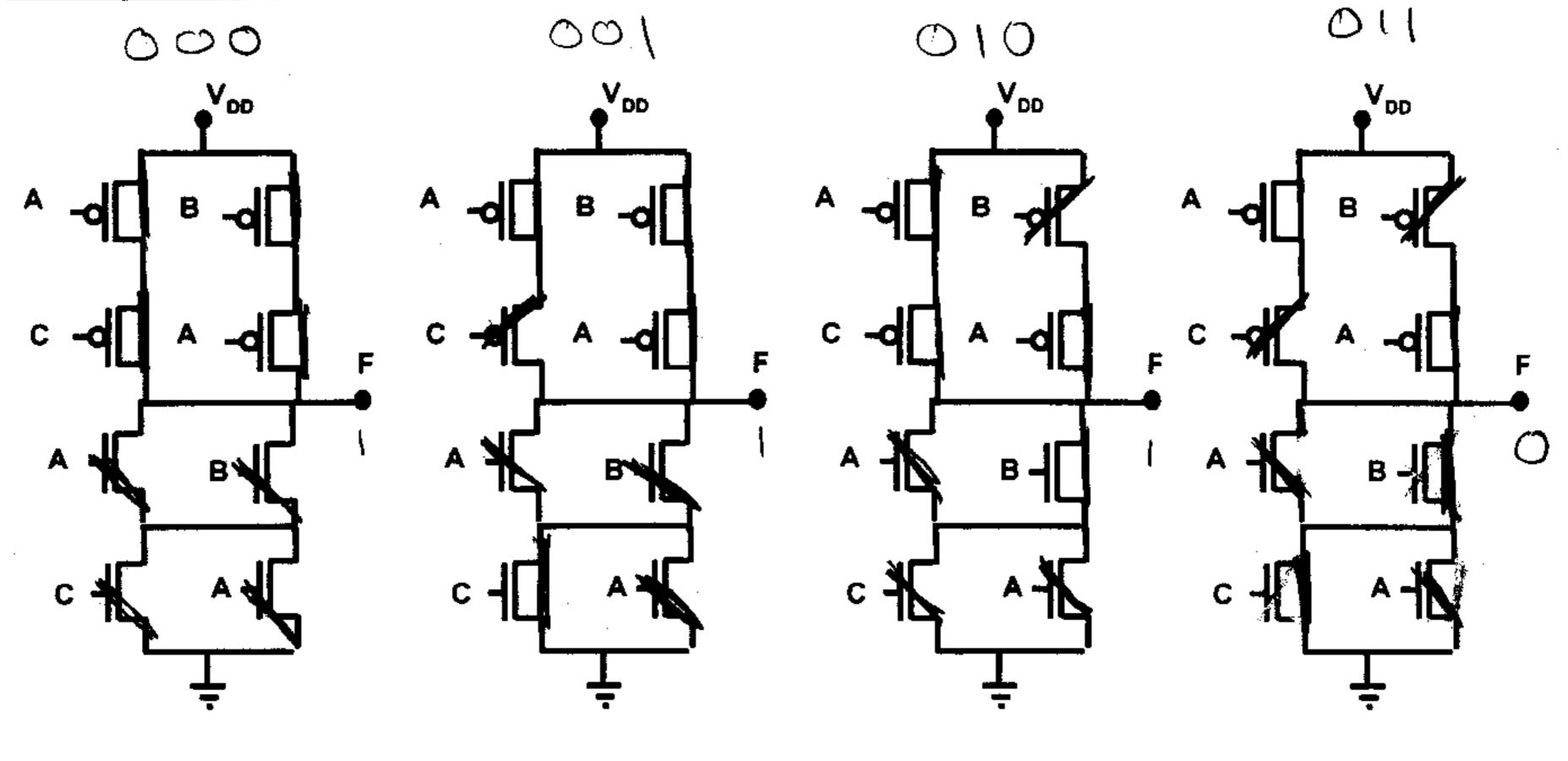

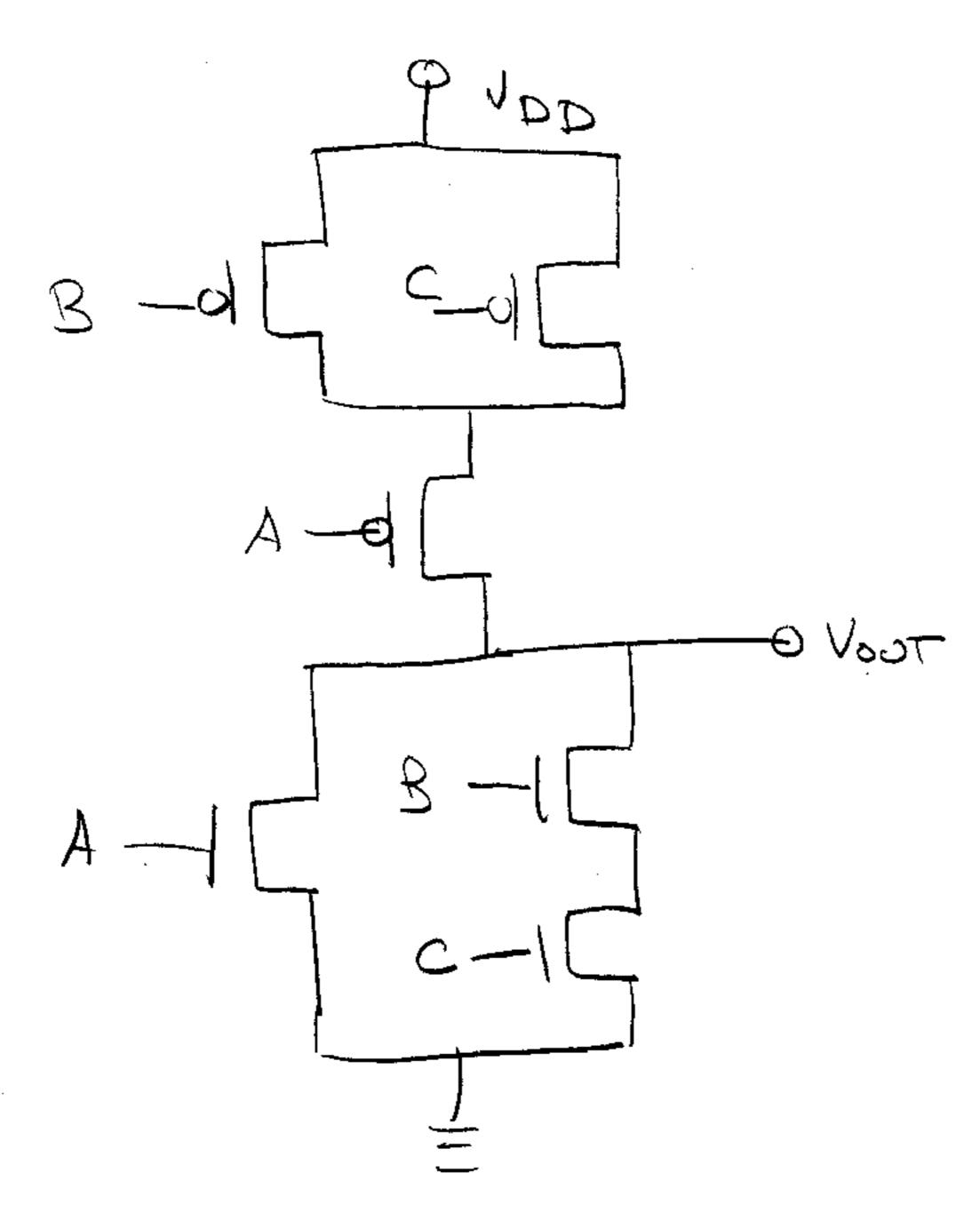

Determine whether the circuit below performs a logical operation.

If the circuit does perform a logical operation,

- a) give the Boolean function it computes, and

- b) design a circuit that computes the same function using fewer transistors.

If the circuit does not perform a logical operation,

- a) give a set of inputs that results in an invalid output, and

- b) rearrange the inputs so that the circuit does perform some logical operation.

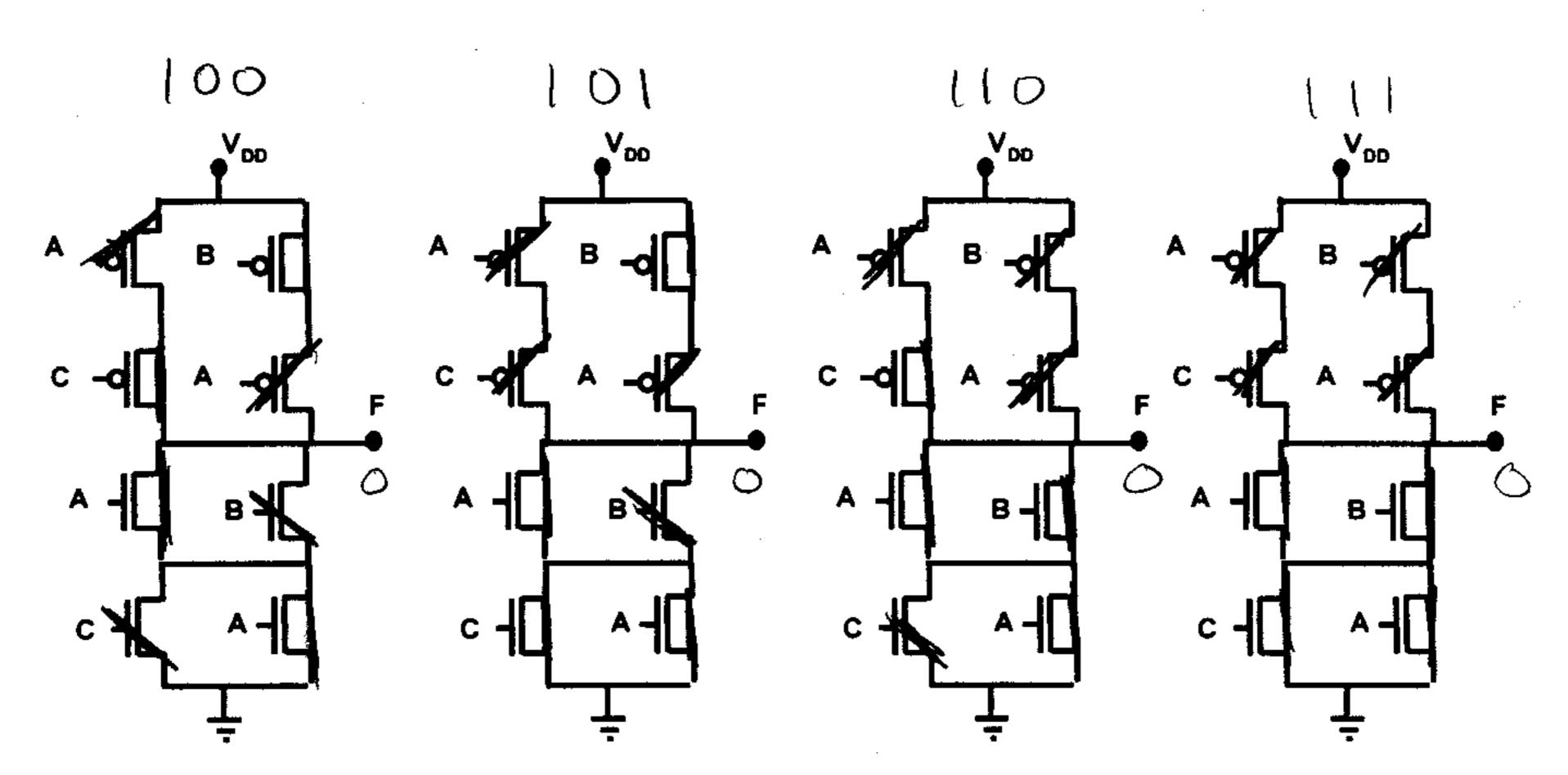

For your convenience, 8 copies of this circuit are given on the next page. Assume that all PMOS transistors have source terminal on top, and all NMOS transistors have source terminal on the bottom.

To connect F to VDD:  $F = AC + \overline{AB}$ To connect F to ground:  $\overline{F} = (A+B)(C+A)$ Use De Morgan:  $F = (\overline{A+B})(C+A) = (\overline{A+B}) + (\overline{C+A})$  $= \overline{AB} + \overline{CA}$  Agrees with PMOS half,

Logical operation portornel: F=ĀC+ĀB

## Problem 3 Workspace

| Name |  |

|------|--|

|      |  |

|      |  |

## **Problem 3 Workspace**

Simpler expression is F = A(B+C)

PMOS: A input in series with (Binput, Cinput in parallel)

NMOS is complement: A input in parallel with (Binput, Cinput in parallel with (Binput, Cinput in series)

| Name |  |

|------|--|

|      |  |

|      |  |

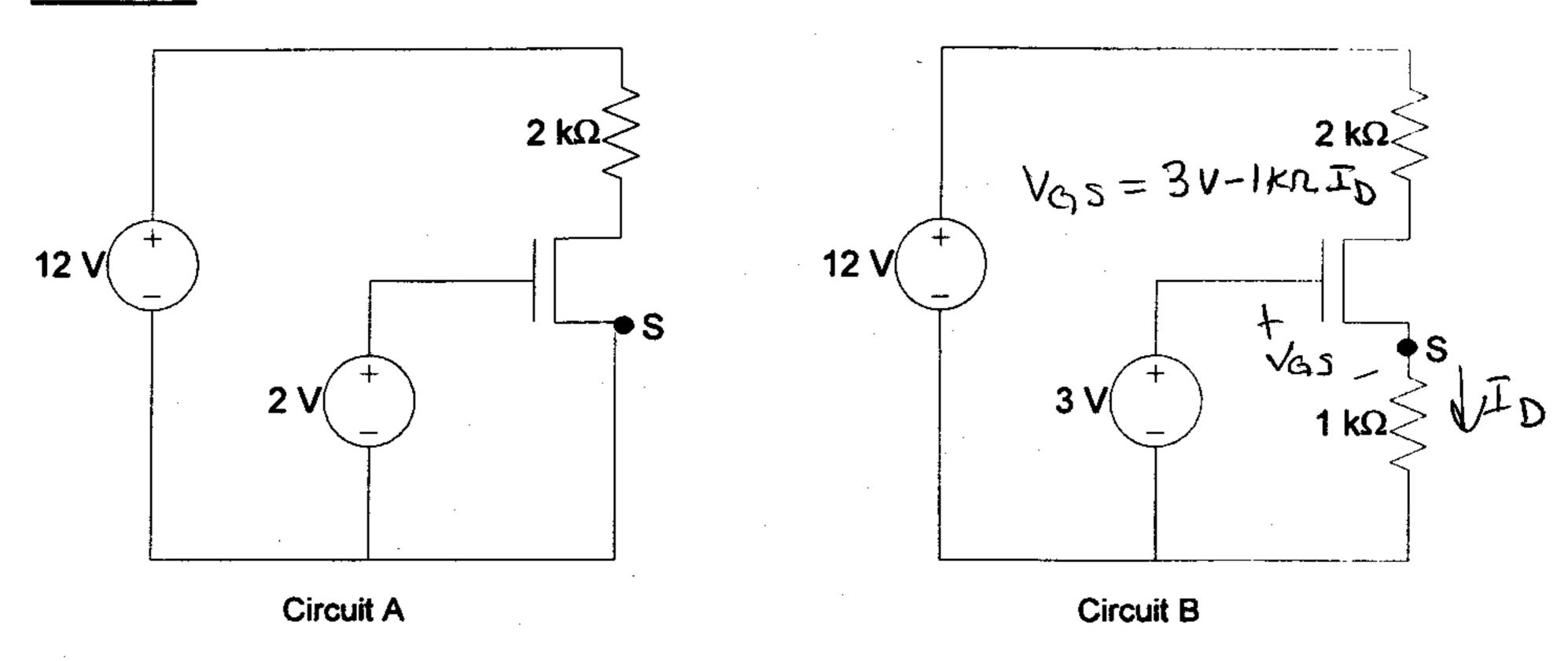

#### Problem 4: 15 Points Possible

Consider the two circuits above, where W/L  $\mu_N$  C<sub>OX</sub> = 2 mA/V<sup>2</sup>, V<sub>TH</sub> = 1 V, and  $\lambda$  = 0 for both transistors, at room temperature. In this situation, both transistors are in saturation, with constant I<sub>D</sub> = 1 mA.

Suppose the circuit temperature rises significantly, doubling µ (not realistic, but bear with me).

Find the  $I_D$  values for the higher temperature:  $I_{D(A)}$  for Circuit A and  $I_{D(B)}$  for Circuit B.

$$I_{D_A} = V_2 \cdot \frac{V}{L} L_N Cox (V_{GS} - V_{TH})^2 = V_2 \cdot 4mA/u^2 (2V-1V)^2$$

$I_{D_A} = 2mA$   $V_{DSA} = RV - 2KL \cdot 2mA = 8V OK$ .

$I_{D_B} = V_2 \cdot \frac{V}{L} L_N Cox (V_{GS} - V_{TH})^2 = V_2 \cdot 4mA/u^2 (3V-1KL_{D_B}-1V)^2$

$O = 2000 I_{D_B}^2 - (8+1) I_{D_B} + .008$   $I_{D_B} = 1.20mA$

$SolutionS^2 = I_{D_B} = \frac{2}{3} \cdot 28mA \cdot 1.20mA^2$

$V_{GSB}$  for  $I_{D_B} = \frac{2}{3} \cdot 28mA \cdot \frac{1}{3} \cdot \frac$

# Problem 5: 15 Points Possible

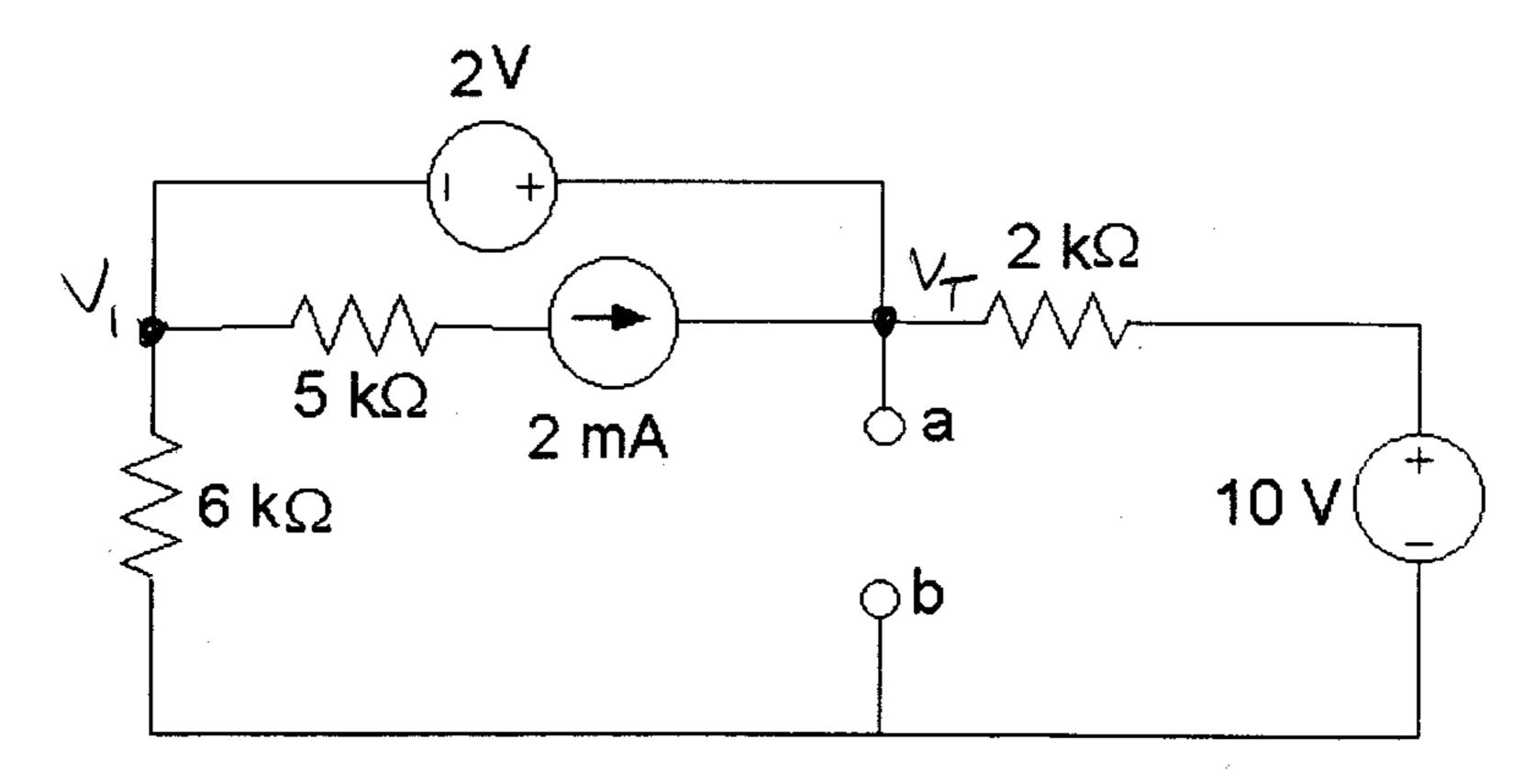

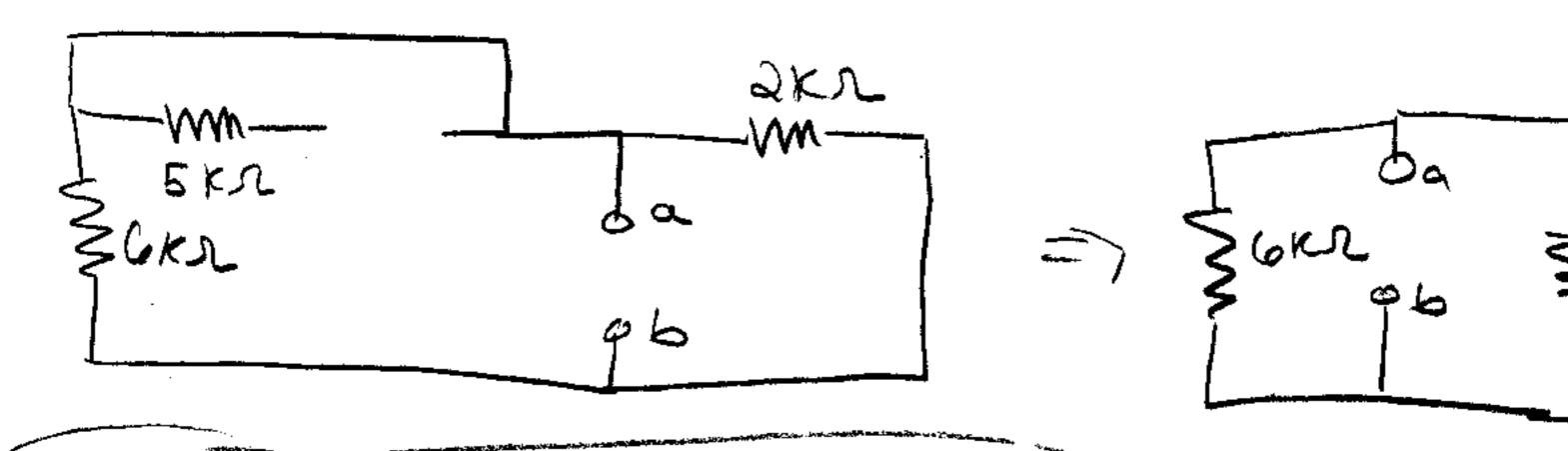

Find the Thevenin equivalent circuit with respect to points a and b for the circuit below.

Find open-circuit voltage from a to b: Nodal analysis with nodes above:

$$\frac{V_1}{6KR} + \frac{V_7 - 10}{2KR} = 0 \quad V_7 - V_1 = 2V \quad \frac{Solution:}{V_7 = 8V}$$

Supernode

$$V_1 = 6V$$

Find Rt by turning off sources &

Source transformations also work here.

| Name |  |

|------|--|

|      |  |

## Problem 6: 45 Points Possible

Complete 3 of the following 5 choices worth 15 Points each. If you complete more than 3 choices, your 3 highest-scoring choices will count towards your Problem 6 total.

## Problem 6 Choice 1:

Design a circuit for which

$$V_{OUT} = \sqrt{V_{IN}}$$

.

Your design only needs to work "on paper".

| Name |  |  |

|------|--|--|

|      |  |  |

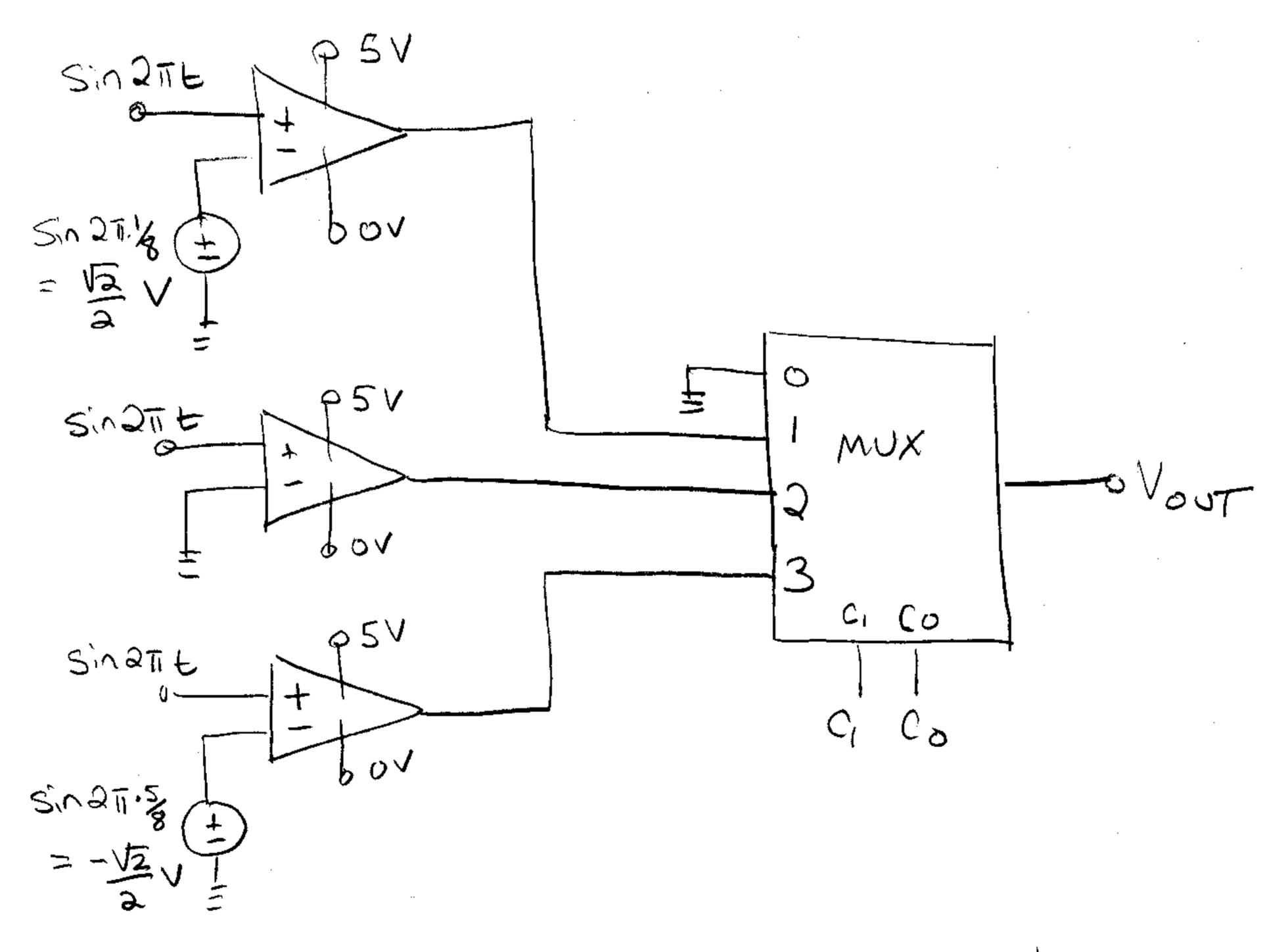

#### Problem 6 Choice 2:

You are given an input  $V_{IN} = \sin 2\pi t$ .

Design a circuit that creates 1 Hz square waves of duty cycle 25%, 50%, and 75%. (Duty cycle is the percentage of time that a square wave is high.) The low and high values for the square waves should be logic 0 (0V) and logic 1 (5 V) respectively.

The circuit output should be:

0 V when the binary control signal  $C_1$   $C_0$  = 0 0 25% duty cycle wave when  $C_1$   $C_0$  = 0 1 50% duty cycle wave when  $C_1$   $C_0$  = 1 0 75% duty cycle wave when  $C_1$   $C_0$  = 1 1.

You may use any of the circuits discussed in class, including the multiplexer.

If you use Schmitt Triggers, you must "trick" them to handle 0 or regative thresholds by adding negative offset voltage to ground + VDD terminals.

| Name |   |

|------|---|

|      | _ |

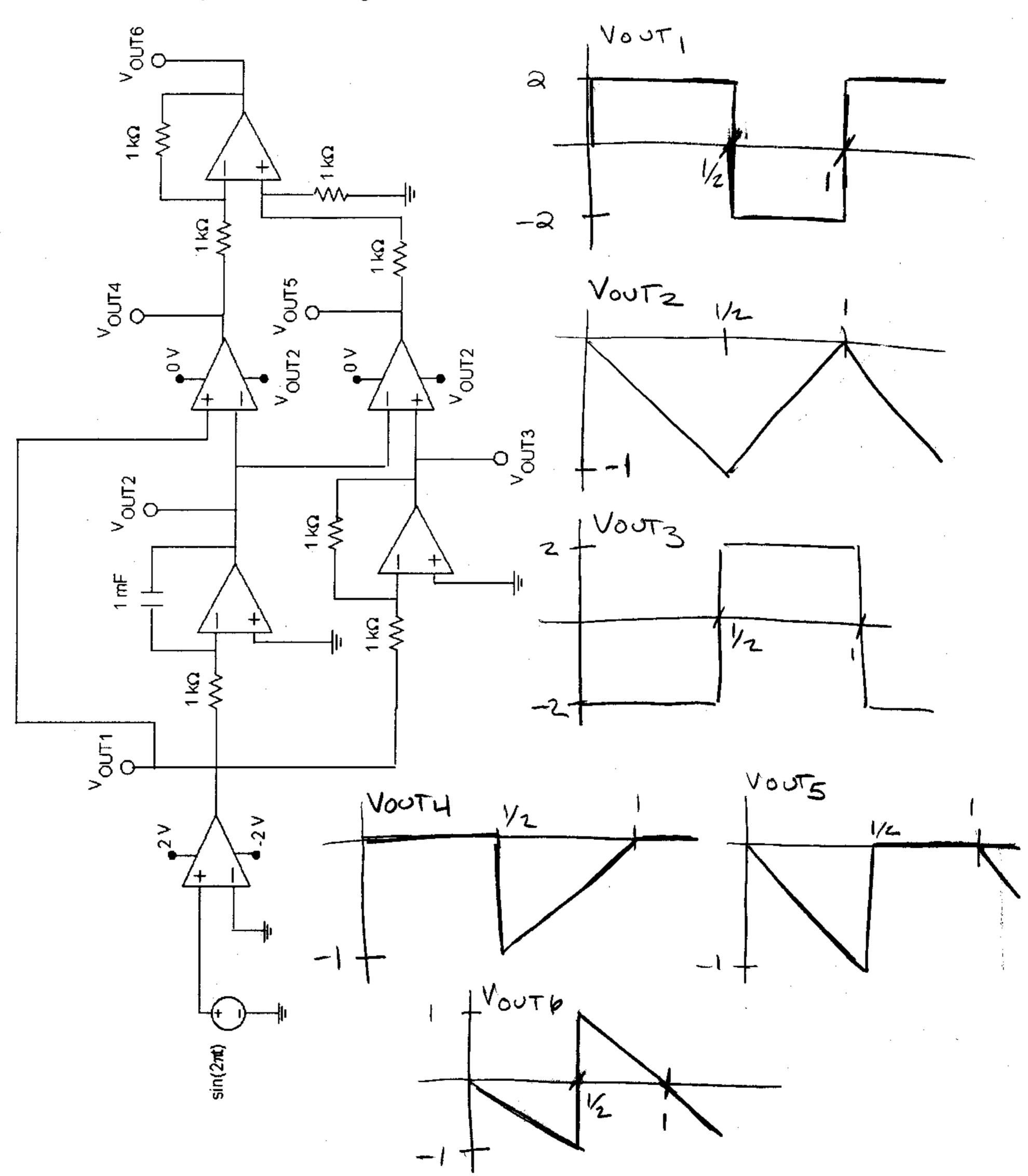

# **Problem 6 Choice 3**

Sketch  $V_{\text{OUT1}}$ ,  $V_{\text{OUT2}}$ ,  $V_{\text{OUT3}}$ ,  $V_{\text{OUT4}}$ ,  $V_{\text{OUT5}}$ , and  $V_{\text{OUT6}}$  for the following circuit.

Be sure to show peak values. Pay close attention to time intervals and +/- terminals on amplifiers.

Assume that the capacitor is discharged at t = 0. Use the ideal diode model.

| Name |      |      |  |

|------|------|------|--|

|      | <br> | <br> |  |

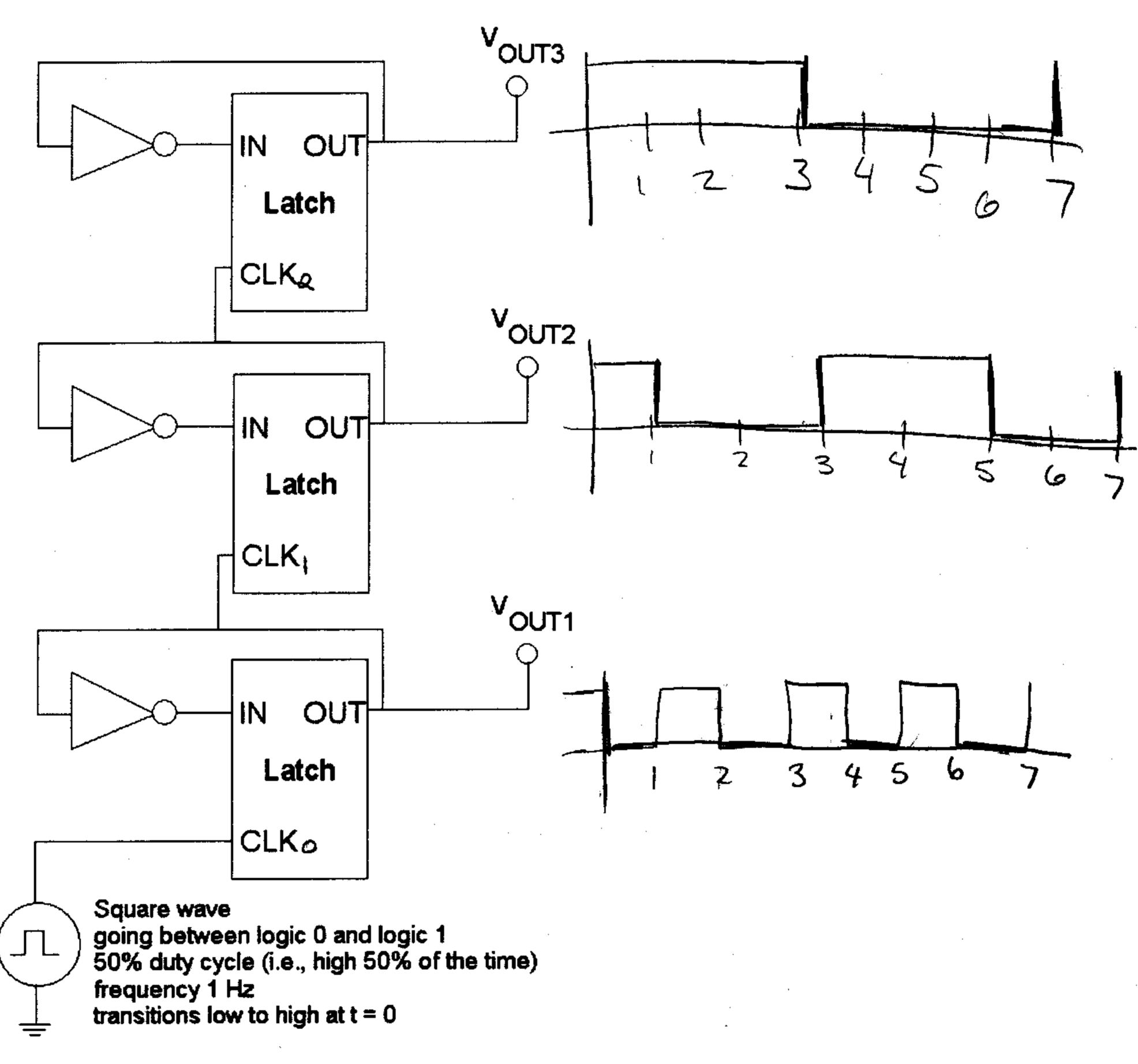

## **Problem 6 Choice 4**

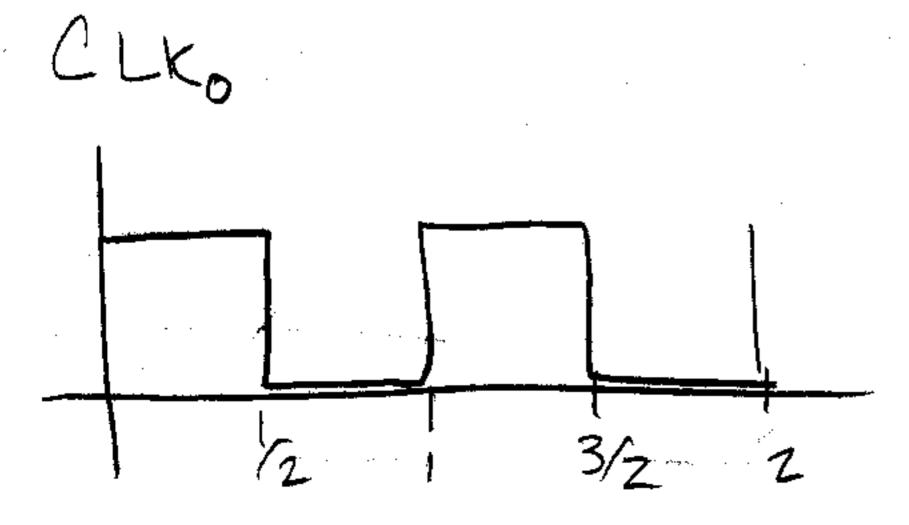

Sketch the logical voltages  $V_{OUT1}$ ,  $V_{OUT2}$ , and  $V_{OUT3}$  over a time period of 7 seconds. Assume that there is no delay in the latch; the output is refreshed the instant the clock signal goes high. Assume that all of the latches have an initial output of logic 1 just before t = 0.

| Name |

|------|

|------|

### Problem 6 Choice 5:

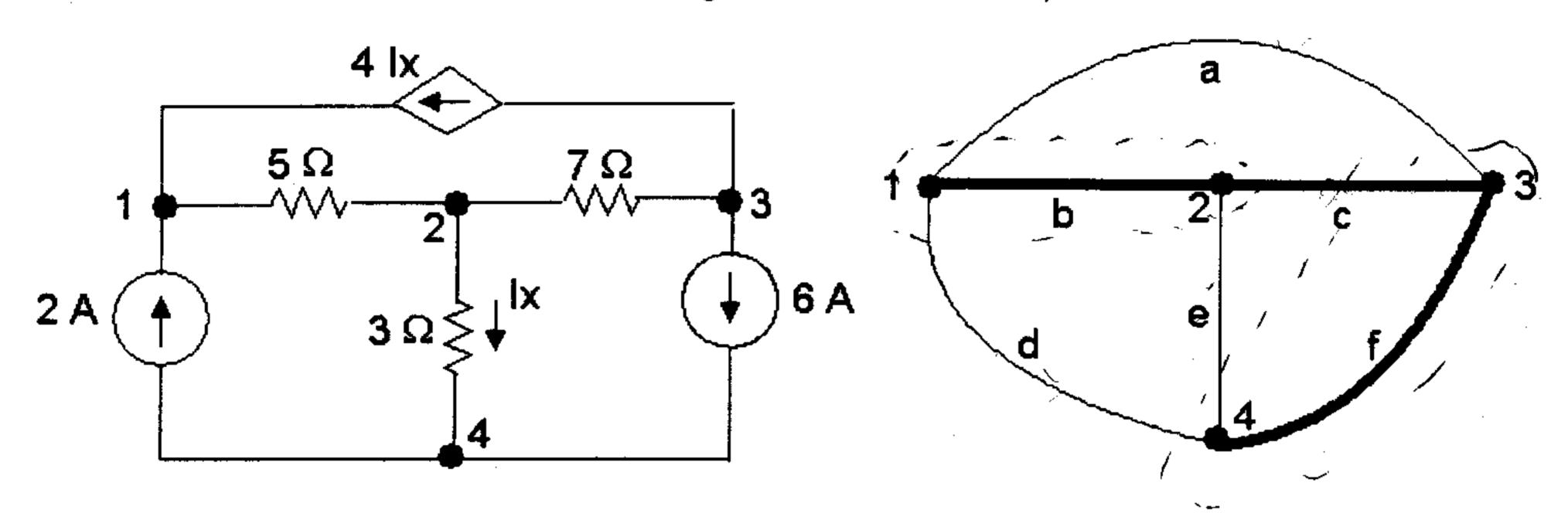

Given the electric circuit, graph, and tree (bolded edges) below, write the KCL equation associated with each fundamental cut set in terms of node voltages. Do not solve the equations.

Fundamental Cut Sets?

$$24 + 4(\frac{\sqrt{2-1}4}{3x}) + \frac{\sqrt{2-1}}{5x} = 0$$

$$GA + V_2 - V_4 - QA = 0$$