## UNIVERSITY OF CALIFORNIA, BERKELEY College of Engineering Dept. of Electrical Engineering and Computer Sciences

**EECS 40**

#### Fall 2003

## Homework #9 Solutions

#### **Problem 1: Inverter Circuits and Noise Margins**

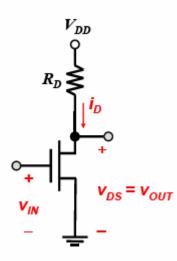

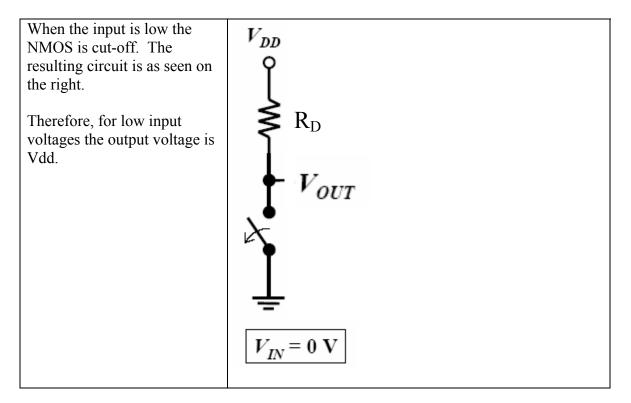

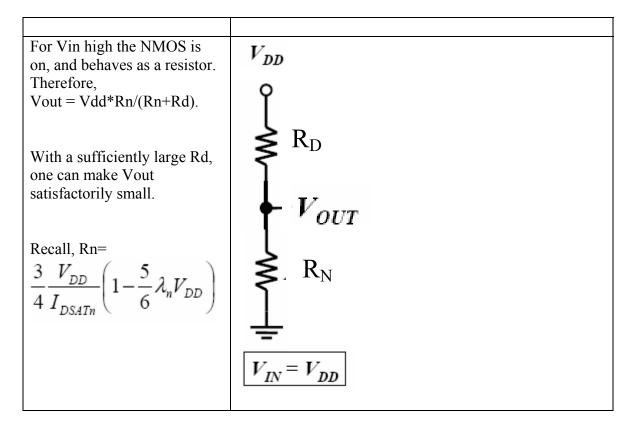

**a)** Describe qualitatively how an NMOS inverter circuit (below left) works. Explain how relatively large noise margins *NMH* and *NML* can be achieved. (Refer to Slide 6 of Lecture 26 for the definitions of *NMH* and *NML*).

Lowering  $V_{OL}$  will increase the noise margin. This allows for a greater swing ( $V_{OH}=Vdd$ ,  $V_{OL}=0$ ) which in turn increases the noise margins. For an NMOS inverter, one can do this by increasing Rd, increasing W, or replacing Rd with a PMOS.

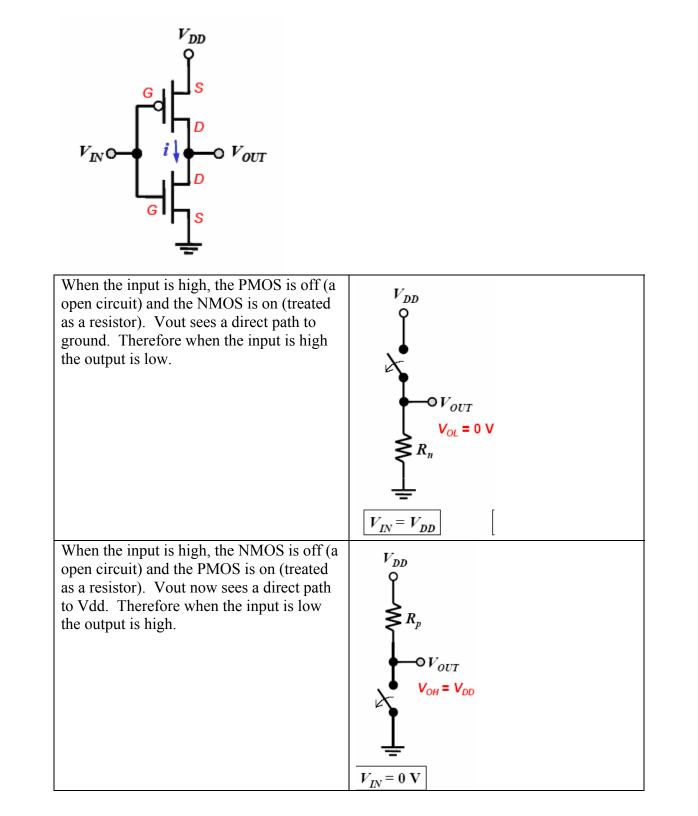

**b)** Describe qualitatively how a CMOS inverter (below right) works. What are its advantages (with respect to noise margins, power consumption, and size) as compared with the NMOS inverter?

The CMOS inverter has a larger output voltage swing than the NMOS inverter, which cannot pull the output voltage all the way to zero. This results in better noise margins. Also, the CMOS inverter takes up less space and uses less energy than the NMOS inverter. Resistors take up much more space on the IC than a PMOS, especially for large resistors. Also, with the CMOS inverter at least one of the two MOSFETs is in the cutoff region during steady-state; however, the NMOS inverter is in the triode mode when the input is high. Therefore the CMOS inverter uses practically no power while in steady-state, while the NMOS does.

# Problem 2: CMOS Logic Gates

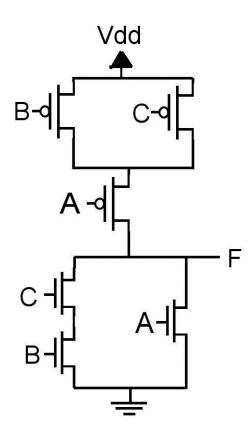

Design a complex CMOS logic gate to implement the function  $\mathbf{F} = (\mathbf{A} + \mathbf{B} \cdot \mathbf{C})$

Using DeMorgan's rule (to find pull up network):  $F = \overline{A} \cdot (\overline{B} \cdot \overline{C}) = \overline{A} \cdot (\overline{B} + \overline{C})$

## **Problem 3: Combinational Logic Circuits**

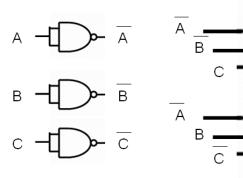

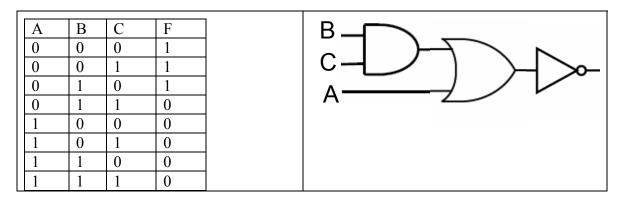

a) Write the truth table for the following Boolean expression:  $\mathbf{F} = \overline{(\mathbf{A} + \mathbf{B} \cdot \mathbf{C})}$ . Draw a logic circuit to realize this expression using AND, OR, and NOT gates.

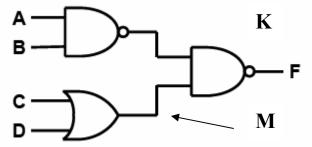

**b)** Consider the following logic circuit:

i) Write the Boolean expression for F.

$$\mathsf{F} = \overline{(\mathsf{A} \bullet \mathsf{B})} \bullet (\mathsf{C} + \mathsf{D}) = \overline{(\mathsf{A} \bullet \mathsf{B})} + \overline{(\mathsf{C} + \mathsf{D})} = \mathsf{A} \bullet \mathsf{B} + \overline{\mathsf{C}} \bullet \overline{\mathsf{D}}$$

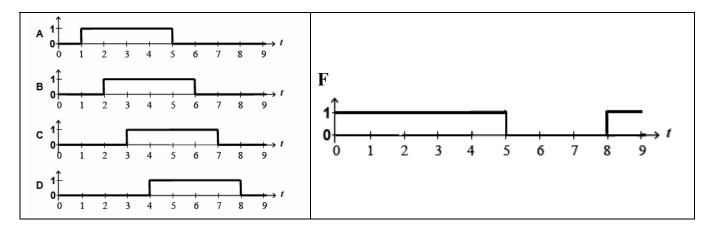

ii) Suppose the values of the four input variables **A B C D** as a function of time are as shown in

the timing diagram below. Draw **F** as a function of time.

## **Problem 4: Logic Circuit Synthesis**

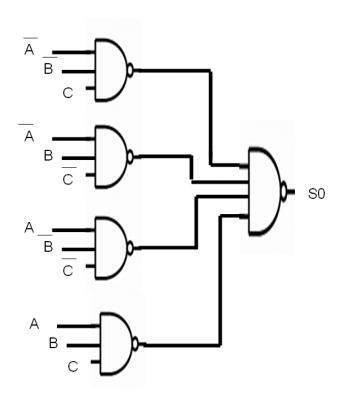

Consider the adder circuit whose truth table is given in Slide 8 of Lecture 29. a) Write a "sum-of-products" expression for the sum bit **S0**.

| Input |   |   | Output         |       |  |

|-------|---|---|----------------|-------|--|

| Α     | В | С | S <sub>1</sub> | $S_0$ |  |

| 0     | 0 | 0 | 0              | 0     |  |

| 0     | 0 | 1 | 0              | 1     |  |

| 0     | 1 | 0 | 0              | 1     |  |

| 0     | 1 | 1 | 1              | 0     |  |

| 1     | 0 | 0 | 0              | 1     |  |

| 1     | 0 | 1 | 1              | 0     |  |

| 1     | 1 | 0 | 1              | 0     |  |

| 1     | 1 | 1 | 1              | 1     |  |

$S0 = \overline{ABC} + \overline{ABC} + \overline{ABC} + \overline{ABC} + ABC$

**b)** Simplify this logical expression.

| S0 | BC |    |    |    |    |

|----|----|----|----|----|----|

|    |    | 00 | 01 | 11 | 10 |

| А  | 0  | 0  | 1  | 0  | 1  |

|    | 1  | 1  | 0  | 1  | 0  |

S0 cannot be simplified anymore using NAND and NORs, but it can be simplified using exclusive-or.

S0=(A < XOR > B < XOR > C)

c) Draw the logic circuit for S0 using only NAND gates.