```

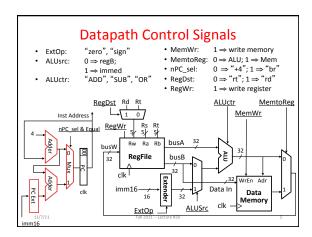

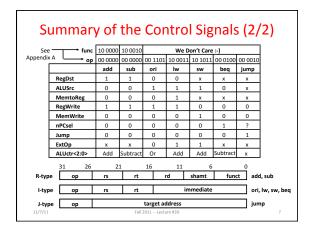

Summary of the Control Signals (1/2)

Register Transfer

inst

R[rd] ← R[rs] + R[rt]; PC ← PC + 4

add

ALUSrc=RegB, ALUctr="ADD", RegDst=rd, RegWr, nPC_sel="+4"

R[rd] \leftarrow R[rs] - R[rt]; PC \leftarrow PC + 4

ALUSTC=RegB, ALUCTT="SUB", RegDst=rd, RegWr, nPC_sel="+4"

R[rt] \leftarrow R[rs] + zero_ext(Imm16); PC \leftarrow PC + 4

ori

ALUSTC=Im, Extop="Z", ALUCT="OR", RegDst=rt, RegWr, nPC sel="+4"

1w

\texttt{R[rt]} \leftarrow \texttt{MEM[R[rs]} + \texttt{sign\_ext(Imm16)]}; \ \texttt{PC} \leftarrow \texttt{PC} + 4

ALUsrc=Im, Extop="sn", ALUctr="ADD", MemtoReg, RegDst=rt, RegWr, nPC_sel = "+4"

MEM[ R[rs] + sign_ext(Imm16)] ← R[rs]; PC ← PC + 4

ALUSTC=Im, Extop="sn", ALUCT = "ADD", MemWr, nPC_sel = "+4"

if (R[rs] == R[rt]) then PC \leftarrow PC + sign_ext(Imm16)] || 00 else PC \leftarrow PC + 4

nPC_sel = "br", ALUctr = "SUB"

Fall 2011 -- Lecture #30

```

#### Administrivia

- Due to time constraints we can only allow the use of a maximum of 2 slip days on Project

4.

- Thus, while we always encourage you to get your work done on time, if you still have 3 slip days left, you may want to consider using one prior to project 4

11/7/11

Fall 2011 -- Lecture #30

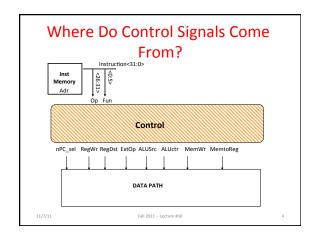

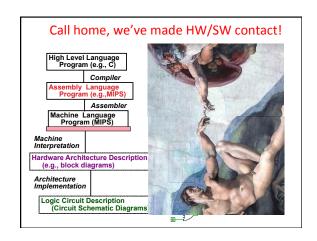

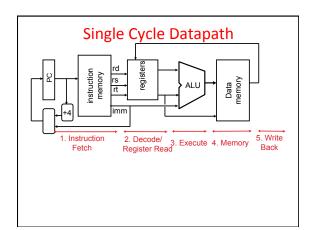

## Review: Single-cycle Processor

Processor

Control

Datapath

- Five steps to design a processor:

- Analyze instruction set → datapath requirements

- 2. Select set of datapath components & establish clock methodology

- 3. Assemble datapath meeting the requirements

- 4. Analyze implementation of each instruction to determine setting of control points that effects the register transfer.

- 5. Assemble the control logic

- · Formulate Logic Equations

- Design Circuits

11/7/11

Fall 2011 -- Lecture #30

### Single Cycle Performance

- Assume time for actions are

- 100ps for register read or write; 200ps for other events

- Clock rate is?

| Instr    | Instr fetch | Register read | ALU op | Memory access | Register<br>write | Total time |

|----------|-------------|---------------|--------|---------------|-------------------|------------|

| lw       | 200ps       | 100 ps        | 200ps  | 200ps         | 100 ps            | 800ps      |

| sw       | 200ps       | 100 ps        | 200ps  | 200ps         |                   | 700ps      |

| R-format | 200ps       | 100 ps        | 200ps  |               | 100 ps            | 600ps      |

| beq      | 200ps       | 100 ps        | 200ps  |               |                   | 500ps      |

- What can we do to improve clock rate?

- Will this improve performance as well?

Want increased clock rate to mean faster programs

**EA)/7/0111** -- Lecture #3

### Single Cycle Performance

- Assume time for actions are

- 100ps for register read or write; 200ps for other events

- Clock rate is?

| Instr    | Instr fetch | Register read | ALU op | Memory access | Register write | Total time |

|----------|-------------|---------------|--------|---------------|----------------|------------|

| lw       | 200ps       | 100 ps        | 200ps  | 200ps         | 100 ps         | 800ps      |

| sw       | 200ps       | 100 ps        | 200ps  | 200ps         |                | 700ps      |

| R-format | 200ps       | 100 ps        | 200ps  |               | 100 ps         | 600ps      |

| beq      | 200ps       | 100 ps        | 200ps  |               |                | 500ps      |

- · What can we do to improve clock rate?

- Will this improve performance as well?

Want increased clock rate to mean faster programs

-- Lecture #30

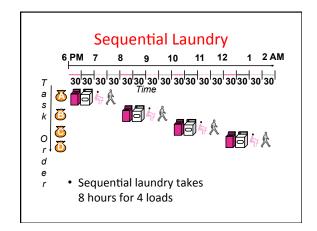

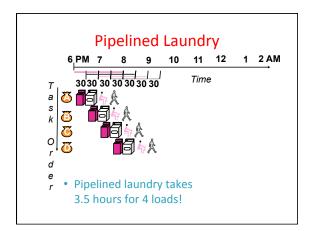

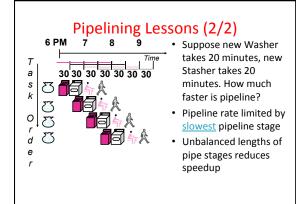

### **Gotta Do Laundry**

- Ann, Brian, Cathy, Dave each have one load of clothes to wash, dry, fold, and put away

- Washer takes 30 minutes

- Dryer takes 30 minutes

- "Folder" takes 30 minutes

- "Stasher" takes 30 minutes to put clothes into drawers

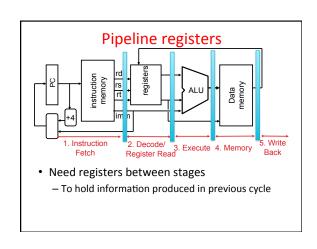

## Steps in Executing MIPS

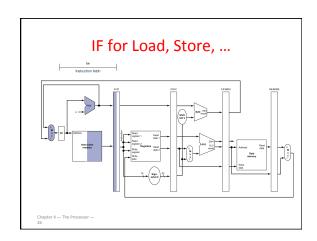

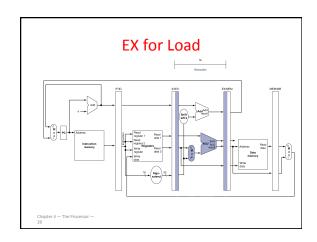

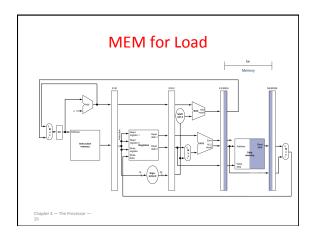

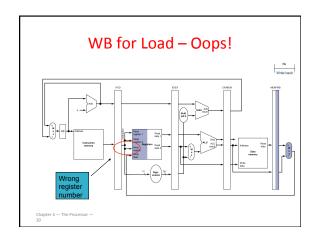

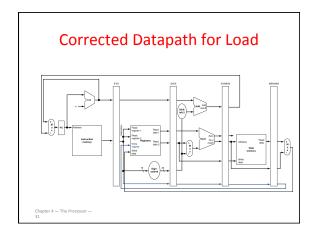

- 1) IFtch: Instruction Fetch, Increment PC

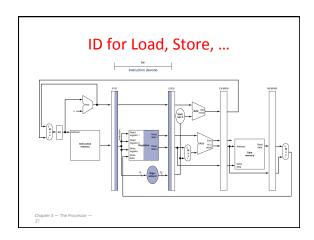

- 2) Dcd: Instruction Decode, Read Registers

- 3) Exec:

Mem-ref: Calculate Address Arith-log: Perform Operation

4) Mem:

Load: Read Data from Memory Store: Write Data to Memory

5) WB: Write Data Back to Register

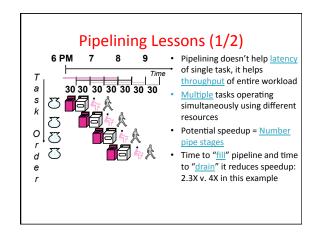

# So, in conclusion

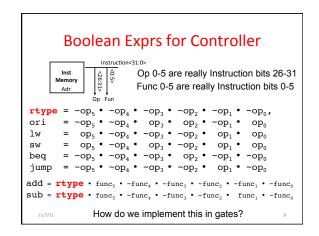

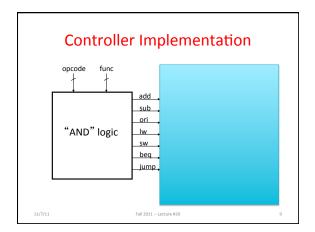

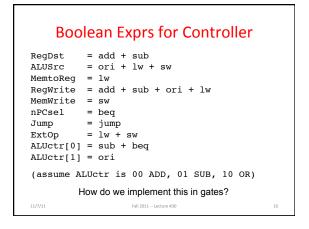

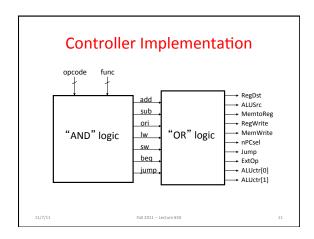

- You now know how to implement the control logic for the single-cycle CPU.

- (actually, you already knew it!)

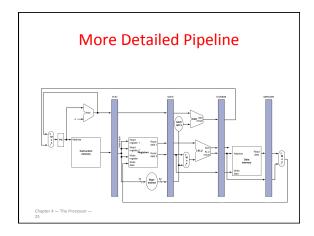

- Pipelining improves performance by increasing instruction throughput: exploits ILP

- Executes multiple instructions in parallel

- Each instruction has the same latency

- Next: hazards in pipelining:

- Structure, data, control

E4V20111 -- Lecture #30

32