tional Logic Circuits (2)

Garcia, Fall 2011 © UCB

| TT Example #1: 1                                 | iff or       | ne (not both | ı) a,b=1               |

|--------------------------------------------------|--------------|--------------|------------------------|

| а                                                | b            | У            |                        |

| 0                                                | 0            | 0            |                        |

| 0                                                | 1            | 1            |                        |

| 1                                                | 0<br>1       | 1            |                        |

| 1                                                | 1            | 0            |                        |

| CSSIC L25 Representations of Combinational Logic | Circuits (4) | 1            | Garcia, Fall 2011 © UC |

| TT Example #3: 32-bit unsigned adder |                                |                         |  |  |

|--------------------------------------|--------------------------------|-------------------------|--|--|

| Α                                    | В                              | C                       |  |  |

| 000 0                                | 000 0                          | 000 00                  |  |  |

| 000 0                                | 000 1                          | 000 01                  |  |  |

| •                                    | •                              | · How                   |  |  |

| •                                    | •                              | . Many<br>Bows?         |  |  |

| •                                    | •                              |                         |  |  |

| 111 1                                | 111 1                          | 111 10                  |  |  |

| CS61C L25 Representations of Con     | abinational Logic Circuits (6) | Garcia, Fall 2011 © UCB |  |  |

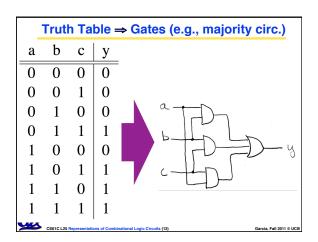

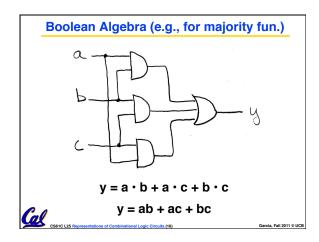

| TT Example                      | #4:           | 3-in          | put | majority circuit        |

|---------------------------------|---------------|---------------|-----|-------------------------|

|                                 | a             | b             | c   | У                       |

|                                 | 0             | 0             | 0   | 0                       |

|                                 | 0             | 0             | 1   | 0                       |

|                                 | 0             | 1             | 0   | 0                       |

|                                 | 0             | 1             | 1   | 1                       |

|                                 | 1             | 0             |     | 0                       |

|                                 | 1             | 0             | 1   | 1                       |

|                                 | 1             | 1             | 0   | 1                       |

| Cal                             | 1             | 1             | 1   | 1                       |

| CS61C L25 Representations of Co | mbinational l | ogic Circuits | (7) | Garcia, Fall 2011 © UCI |

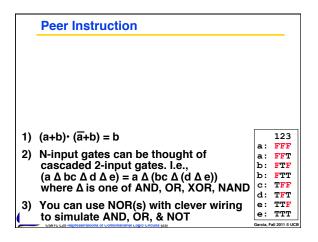

| 2-input gates extend to n-inputs                                                          |   |   |   |                        |

|-------------------------------------------------------------------------------------------|---|---|---|------------------------|

| N-input XOR is the                                                                        | а | b | с | У                      |

| <ul> <li>N-input XOR is the<br/>only one which isn't<br/>so obvious</li> </ul>            | 0 | 0 | 0 | 0                      |

| <ul> <li>It's simple: XOR is a<br/>1 iff the # of 1s at its<br/>input is odd ⇒</li> </ul> | 0 | 0 | 1 | 1                      |

|                                                                                           | 0 | 1 | 0 | 1                      |

|                                                                                           | 0 | 1 | 1 | 0                      |

|                                                                                           | 1 | 0 | 0 | 1                      |

|                                                                                           | 1 | 0 | 1 | 0                      |

|                                                                                           | 1 | 1 | 0 | 0                      |

| Cal                                                                                       | 1 | 1 | 1 | 1                      |

| CS61C L25 Representations of Combinational Logic Circuits (11)                            |   |   |   | Garcia, Fall 2011 © UC |

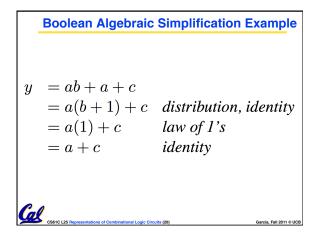

| Laws of Bo                   | oolean Algebra                                                                                                                                                                                          |                                                                                                                                                                                      |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ( 0 )                        | $\begin{array}{c} x+\overline{x}=1\\ x+1=1\\ x+0=x\\ x+x=x\\ (x+y)+z=x+(y+z)\\ x+yz=(x+y)(x+z)\\ (x+y)x=x\\ (x+y)x=x\\ (\overline{x}+y)x=xy\\ \overline{x+y}=\overline{x}\cdot\overline{y} \end{array}$ | complementarity<br>laws of 0's and 1's<br>identities<br>idempotent law<br>commutativity<br>associativity<br>distribution<br>uniting theorem<br>uniting theorem v.2<br>DeMorgan's Law |

| GS61C L25 Representations of | Combinational Looic Circuits (19)                                                                                                                                                                       | Garcia. Fall 2011 © UC                                                                                                                                                               |