## CS 150 Lab 4 Prelab Spring 2013

Read section 2 of the lab document and complete these questions before attending your lab section.

## 1 Synchronous vs. Asynchronous Read

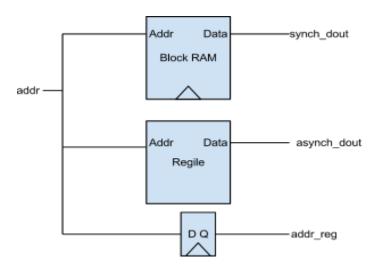

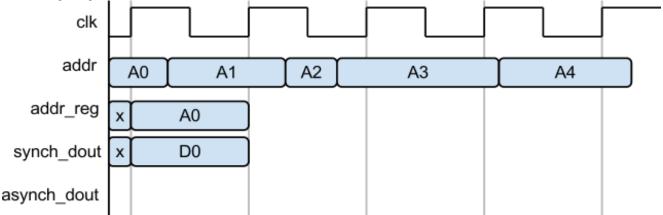

The Block RAMs that you will use in this lab (and throughout the project) are synchronous read and synchronous write. On the other hand, the register file you will build in the project has an asynchronous read and synchronous write. Consider the hypothetical datapath above, where both the register file and the block ram have the same contents and receive the same address. Complete the timing diagram below:

Imagine you need to implement logic that depends on the data and the address it was loaded from. Which address would you use with synch dout? Which with asynch dout?

## 2 Example List

The skeleton files include a memory initialization vector representing a linked list to use while debugging your processor. The contents of the file are reproduced below (in hexadecimal). What list does this represent, and what is the sum of the elements in the list? In the lab, you will need to use this information to debug and verify your list processor.

## Control Signals

Section 2 of the lab document shows one possible way to store the list  $\{1,2,3\}$  in memory. Fill in the table of control signals and expected data signals to sum this list using the datapath given in section 2.3 of the lab document. Write 'x' when you don't care about the signal and use as few cycles as possible to sum the list.

|   | rst | addr_sel | wr_en | alu_op | Block RAM dout | accum_result |

|---|-----|----------|-------|--------|----------------|--------------|

| 0 | 1   | Х        | X     | Х      | Х              | 0x0000000    |

| 1 | 0   |          |       |        | 0x00000001     |              |

| 2 |     |          |       |        |                |              |

| 3 |     |          |       |        |                |              |

| 4 |     |          |       |        |                |              |

| 5 |     |          |       |        |                |              |

| 6 |     |          |       |        |                |              |

| 7 |     |          |       |        |                |              |