# <u>EECS150 - Digital Design</u> <u>Lecture 25 - Latches & Flip-flops</u>

## April 23, 2012 John Wawrzynek

Spring 2013

EECS150 - Lec25-flipflops

Page 1

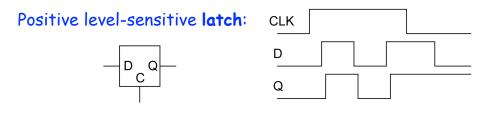

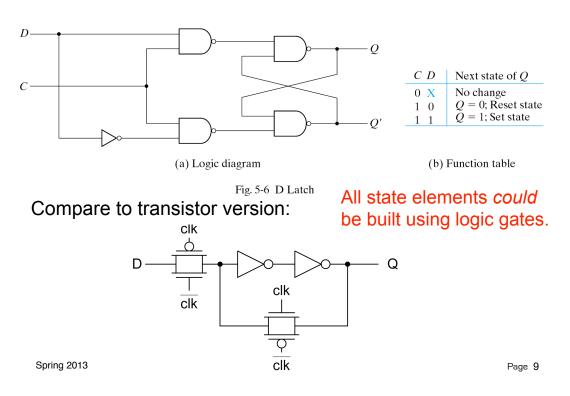

## **CMOS "Transparent" Latches**

#### Latch Implementation:

EECS150 - Lec25-flipflops

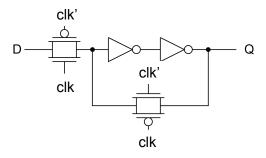

### **Designing with Latches**

Spring 2013

EECS150 - Lec25-flipflops

Page 3

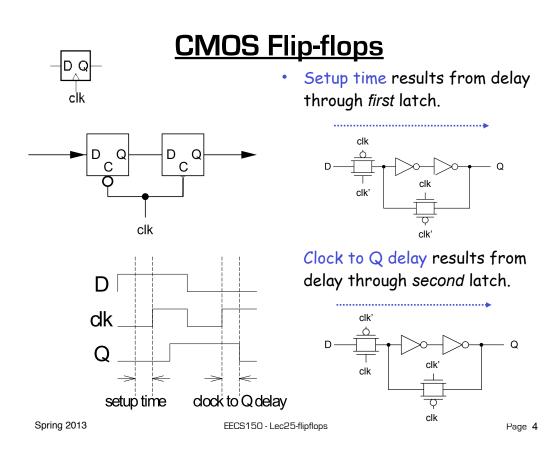

## **Cross-coupled NOR gates**

remember. 00 01

NOR

1

0

0 11 | 0

10

If both R=0 & S=0, then cross-couped NORs ٠ equivalent to a stable latch:

If either R or S becomes =1 then state may change: 0 R

What happens if R or S or both become = 1?

Spring 2013

EECS150 - Lec25-flipflops

Page 5

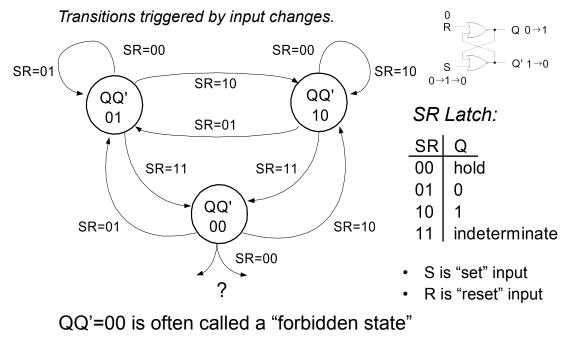

## Asynchronous State Transition Diagram

Spring 2013

EECS150 - Lec25-flipflops

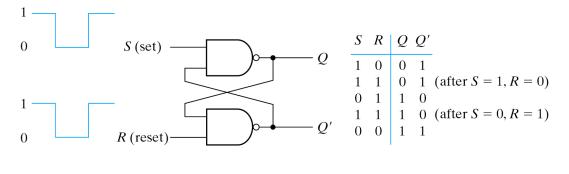

#### Nand-gate based SR latch

(a) Logic diagram (b) Function table

Fig. 5-4 SR Latch with NAND Gates

• Same behavior as cross-coupled NORs with inverted inputs.

Spring 2013

EECS150 - Lec25-flipflops

Page 7

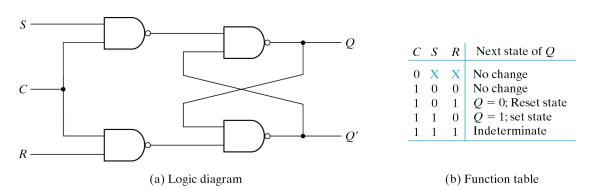

### Level-sensitive SR Latch

Fig. 5-5 SR Latch with Control Input

- The input "C" works as an "enable" signal, latch only changes output when C is high.

- Usually connected to **clock**.

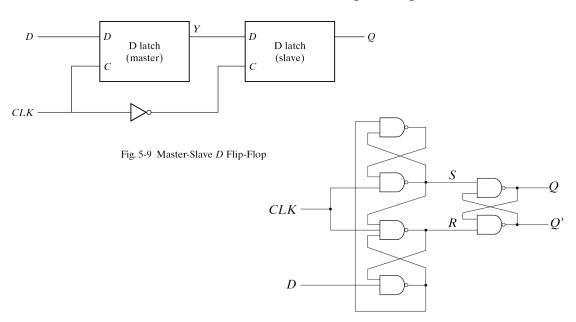

#### <u>D-latch</u>

## **2** Alternative Flip-flops

Fig. 5-10 D-Type Positive-Edge-Triggered Flip-Flop

EECS150 - Lec25-flipflops

## <u>J-K FF</u>

- Add logic to eliminate "indeterminate" action of RS FF.

- New action is "toggle"

- J = "jam"

Spring 2013

EECS150 - Lec25-flipflops

Page 11

# **Storage Element Taxonomy**

| synchronous<br>level-sensitive edge-triggered |         |              | asynchronous |

|-----------------------------------------------|---------|--------------|--------------|

| D-type                                        | *       | $\checkmark$ | n.a.         |

| JK-type<br>RS-type                            | √<br>√  | ✓<br>✓       | n.a.<br>★    |

|                                               | "latch" | "flip-flop"  | "latch"      |

★"natural" form

✓ "possible" form

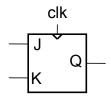

## **Design Example with RS FF**

- With D-type FF state elements, new state is computed based on inputs & present state bits - reloaded each cycle.

- With RS (or JK) FF state elements, inputs are used to determine conditions under which to set or reset state bits.

- Example: bit-serial adder (LSB first)

Spring 2013

EECS150 - Lec25-flipflops

Page 13

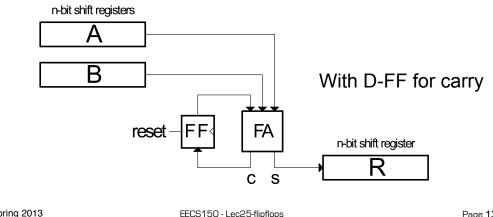

# **Bit-serial adder with RS FF**

• RS FF stores the carry: a b  $c_{i||} c_{i+1}$ S 0 000 0 Carry kill a'b' 001 0 1 010 1 0 а 1 011 0 100 0 1 b 1 101 0 110 1 0 Carry generate 1 111 1 S ab Q R