# EECS150 - Digital Design

# Lecture 19 - Finite State Machines Revisited

# April 2, 2013 John Wawrzynek

Spring 2013 EECS150 - Lec19-fsm Page 1

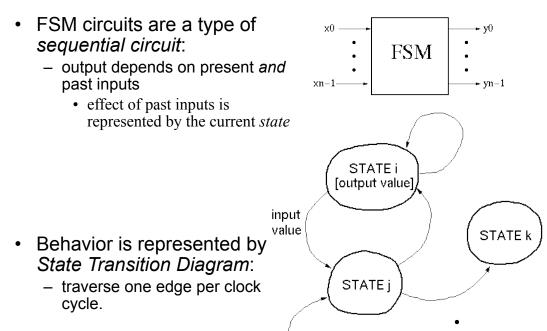

# Finite State Machines (FSMs)

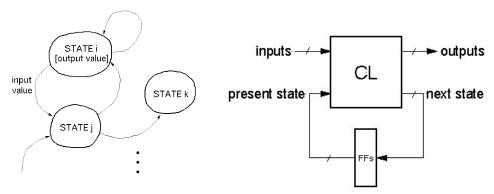

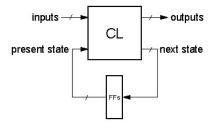

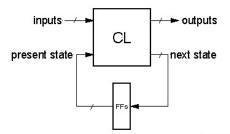

#### **FSM Implementation**

- Flip-flops form state register

- number of states ≤ 2<sup>number of flip-flops</sup>

- CL (combinational logic) calculates next state and output

- Remember: The FSM follows exactly one edge per cycle.

So far we have learned how to implement in Verilog. Now we learn how to design "by hand" to the gate level.

Spring 2013 EECS150 - Lec19-FSM Page 3

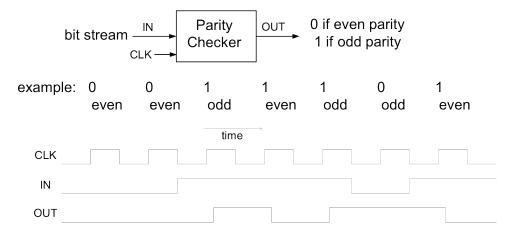

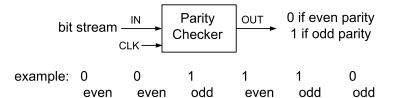

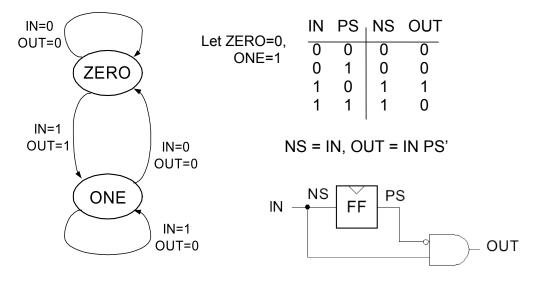

## Parity Checker Example

A string of bits has "even parity" if the number of 1's in the string is even.

Design a circuit that accepts a bit-serial stream of bits and outputs a 0 if the parity thus far is even and outputs a 1 if odd:

Next we take this example through the "formal design process". But first, can you guess a circuit that performs this function?

#### Formal Design Process

time

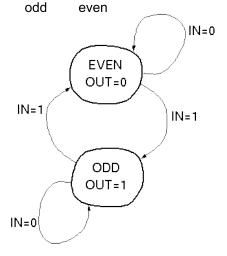

#### "State Transition Diagram"

- circuit is in one of two "states".

- transition on each cycle with each new input, over exactly one arc (edge).

- Output depends on which state the circuit is in.

Page 5 Spring 2013 EECS150 - Lec19-FSM

## Formal Design Process

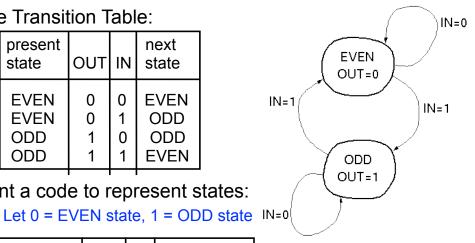

#### State Transition Table:

| present<br>state | OUT | IN      | next<br>state |

|------------------|-----|---------|---------------|

| EVEN             | 0   | 0 1 0 1 | EVEN          |

| EVEN             | 0   |         | ODD           |

| ODD              | 1   |         | ODD           |

| ODD              | 1   |         | EVEN          |

Invent a code to represent states:

next state (ns) present state (ps) OUT IN 0 0 0 0 1 1 1 1 0 1 1 1 1 0

Derive logic equations from table (how?):

> OUT = PS NS = PS xor IN

#### Formal Design Process

#### Logic equations from table:

OUT = PS NS = PS xor IN

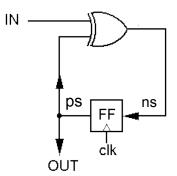

- Circuit Diagram:

- XOR gate for NS calculation

- DFF to hold present state

- no logic needed for output in this example.

Spring 2013 EECS150 - Lec19-FSM Page 7

## Formal Design Process

#### Review of Design Steps:

- 1. Specify circuit function (English)

- 2. Draw state transition diagram

- 3. Write down symbolic state transition table

- 4. Write down encoded state transition table

- 5. Derive logic equations

- 6. Derive circuit diagram

Register to hold state Combinational Logic for Next State and Outputs

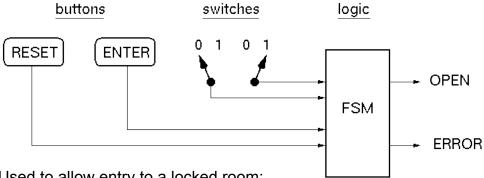

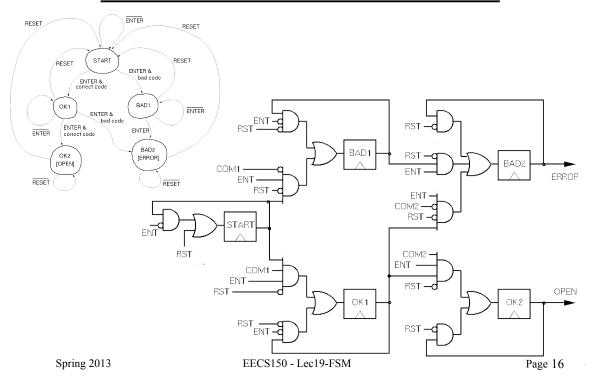

#### **Combination Lock Example**

- Used to allow entry to a locked room:

- 2-bit serial combination. Example 01,11:

- 1. Set switches to 01, press ENTER

- 2. Set switches to 11, press ENTER

- 3. OPEN is asserted (OPEN=1).

If wrong code, ERROR is asserted (after second combo word entry). Press Reset at anytime to try again.

Spring 2013 EECS150 - Lec19-FSM Page 9

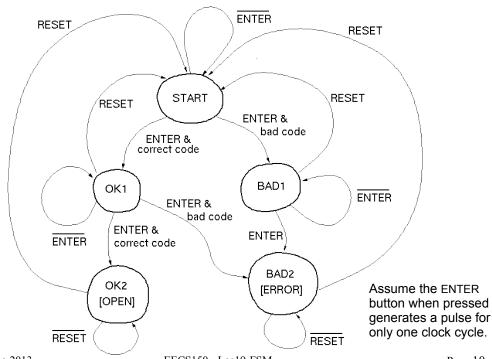

## **Combinational Lock STD**

#### **Symbolic State Transition Table**

| RESET | ENTER | COM1 | COM2 | Preset State | Next State | OPEN | ERROR |

|-------|-------|------|------|--------------|------------|------|-------|

| 0     | 0     | *    | *    | START        | START      | 0    | 0     |

| 0     | 1     | 0    | *    | START        | BAD1       | 0    | 0     |

| 0     | 1     | 1    | *    | START        | OK1        | 0    | 0     |

| 0     | 0     | *    | *    | OK1          | OK1        | 0    | 0     |

| 0     | 1     | *    | 0    | OK1          | BAD2       | 0    | 0     |

| 0     | 1     | *    | 1    | OK1          | OK2        | 0    | 0     |

| 0     | *     | *    | *    | OK2          | OK2        | 1    | 0     |

| 0     | 0     | *    | *    | BAD1         | BAD1       | 0    | 0     |

| 0     | 1     | *    | *    | BAD1         | BAD2       | 0    | 0     |

| 0     | *     | *    | *    | BAD2         | BAD2       | 0    | 1     |

| 1     | *     | *    | *    | *            | START      | 0    | 0     |

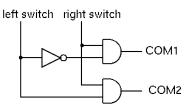

Decoder logic for checking combination (01,11):

Spring 2013 EECS150 - Lec19-FSM Page 11

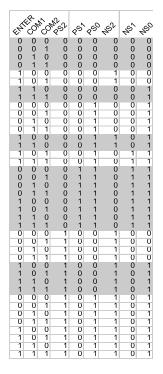

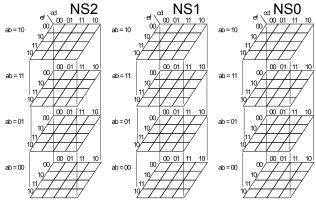

#### **Encoded ST Table**

- · Assign states:

- START=000, OK1=001, OK2=011 BAD1=100, BAD2=101

- Omit reset. Assume that primitive flip-flops has reset input.

- Rows not shown have don't cares in output.

Correspond to invalid PS values.

What are the output functions for OPEN and ERROR?

#### **State Encoding**

In general:

# of possible FSM state = 2<sup># of Flip-flops</sup> Example:

state1 = 01, state2 = 11, state3 = 10, state4 = 00

- However, often more than log<sub>2</sub>(# of states) FFs are used, to simplify logic at the cost of more FFs.

- Extreme example is one-hot state encoding.

Spring 2013 EECS150 - Lec19-FSM Page 13

#### State Encoding

- One-hot encoding of states.

Ex: 3 States.

- One FF per state.

STATE1: 001 STATE2: 010 STATE3: 100

- · Why one-hot encoding?

- Simple design procedure.

- Circuit matches state transition diagram (example next page).

- Often can lead to simpler and faster "next state" and output logic.

- Why not do this?

- Can be costly in terms of Flip-flops for FSMs with large number of states.

- FPGAs are "Flip-flop rich", therefore one-hot state machine encoding is often a good approach.

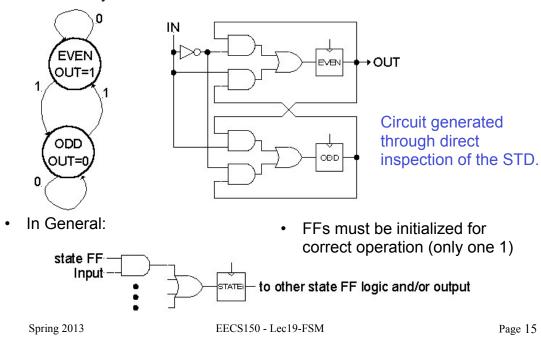

#### One-hot encoded FSM

• Even Parity Checker Circuit:

## One-hot encoded combination lock

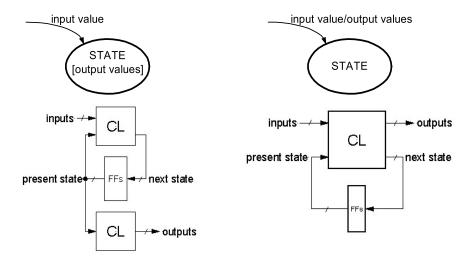

#### **FSM Implementation Notes**

· General FSM form:

- All examples so far generate output based only on the present state:

- Commonly name Moore Machine

(If output functions include both present state and input then called a Mealy Machine)

present state

CL

FFs next state

CL

outputs

Spring 2013 EECS150 - Lec19-FSM Page 17

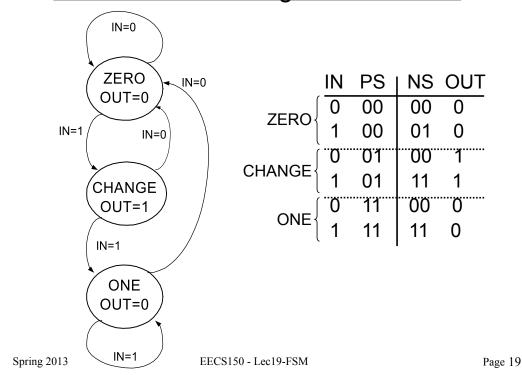

#### **Finite State Machines**

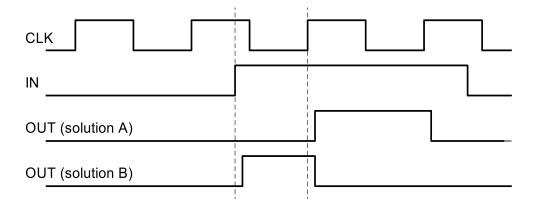

Example: Edge Detector

Bit are received one at a time (one per cycle),

such as:  $000111010 \longrightarrow time$

Design a circuit that asserts its output for one cycle when the input bit stream changes from 0 to 1.

Try two different solutions.

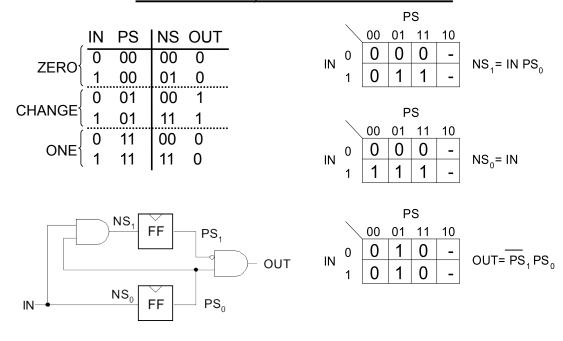

# State Transition Diagram Solution A

#### Solution A, circuit derivation

#### Solution B

Output depends not only on PS but also on input, IN

What's the *intuition* about this solution?

Spring 2013 EECS150 - Lec19-FSM Page 21

# Edge detector timing diagrams

- Solution A: output follows the clock

- Solution B: output changes with input rising edge and is asynchronous wrt the clock.

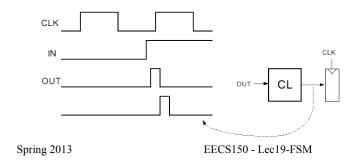

#### **FSM Comparison**

#### Solution A

#### **Moore Machine**

- output function only of PS

- maybe <u>more</u> states (why?)

- synchronous outputs

- no glitches

- one cycle "delay"

- full cycle of stable output

#### Solution B

#### **Mealy Machine**

- output function of both PS & input

- maybe fewer states

- · asynchronous outputs

- if input glitches, so does output

- output immediately available

- output may not be stable long enough to be useful (below):

If output of Mealy FSM goes through combinational logic before being registered, the CL might delay the signal and it could be missed by the clock edge.

Page 23

## **FSM Recap**

#### **Moore Machine**

#### **Mealy Machine**

Both machine types allow one-hot implementations.

#### Final Notes on Moore versus Mealy

- 1. A given state machine *could* have *both* Moore and Mealy style outputs. Nothing wrong with this, but you need to be aware of the timing differences between the two types.

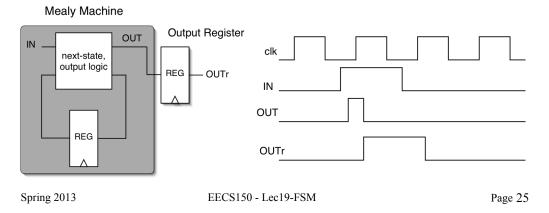

- 2. The output timing behavior of the Moore machine can be achieved in a Mealy machine by "registering" the Mealy output values:

## General FSM Design Process with Verilog

Design Steps: <u>Implementation</u>

- 1. Specify circuit function (English)

- 2. Draw state transition diagram

- 3. Write down symbolic state transition table

- 4. Assign encodings (bit patterns) to symbolic states

- 5. Code as Verilog behavioral description

- ✓ Use parameters to represent encoded states.

- ✓ Use separate always blocks for register assignment and CL logic block.

- ✓ Use case for CL block. Within each case section assign all outputs and next state value based on inputs. Note: For Moore style machine make outputs dependent only on state not dependent on inputs.

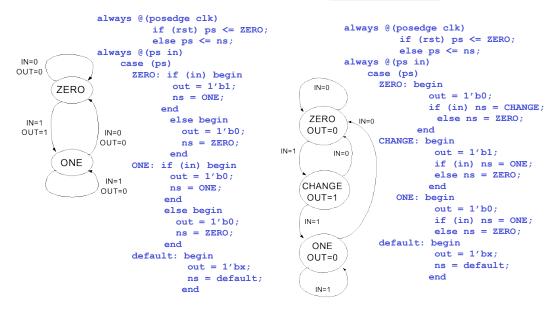

# FSMs in Verilog

#### Mealy Machine

#### **Moore Machine**