| <u>EECS150 - Digital Design</u><br><u>Lecture 5 - Verilog Logic Synthesis</u> |                               |        |  |

|-------------------------------------------------------------------------------|-------------------------------|--------|--|

|                                                                               | Feb 4, 2013<br>John Wawrzynek |        |  |

| Spring 2013                                                                   | EECS150 - LecO5-verilog_synth | Page 1 |  |

### **Parameterized Version**

Parameters give us a way to generalize our designs. A module becomes a "generator" for different variations. Enables design/module reuse. Can simplify testing.

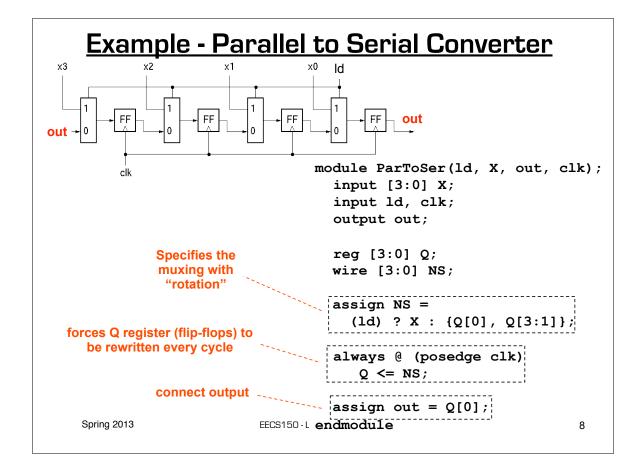

|                                         | <pre>module ParToSer(ld, X, out, CLK);</pre>                   |

|-----------------------------------------|----------------------------------------------------------------|

| parameter N                             | = 4; input [N-1:0] X;                                          |

| Declare a parame<br>default valu        |                                                                |

| Note: this is not<br>Acts like a "syn   | ta port. reg out; of "3" with "N-1".<br>thesis- reg [N-1:0] Q; |

| time" consta                            | ant. wire $[N-1:0]$ NS;                                        |

| ParToSer #(.N(8))<br>ps8 ( );           | assign NS =<br>(ld) ? X : {Q[0], Q[ <mark>N-1</mark> :1]};     |

| ParToSer #(.N(64))<br>ps64 ( );         | always @ (posedge clk)<br>Q <= NS;                             |

| Overwrite parameter N at instantiation. | assign out = $Q[0];$                                           |

| Spring 2013                             | EECS150-L endmodule                                            |

|                                         |                                                                |

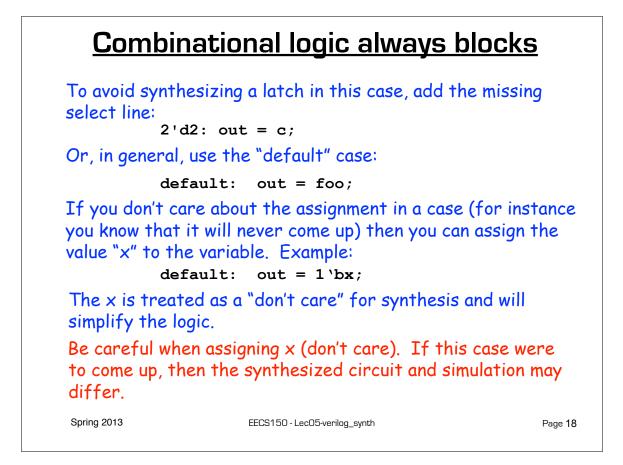

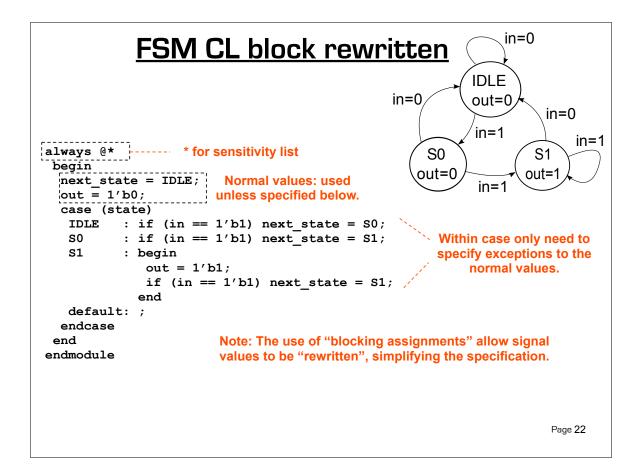

## **Combinational logic always blocks**

Make sure all signals assigned in a combinational always block are explicitly assigned values every time that the always block executes. Otherwise latches will be generated to hold the last value for the signals not assigned values

| Sel case value 2'd2 omitted.<br>Out is not updated when select<br>line has 2'd2. | <pre>module mux4to1 (out, a, b, c, d, sel);<br/>output out;<br/>input a, b, c, d;<br/>input [1:0] sel;<br/>reg out;<br/>always @(sel or a or b or c or d)</pre> |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Latch is added by tool to hold<br>the last value of out under this<br>condition. | <pre>begin case (sel)     2'd0: out = a;     2'd1: out = b;     2'd3: out = d; endcase</pre>                                                                    |

| Similar problem with if-else statements.                                         | endmodule                                                                                                                                                       |

| Spring 2013 EEC                                                                  | S150 - Lec05-verilog_synth Page 17                                                                                                                              |

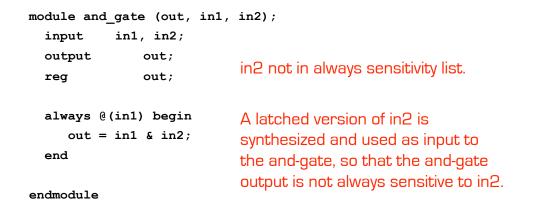

#### **Incomplete Triggers**

Leaving out an input trigger usually results in latch generation for the missing trigger.

Easy way to avoid incomplete triggers for combinational logic is with: always @\*

Spring 2013

EECS150 - LecO5-verilog\_synth

Page 19

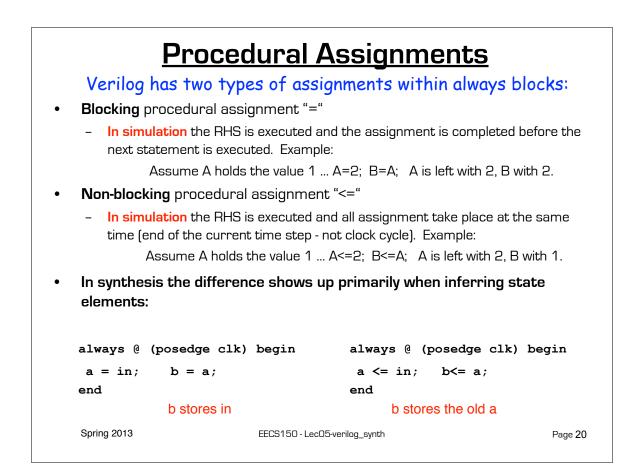

# Procedural Assignments

The sequential semantics of the blocking assignment allows variables to be multiply assigned within a single always block. Unexpected behavior can result from mixing these assignments in a single block. Standard rules:

- Use blocking assignments to model combinational logic within an always block ( "=").

- ii. Use non-blocking assignments to implement sequential logic ("<=").</li>

- iii. Do not mix blocking and non-blocking assignments in the same always block.

- iv. Do not make assignments to the same variable from more than one always block.

Spring 2013

EECS150 - LecO5-verilog\_synth

Page **21**

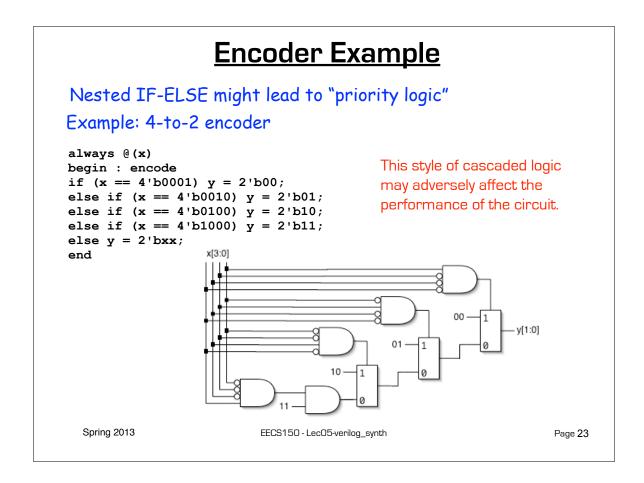

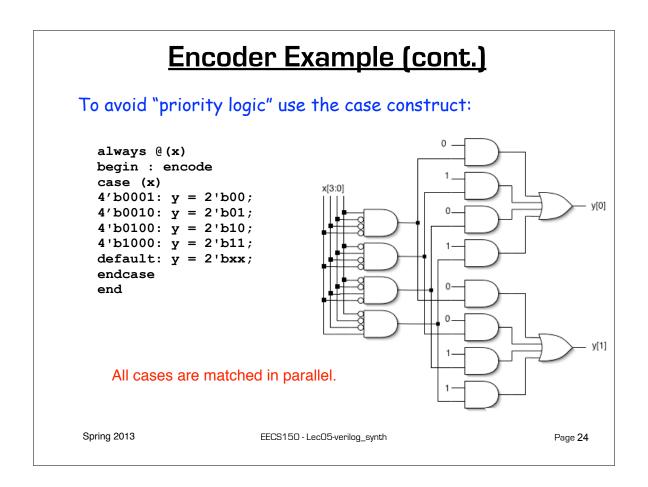

## Final thoughts on Verilog Examples

Verilog may look like C, but it describes hardware! (Except in simulation "test-benches" - which actually behave like programs.)

Multiple physical elements with parallel activities and temporal relationships.

A large part of digital design is knowing how to write Verilog that gets you the desired circuit. <u>First understand the circuit you</u> <u>want then figure out how to code it in Verilog</u>. If you do one of these activities without the other, you will struggle. These two activities will merge at some point for you.

Be suspicious of the synthesis tools! Check the output of the tools to make sure you get what you want.

Spring 2013

EECS150 - LecO5-verilog\_synth

Page 27