# EECS150 - Digital Design <u>Lecture 4 – Register & Flip-flops</u>

January 31, 2013

John Wawrzynek Electrical Engineering and Computer Sciences University of California, Berkeley

Spring 2013 EECS150 lec04-seq\_logic Page 1

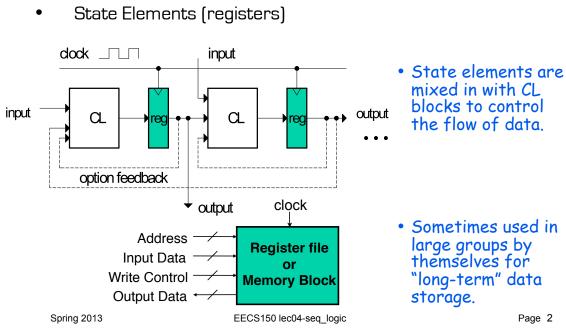

### Only Two Types of Circuits Exist

Combinational Logic Blocks (CL)

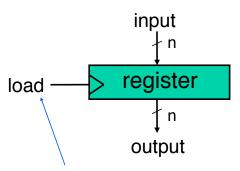

#### State Elements: circuits that store info

- Examples: registers, memories

- Register: Under the control of the "load" signal, the register captures the input value and stores it indefinitely.

often replace by clock signal (clk)

- The value stored by the register appears on the output (after a small delay).

- · Until the next load, changes on the data input are ignored (unlike CL, where input changes change output).

- These get used for short term storage (ex: register file), and to help move data around the processor.

Spring 2013

EECS150 lec04-seq\_logic

Page 3

## Register Details...What's inside?

Register cux =

$$\frac{dn-1}{p}$$

$\frac{dn-2}{p}$   $\frac{dn}{q}$   $\frac$

- n instances of a "Flip-Flop"

- Flip-flop name because the output flips and flops between and 0.1

- D is "data", Q is "output"

- Also called "d-type Flip-Flop"

EECS150 lec04-seq\_logic Page 4

Spring 2013

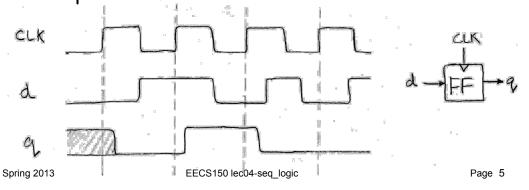

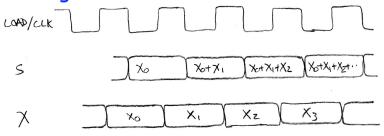

## **Flip-flop Timing**

- · Edge-triggered d-type flip-flop

- This one is "positive edge-triggered"

- "On the rising edge of the clock, the input d is sampled and transferred to the output. At all other times, the input d is ignored."

- · Example waveforms:

### **Uses for State Elements**

- 1) As a place to store values for some indeterminate amount of time:

- Register files (like \$1-\$31 on the MIPS)

- Memory (caches, and main memory)

- 2) Help control the flow of information between combinational logic blocks.

- State elements are used to hold up the movement of information at the inputs to combinational logic blocks and allow for orderly passage.

Spring 2013

EECS150 lec04-seq\_logic

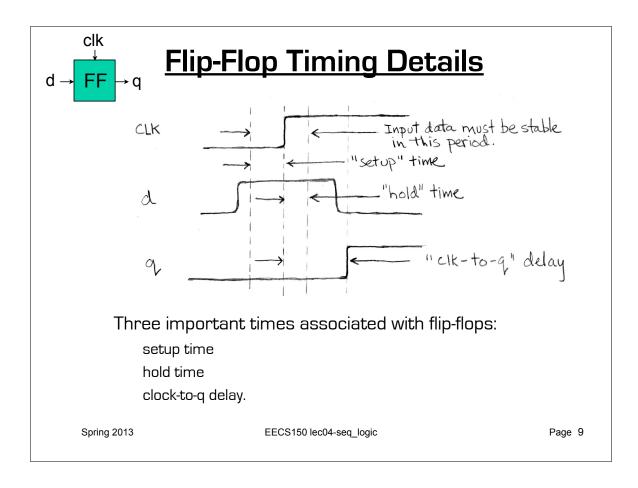

## **Accumulator Circuit Example**

Assume X is a vector of N integers, presented to the input of our accumulator circuit one at a time (one per clock cycle), so that after N clock cycles, S hold the sum of all N numbers.

S=0; Repeat N times

$$S = S + X$$

:

- We need something like this:

- But not quite.

Need to use the clock signal to hold up the feedback to match up with the input signal.

Spring 2013 EECS150 lec04-seq\_logic Page 7

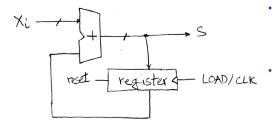

### **Accumulator Circuit**

- Put register, with clock signal controlling its load, in feedback path.

- On each clock cycle the register prevents the new value from reaching the input to the adder prematurely. (The new value just waits at the input of the register).

#### Timing:

Spring 2013

EECS150 lec04-seq\_logic

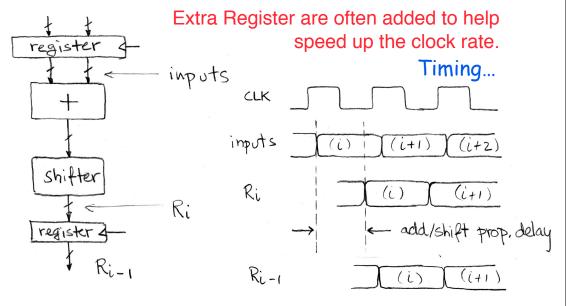

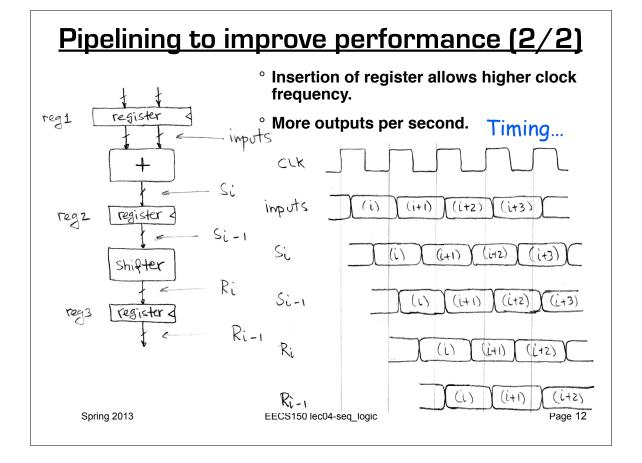

## Pipelining to improve performance (1/2)

Note: delay of 1 clock cycle from input to output.

Clock period limited by propagation delay of adder/shifter.

Spring 2013 EECS150 lec04-seq\_logic Page 11

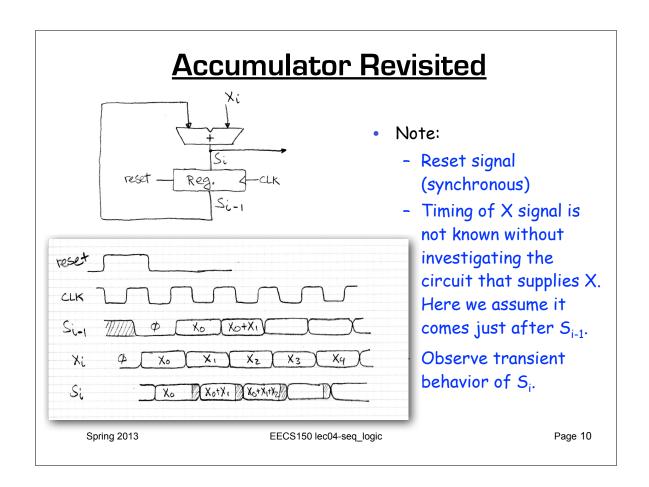

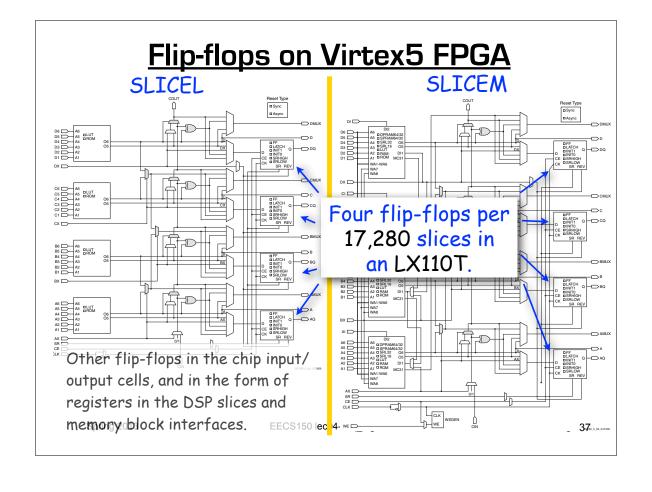

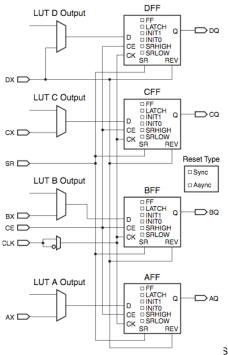

### Virtex5 Slice Flip-flops

4 flip-flops / slice (corresponding to the 4 6-LUTs)

Each takes input from LUT output or primary slice input.

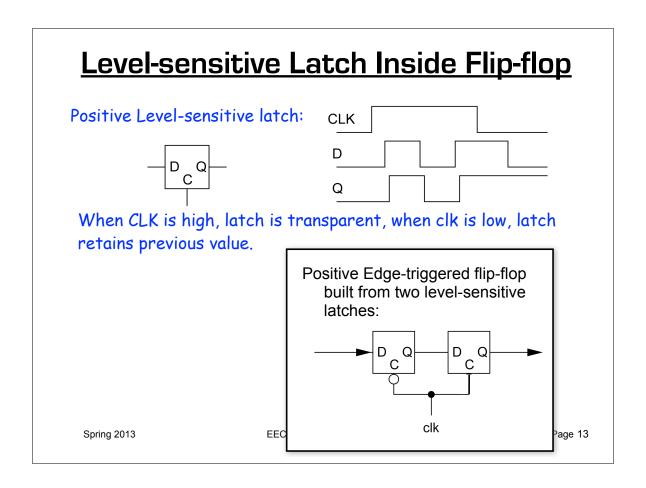

Edge-triggered FF vs. level-sensitive latch. Clock-enable input (can be set to 1 to disable) (shared).

Positive versus negative clock-edge.

Synchronous vs. asynchronous reset.

SRHIGH/SRLOW select reset (SR) set.

REV forces opposite state.

INITO/INIT1 used for global reset (not shown - usually just after power-on and configuration).

UG190\_5\_05\_071207 S150 lec04-seq\_logic

Page 15

## Virtex5 Flip-flops "Primitives"

D Flip-Flop with Synchronous Reset and Set and Clock Enable

Provided by the CAD tools. This maps to single slice flip-flop.

#### Logic Table

Negative-Clock Edge, Synchronous Reset and Set, and Clock Enable

Negative-Edge Clock, Clock Enable, and Asynchronous Preset and Clear

Clock Enable and Asynchronous Preset and Clear

Spring 2013

EECS150 lec04-seq\_logic

### State Elements in Verilog

Always blocks are the only way to specify the "behavior" of state elements. Synthesis tools will turn state element behaviors into state element instances.

#### D-flip-flop with synchronous set and reset example:

```

module dff(q, d, clk, set, rst);

input d, clk, set, rst;

output q;

keyword

reg q;

"always @ (posedge clk)" is key

to flip-flop generation.

always @ (posedge clk)

if (rst)

set

q \le 1'b0;

else if (set)

This gives priority to

clk -

q \le 1'b1;

reset over set and

rst

set over d.

else

q \le d;

On FPGAs, maps to native flip-flop.

endmodule

```

Spring 2013 How would you add an CE (clock enable) input?

Page 17

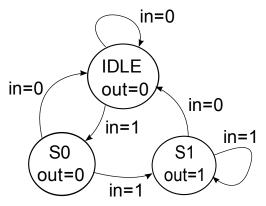

#### Finite State Machines

#### State Transition Diagram

#### Implementation Circuit Diagram

Holds a symbol to keep track of which bubble the FSM is in.

What does this one do?

Did you know that every SDS is a FSM?

clk state register combinational logic out

CL functions to determine output value and next state based on input and current state.

out = f(in, current state)

next state = f(in, current state)

Spring 2013 EECS150 - LecO6-CAD1

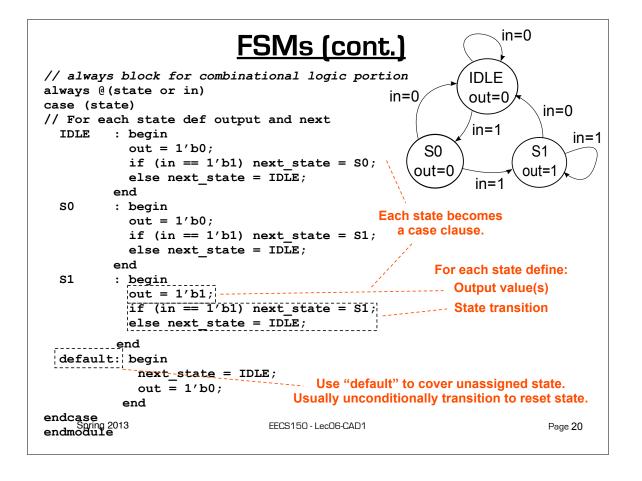

```

Finite State Machines

in=0

module FSM1(clk, rst, in, out);

IDLE

input clk, rst;

Must use reset to force

in=0

out=0

input in;

to initial state.

in=0

output out;

reset not always shown in STD -----

in=1

in=1

// Defined state encoding:

S<sub>0</sub>

S1

parameter IDLE = 2'b00; Constants local

out=0

out=1

parameter S0 = 2'b01;

- to this module.

parameter S1 = 2'b10;

reg out; ---- out not a register, but assigned in always block

reg [1:0] state, next state;

Combinational logic

signals for transition.

THE register to hold the "state" of the FSM.

// always block for state register

always @ (posedge clk)

if (rst) state <= IDLE;</pre>

else state <= next state;</pre>

A separate always block should be used for combination logic part of FSM. Next

state and output generation. (Always blocks in a design work in parallel.)

Spring 2013

EECS150 - Lec06-CAD1

Page 19

```

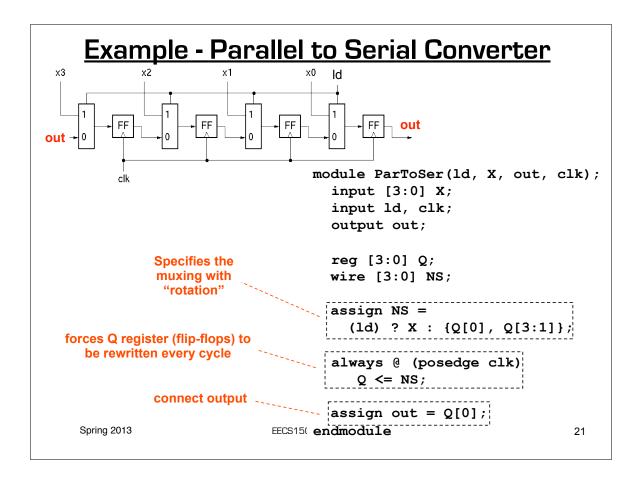

#### Parameterized Version

Parameters give us a way to generalize our designs. A module becomes a "generator" for different variations. Enables design/module reuse. Can simplify testing.

```

module ParToSer(ld, X, out, CLK);

parameter N = 4;

input [N-1:0] X;

input ld, clk;

Declare a parameter with

default value.

output out;

Replace all occurrences

Note: this is not a port.

reg out;

of "3" with "N-1".

reg [N-1:0] Q;

Acts like a "synthesis-

time" constant.

wire [N-1:0] NS;

ParToSer #(.N(8))

assign NS =

ps8 ( ... );

(ld) ? X : \{Q[0], Q[N-1:1]\};

ParToSer #(.N(64))

always @ (posedge clk)

ps64 ( ... );

Q \le NS;

Overwrite parameter N at

instantiation.

assign out = Q[0];

Spring 2013

EECS150 endmodule

```