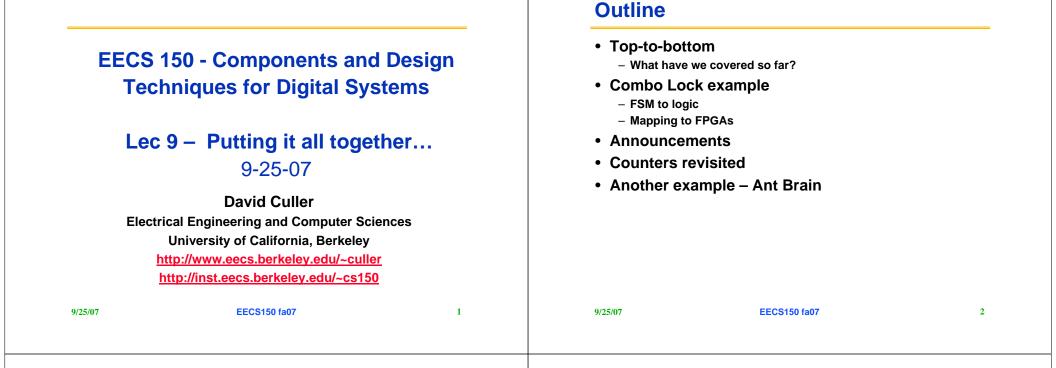

### Digital design - as we've seen it

### Where are we now?

- (Synchronous) Sequential systems

- Given datapath and control specifications

- Generate comb. logic for datapath

- » Minimize logic for efficient implementation

- Generate FSM for controller

- » Choose implementation, encoding

- » Generate logic for nextstate and output

- Describe datapath and controller in Verilog

- » structure, dataflow and behavior

- » Map onto gates or LUTs

- Seems like a good point to "test" your understanding!

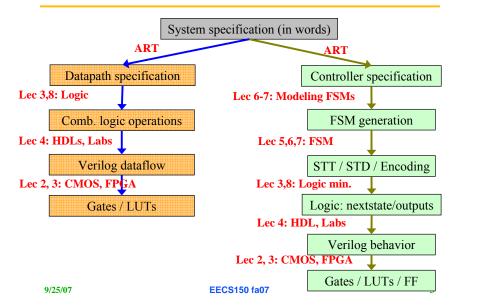

### **Representation of digital designs**

scope of CS 150

more depth than 61C

focus on building systems

5

- Physical devices (transistors, relays)

- Switches

- Truth tables

- Boolean algebra

- Gates

9/25/07

- Waveforms

- · Finite state behavior

- Register-transfer behavior

- Concurrent abstract specifications

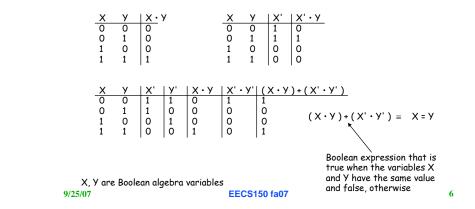

### Logic Functions and Boolean Algebra

Any logic function that can be expressed as a truth table can be written as an expression in Boolean algebra using the operators: ', +, and •

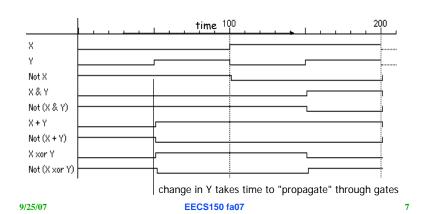

### **Waveform View of Logic Functions**

EECS150 fa07

- Just a sideways truth table

- But note how edges don't line up exactly

- It takes time for a gate to switch its output!

### An algebraic structure

- · An algebraic structure consists of

- a set of elements B

- binary operations { + , }

- and a unary operation { ' }

- such that the following axioms hold:

| 1. set B contains a | at least two elements, a, b, s                | such that a ≠ b                                     |

|---------------------|-----------------------------------------------|-----------------------------------------------------|

| 2. closure:         | a+b is in B                                   | a∙b isinB                                           |

| 3. commutativity:   | a + b = b + a                                 | a • b = b • a                                       |

| 4. associativity:   | a + (b + c) = (a + b) + c                     | a • (b • c) = (a • b) • c                           |

| 5. identity:        | a + 0 = a                                     | a • 1 = a                                           |

| 6. distributivity:  | $a + (b \bullet c) = (a + b) \bullet (a + c)$ | $a \bullet (b + c) = (a \bullet b) + (a \bullet c)$ |

| 7. complementarit   | ty: a + a' = 1                                | a • a' = 0                                          |

EECS150 fa07

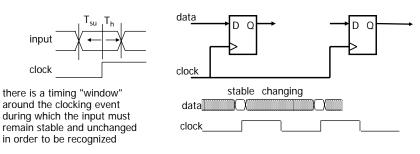

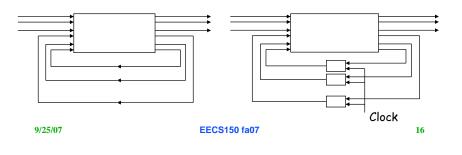

### **Timing Methodologies (cont'd)**

- Definition of terms

- clock: periodic event, causes state of storage element to change; can be rising or falling edge, or high or low level

- setup time: minimum time before the clocking event by which the input must be stable (Tsu)

- hold time: minimum time after the clocking event until which the input must remain stable (Th)

there is a timing "window" around the clocking event

in order to be recognized

clock

9/25/07

### **Axioms & theorems of Boolean algebra**

| Identity                             |                                                 |

|--------------------------------------|-------------------------------------------------|

| 1. $X + 0 = X$                       | 1D. $X \cdot 1 = X$                             |

| • Null                               |                                                 |

| 2. X + 1 = 1                         | 2D. $X \cdot 0 = 0$                             |

| <ul> <li>Idempotency:</li> </ul>     |                                                 |

| 3. X + X = X                         | 3D. X • X = X                                   |

| <ul> <li>Involution:</li> </ul>      |                                                 |

| 4. (X')' = X                         |                                                 |

| <ul> <li>Complementarity:</li> </ul> |                                                 |

| 5. X + X' = 1                        | 5D. X • X' = 0                                  |

| Commutativity:                       |                                                 |

| 6. $X + Y = Y + X$                   | $6D.  X \bullet Y = Y \bullet X$                |

| <ul> <li>Associativity:</li> </ul>   |                                                 |

| 7. $(X + Y) + Z = X + (Y + Z)$       | 7D. $(X \cdot Y) \cdot Z = X \cdot (Y \cdot Z)$ |

| 9/25/07 EEC                          | S150 fa07 10                                    |

### Axioms and theorems of Boolean algebra (cont'd)

EECS150 fa07

• Distributivity: 8.  $X \cdot (Y + Z) = (X \cdot Y) + (X \cdot Z)$  8D.  $X + (Y \cdot Z) = (X + Y) \cdot (X + Z)$ • Uniting: 9.  $X \cdot Y + X \cdot Y' = X$ 9D.  $(X + Y) \cdot (X + Y') = X$ • Absorption: 10.  $X + X \cdot Y = X$ 10D.  $X \cdot (X + Y) = X$ 11.  $(X + Y') \cdot Y = X \cdot Y$ 11D.  $(X \bullet Y') + Y = X + Y$ • Factoring: 12.  $(X + Y) \cdot (X' + Z) =$ 12D.  $X \cdot Y + X' \cdot Z =$  $(X + Z) \cdot (X' + Y)$  $X \bullet Z + X' \bullet Y$ • Concensus: 13.  $(X \bullet Y) + (Y \bullet Z) + (X' \bullet Z) = 13D. (X + Y) \bullet (Y + Z) \bullet (X' + Z) =$  $(X + Y) \cdot (X' + Z)$  $X \bullet Y + X' \bullet Z$

### Axioms and theorems of Boolean algebra (cont')

14D.  $(X \bullet Y \bullet ...)' = X' + Y' + ...$

• de Morgan's:

14.  $(X + Y + ...)' = X' \cdot Y' \cdot ...$

- generalized de Morgan's: 15.  $f'(X1, X2, ..., Xn, 0, 1, +, \bullet) = f(X1', X2', ..., Xn', 1, 0, \bullet, +)$

- establishes relationship between and +

### **Recall: What makes Digital Systems tick?**

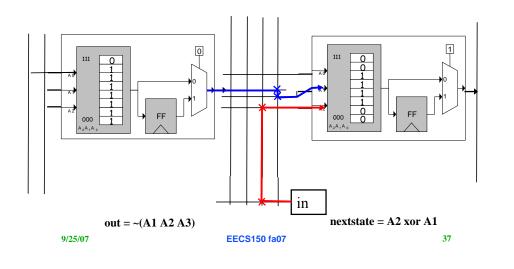

### **Sequential Logic Implementation**

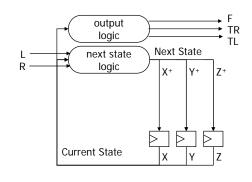

# Models for representing sequential circuits Finite-state machines (Moore and Mealy) Representation of memory (states) Changes in state (transitions) Design procedure State diagrams Implementation choice: counters, shift registers, FSM State transition table State encoding Combinational logic Next state functions Output functions

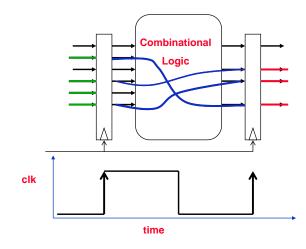

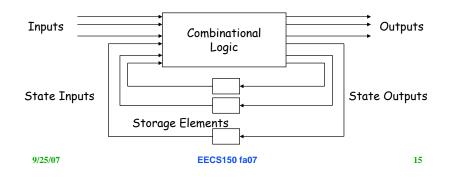

### **Abstraction of State Elements**

- Divide circuit into combinational logic and state

- · Localize feedback loops and make it easy to break cycles

- Implementation of storage elements leads to various forms of sequential logic

### Forms of Sequential Logic

- Asynchronous sequential logic state changes occur whenever state inputs change (elements may be simple wires or delay elements)

- Synchronous sequential logic state changes occur in lock step across all storage elements (using a periodic waveform - the clock)

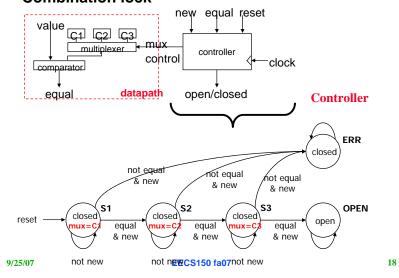

### **FSM** Representations

- States: determined by possible values in sequential storage elements

- Transitions: change of state

- Clock: controls when state can change by controlling storage elements

- Sequential Logic

- Sequences through a series of states

- Based on sequence of values on input signals

- Clock period defines elements of sequence

| 9/25/07 | EECS150 fa07 | 17 |  |

|---------|--------------|----|--|

|         |              |    |  |

### Example: FSM Design – Combo lock

### Combination lock

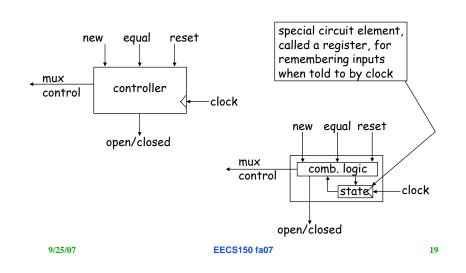

# Combo lock - controller implementation

• Implementation of the controller

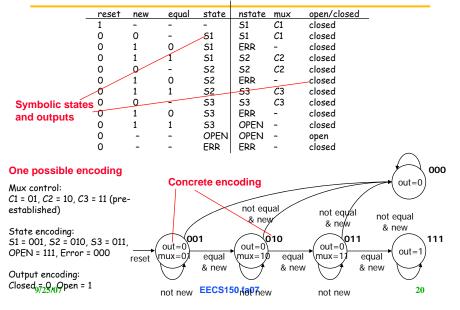

### **Combo Lock - State Encoding**

### **FSM** implementation

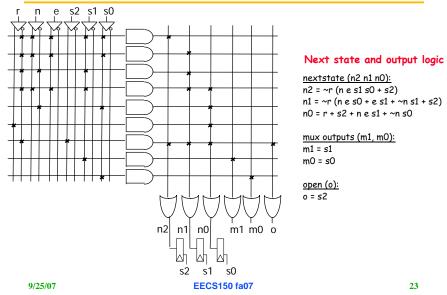

| Steps for the hardware designer:                       |    | reset | new     | equal | state                                           | nstate                                          | mux                              | open |                                     |

|--------------------------------------------------------|----|-------|---------|-------|-------------------------------------------------|-------------------------------------------------|----------------------------------|------|-------------------------------------|

| <ul> <li>Word specification</li> </ul>                 |    | (r)   | (n)     | (e)   | (s <sub>2</sub> s <sub>1</sub> s <sub>0</sub> ) | (n <sub>2</sub> n <sub>1</sub> n <sub>0</sub> ) | (m <sub>1</sub> m <sub>0</sub> ) | (0)  | Next state and output log           |

| <ul> <li>FSM design</li> </ul>                         |    | 1     | -       | -     |                                                 | 001                                             |                                  | 0    | nextstate (n2 n1 n0):               |

| <ul> <li>Encoding</li> </ul>                           |    | 0     | 0       | -     | 001                                             | 001                                             | 01                               | 0    | n2 = ~r (n e s1 s0 + s2)            |

| – Verification!                                        |    | 0     | 1       | 0     | 001                                             | 000                                             | 01                               | 0    | n1 = -r (n e s0 + e s1 + -n s1 + s) |

|                                                        |    | 0     | 1       | 1     | 001                                             | 010                                             | 01                               | 0    | n0 = r + s2 + n e s1 + ~n s0        |

| At this point, hand over to synthesis tools:           |    | 0     | 0       | -     | 010                                             | 010                                             | 10                               | 0    | <u>mux outputs (m1, m0):</u>        |

| <ul> <li>Describe FSM behavior in Verilog</li> </ul>   |    | 0     | 1       | 0     | 010                                             | 000                                             | 10                               | 0    | m1 = s1                             |

| <ul> <li>Synthesize controller</li> </ul>              |    | 0     | 1       | 1     | 010                                             | 011                                             | 10                               | 0    | mO = sO                             |

|                                                        |    | 0     | 0       | -     | 011                                             | 011                                             | 11                               | 0    | <u>open (o):</u><br>o = s2          |

| Good encoding                                          |    | 0     | 1       | 0     | 011                                             | 000                                             | 11                               | 0    |                                     |

| <ul> <li>Better performance</li> </ul>                 |    | 0     | 1       | 1     | 011                                             | 111                                             | 11                               | 0    | Take advantage of DC:               |

| - Fewer state bits                                     |    | 0     | -       | -     | 111                                             | 111                                             |                                  | 1    |                                     |

| <ul> <li>Possibility of state minimization</li> </ul>  |    | 0     | -       | -     | 000                                             | 000                                             |                                  | 0    |                                     |

| <ul> <li>Tools also try to figure this out</li> </ul>  |    | 0     | -       | -     | 100                                             |                                                 |                                  | -    | How do we get these:                |

|                                                        |    | 0     | -       | -     | 101                                             |                                                 |                                  | -    | •K-maps?                            |

| for this example, so through the logic synthesis store |    | 0     | -       | -     | 110                                             |                                                 |                                  | -    | •Tools<br>≻Espresso                 |

| For this example, go through the logic synthesis steps |    |       |         |       |                                                 |                                                 |                                  |      | >Synplicity                         |

| ideally, tools take care of all this).                 | 21 |       | 9/25/07 |       |                                                 | EECS                                            | S150 fa07                        |      | 22 22                               |

### Logic Implementation (on PLA)

### **Alternate logic implementations**

- PALs

- Multi-level circuits

**Example: Combo Lock**

- Library of gates for implementation technology

- LUTs on FPGA

- ...

9/25/07

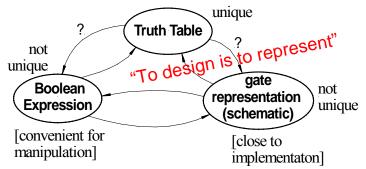

### **Alternate Logic Representations**

Theorem: Any Boolean function that can be expressed as a truth table can be written as an expression in Boolean Algebra using AND, OR, NOT.

How do we convert from one to the other?

| 9 | 0/25/07 | EECS150 fa07 | 25 |   |

|---|---------|--------------|----|---|

|   |         |              |    | J |

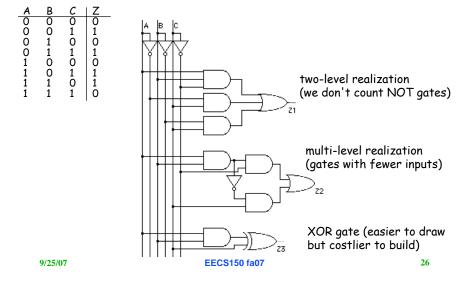

## Which realization is best?

- Reduce number of inputs

- literal: input variable (complemented or not)

- » approximate cost of logic gate is 2 transistors per literal

- Fewer literals means less transistors smaller circuits

- Fewer inputs implies faster gates

- Fan-ins (# of gate inputs) are limited in some technologies

- Reduce number of gates

- Fewer gates (and the packages they come in) means smaller circuits

- Reduce number of levels of gates

- Fewer level of gates implies reduced signal propagation delays

- How do we explore tradeoffs between increased circuit delay and size?

- Automated tools to generate different solutions

- Logic minimization: reduce number of gates and complexity

- Logic optimization: reduction while trading off against delay

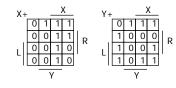

# Choosing different realizations of a function

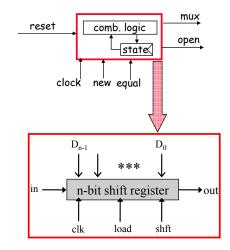

# Alternate Implementation: Controller based on Shift Register

- Previous implementation

- Comb. logic as gates (PLA)

- State bits in latches

- Alternative

- Shift reg to manipulate state

- Simplify comb. logic

9/25/07

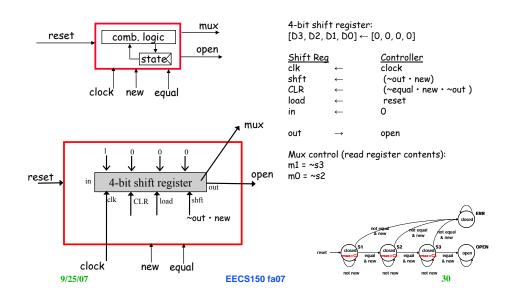

### **Controller using Shift Register**

| reset | new                 | equal | state            | nstate                                                         | mu×                              | open |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|---------------------|-------|------------------|----------------------------------------------------------------|----------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (r)   | (n)                 | (e)   | $(s_3s_2s_1s_0)$ | (n <sub>3</sub> n <sub>2</sub> n <sub>1</sub> n <sub>0</sub> ) | (m <sub>1</sub> m <sub>0</sub> ) | (o)  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1     | -                   | -     |                  | 1000                                                           |                                  | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0     | 0                   | -     | 1000             | 1000                                                           | 01                               | 0    | One-hot encoding scheme: state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0     | 1                   | 0     | 1000             | 0000                                                           | 01                               | 0    | transition is a shift right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0     | 1                   | 1     | 1000             | 0100                                                           | 01                               | 0    | Mux control:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0     | 0                   | -     | 0100             | 0100                                                           | 10                               | 0    | C1 = 01, C2 = 10, C3 = 11 (pre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0     | 1                   | 0     | 0100             | 0000                                                           | 10                               | 0    | established)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0     | 1                   | 1     | 0100             | 0010                                                           | 10                               | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0     | 0                   | -     | 0010             | 0010                                                           | 11                               | 0    | State encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0     | 1                   | 0     | 0010             | 0000                                                           | 11                               | 0    | 51 = 1000, 52 = 0100,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0     | 1                   | 1     | 0010             | 0001                                                           | 11                               | 0    | S3 = 0010, OPEN = 0001, Error =<br>0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0     | -                   | -     | 0001             | 0001                                                           |                                  | 1    | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0     | -                   | -     | 0000             | 0000                                                           |                                  | 0    | Output encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0     | -                   | -     | 11               |                                                                |                                  | -    | Closed = 0, Open = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0     | -                   | -     | 1-1-             |                                                                |                                  | -    | closed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0     | -                   | -     | 11               |                                                                |                                  | -    | not equal not equal since the second |

| 0     | -                   | -     | -11-             |                                                                |                                  | -    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0     | -                   | -     | -1-1             |                                                                |                                  | -    | reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0     | <u>-</u><br>9/25/07 | -     | 11               |                                                                | ECS150 fa07                      | -    | not new not new not new 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### Combo lock controller on shift reg

# How does the combo lock look on an FPGA?

- Latches

- implement shift register (chain of 4 latches)

- LUTs

- Combinational logic for out and mux control

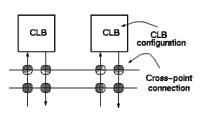

- Routing fabric

- Connect logical nets between CLBs

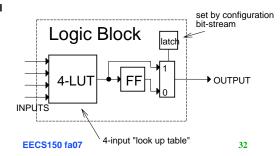

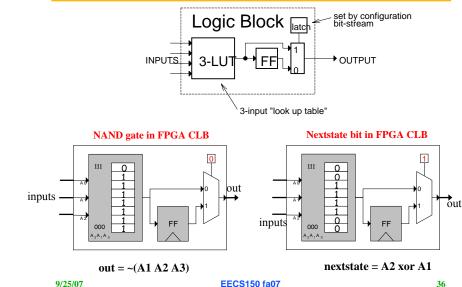

### **Inside the FPGA**

- Network of Combinational logic blocks, memory and I/O

- rich interconnect network

- special units multipliers, carry-logic

- CLBs

- 3 or 4-input look up table (LUT)

- implements combinational logic functions

- Register optionally stores output of LUT

- Logic on FPGA

- Configure LUTs (table of entries)

- Configure latches in CLB

- Program interconnect

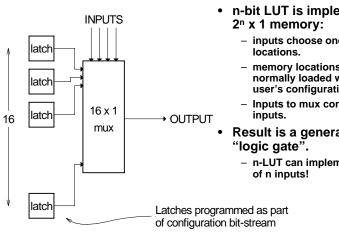

### LUT as general logic gate Example: 4-lut

|                                                   |              | ampi <del>o</del> . <del>4</del> -iui |

|---------------------------------------------------|--------------|---------------------------------------|

| <ul> <li>An n-lut as a direct</li> </ul>          | INPUTS       |                                       |

| implementation of a function                      | 0000         | F(0,0,0,0) < store in 1st latch       |

| truth-table.                                      | 0001         | F(0,0,0,1) < store in 2nd latch       |

| <ul> <li>Each latch location holds the</li> </ul> | 0010         | F(0,0,1,0) <                          |

| value of the function                             | 0011         | F(0,0,1,1) <                          |

| corresponding to one input                        | 0011         | _                                     |

| combination.                                      | 0100         | •                                     |

| Example: 2-lut                                    | 0101         | •                                     |

| INPUTS, AND OR                                    | 0110         |                                       |

|                                                   | 0111         |                                       |

|                                                   | 1000         |                                       |

|                                                   | 1001<br>1010 |                                       |

|                                                   | 1010         |                                       |

|                                                   | 1100         |                                       |

| Implements any function of 2 inputs.              | 1101         |                                       |

| How many of these are there?                      | 1110         |                                       |

| •                                                 | 1111         |                                       |

| How many functions of n inputs?                   |              |                                       |

| 9/25/07 EECS150 fa0                               | 7            | 33                                    |

|                                                   |              |                                       |

|                                                   |              |                                       |

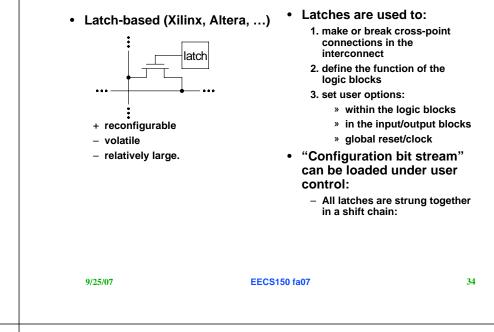

### **User Programmability**

### **4-LUT Implementation**

## · n-bit LUT is implemented as a

- inputs choose one of 2<sup>n</sup> memory

- memory locations (latches) are normally loaded with values from user's configuration bit stream.

- Inputs to mux control are the CLB

- Result is a general purpose

- n-LUT can implement any function

### **Configuring CLBs**

### **Configuring Routes**

### Sequential Systems – more examples

- Beat the combo lock example to death

- Direct FSM implementation

- Shift register

- » Multiple logic representations

- » gates to LUTs

### • Up next

9/25/07

- A few quick counter examples

- Another design problem Ant Brain

### Announcements/Reminders

- First mid term Thursday 9/27

- No notes (... to discuss)

- Review materials are in the HW4

- Review session tonight 8-10 642-WALK (9255)

- Trying to make the exams routine

- · Feel free to approach us with questions...

- No discussion Thurs, yes friday

- Lab 5 Where's the music?

- Normal lab lecture on Friday

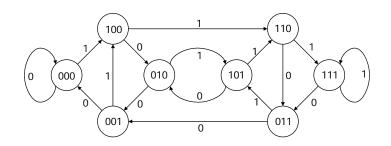

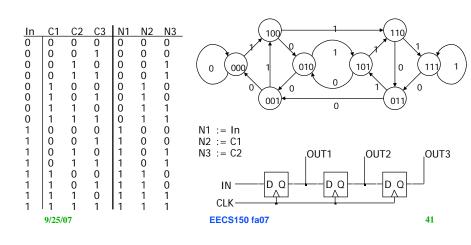

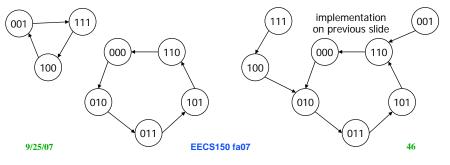

### Can Any Sequential System be Represented with a State Diagram?

• Shift Register

EECS150 fa07

Output values shown within state node

39

EECS150 fa07

**40**

38

OUT3

### **Counter Example**

### • Shift Register

Input determines next state

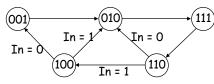

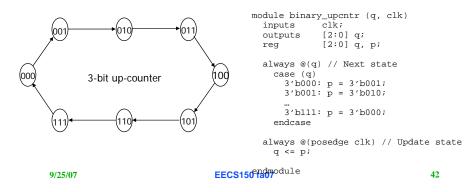

### **Counters are Simple Finite State Machines**

Counters

- Proceed thru well-defined state sequence in response to enable

- Many types of counters: binary, BCD, Gray-code

- 3-bit up-counter: 000, 001, 010, 011, 100, 101, 110, 111, 000, ...

- 3-bit down-counter: 111, 110, 101, 100, 011, 010, 001, 000, 111, ...

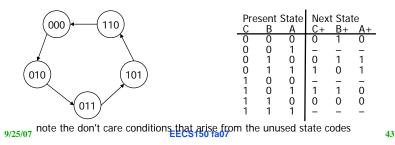

### **More Complex Counter Example**

- Complex Counter

- Repeats five states in sequence

- Not a binary number representation

- Step 1: Derive the state transition diagram

- Count sequence: 000, 010, 011, 101, 110

- Step 2: Derive the state transition table from the state transition diagram

# More Complex Counter Example (cont'd)

• Step 3: K-maps for Next State Functions

A+ := BC'

EECS150 fa07

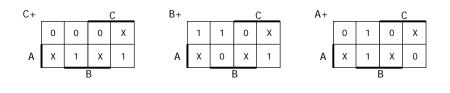

### Self-Starting Counters (cont'd)

Re-deriving state transition table from don't care assignment

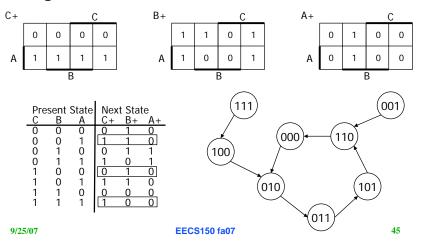

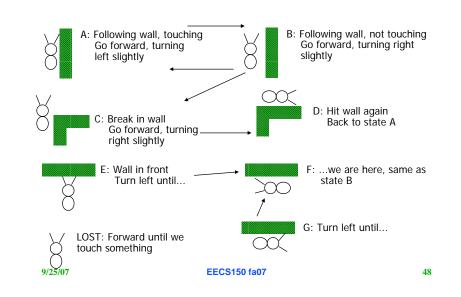

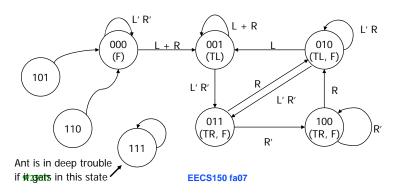

### Final Example: Ant Brain (Ward, MIT)

• Sensors: touching wall L and R antennae, 1 if in

keep the wall on the right

47

- F forward step, TL/TR turn • Actuators: left/right slightly find way out of maze

- · Goal:

- Strategy:

## **Self-Starting Counters**

- Start-up States

- At power-up, counter may be in an unused or invalid state

- Designer must guarantee it (eventually) enters a valid state

- Self-starting Solution

- Design counter so that invalid states eventually transition to a valid state

- May limit exploitation of don't cares

**Ant Behavior**

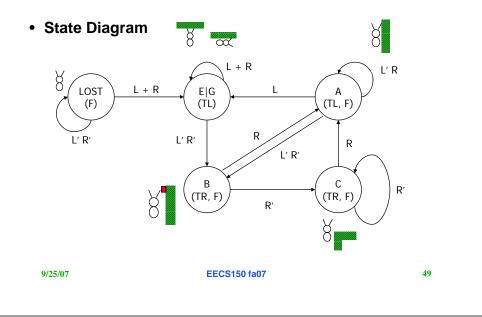

### **Designing an Ant Brain**

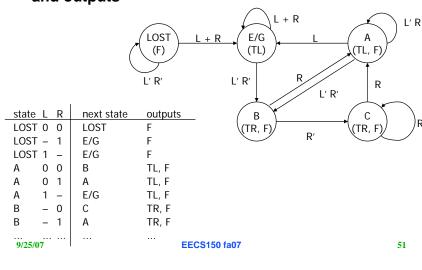

### **Synthesizing the Ant Brain Circuit**

- Encode States Using a Set of State Variables

- Arbitrary choice may affect cost, speed

- Use Transition Truth Table

- Define next state function for each state variable

- Define output function for each output

- Implement next state and output functions using combinational logic

- 2-level logic (ROM/PLA/PAL)

- Multi-level logic

- Next state and output functions can be optimized together

EECS150 fa07

50

| <b>Transition</b> | <b>Truth</b> | <b>Table</b> |

|-------------------|--------------|--------------|

• Using symbolic states and outputs

### **Synthesis**

9/25/07

• 5 states : at least 3 state variables required (X, Y, Z) – State assignment (in this case, arbitrarily chosen)

| state L R<br>X,Y,Z | next state | outputs<br>F TR TL + to synthesize | LOST - 000<br>E/G - 001<br>A - 010<br>B - 011<br>C - 100 |

|--------------------|------------|------------------------------------|----------------------------------------------------------|

| 000 00             | 000        | 1 0 0 these 6 functions            |                                                          |

| 000 0 1            | 001        | 100                                |                                                          |

|                    |            |                                    |                                                          |

| 010 00             | 011        | 101                                |                                                          |

| 010 01             | 010        | 101                                |                                                          |

| 010 10             | 001        | 101                                |                                                          |

| 010 11             | 001        | 101                                |                                                          |

| 011 0 0            | 100        | 1 1 0                              |                                                          |

| 011 0 1            | 010        | 1 1 0                              |                                                          |

| 9/25/07            |            | <br>EECS150 fa07                   | 52                                                       |

# Synthesis of Next State and Output Functions

| state inputs | next state | outputs |                                 |

|--------------|------------|---------|---------------------------------|

| X,Y,Z L R    | X+,Y+,Z+   | F TR TL |                                 |

| 000 00       | 000        | 100     |                                 |

| 000 - 1      | 001        | 100     |                                 |

| 0001-        | 001        | 100     |                                 |

| 00100        | 011        | 001     |                                 |

| 001 - 1      | 010        | 001     | e.g.                            |

| 0011-        | 010        | 001     | <b>U</b>                        |

| 010 00       | 011        | 101     | TR = X + Y Z                    |

| 010 01       | 010        | 101     | $X^{+} = X R' + Y Z R' = R' TR$ |

| 0101-        | 001        | 101     |                                 |

| 011 - 0      | 100        | 110     |                                 |

| 011 - 1      | 010        | 110     |                                 |

| 100 - 0      | 100        | 110     |                                 |

| 100 - 1      | 010        | 110     |                                 |

|              |            |         |                                 |

EECS150 fa07

### **Circuit Implementation**

• Outputs are a function of the current state only -Moore machine

EECS150 fa07

| Veril | oa | Sketch |

|-------|----|--------|

|       | 99 |        |

9/25/07

```

module ant_brain (F, TR, TL, L, R)

inputs

L, R;

F, TR, TL;

outputs

req

X, Y, Z;

assign F = function(X, Y, Z, L, R);

assign TR = function(X, Y, Z, L, R);

assign TL = function(X, Y, Z, L, R);

always @(posedge clk)

begin

X \leq function (X, Y, Z, L, R);

Y \leq function (X, Y, Z, L, R);

Z \leq function (X, Y, Z, L, R);

end

endmodule

```

### **Don't Cares in FSM Synthesis**

- What happens to the "unused" states (101, 110, 111)?

- · Exploited as don't cares to minimize the logic

- If states can't happen, then don't care what the functions do

- if states do happen, we may be in trouble

53

9/25/07

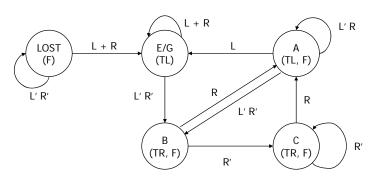

### **State Minimization**

- Fewer states may mean fewer state variables

- High-level synthesis may generate many redundant states

- Two state are equivalent if they are impossible to distinguish from the outputs of the FSM, i. e., for any input sequence the outputs are the same

- Two conditions for two states to be equivalent:

- 1) Output must be the same in both states

- 2) Must transition to equivalent states for all input combinations

### **Ant Brain Revisited**

• Any equivalent states?

| 9/25/07 | EECS150 fa07 | 57 | 9/25/07 | EECS150 fa07 | 58 |

|---------|--------------|----|---------|--------------|----|

|         |              |    |         |              |    |

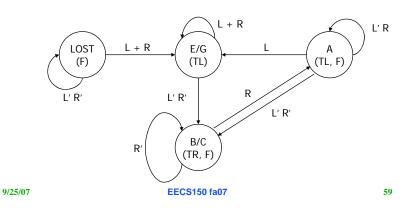

### **New Improved Brain**

- Merge equivalent B and C states

- Behavior is exactly the same as the 5-state brain

- We now need only 2 state variables rather than 3

### **New Brain Implementation**

| state | inputs | next state |   | outputs |   |

|-------|--------|------------|---|---------|---|

| X,Y   | LR     | X',Y'      | F | TRTL    |   |

| 00    | 0 0    | 00         | 1 | 0       | 0 |

| 00    | - 1    | 01         | 1 | 0       | 0 |

| 00    | 1 -    | 01         | 1 | 0       | 0 |

| 01    | 0 0    | 11         | 0 | 0       | 1 |

| 01    | - 1    | 01         | 0 | 0       | 1 |

| 01    | 1 -    | 01         | 0 | 0       | 1 |

| 10    | 0 0    | 11         | 1 | 0       | 1 |

| 10    | 0 1    | 10         | 1 | 0       | 1 |

| 10    | 1 -    | 01         | 1 | 0       | 1 |

| 11    | - 0    | 11         | 1 | 1       | 0 |

| 11    | - 1    | 10         | 1 | 1       | 0 |

|       |        |            |   |         |   |

EECS150 fa07

### **Sequential Logic Implementation Summary**

EECS150 fa07

- Models for representing sequential circuits

- Abstraction of sequential elements

- Finite state machines and their state diagrams

- Inputs/outputs

- Mealy, Moore, and synchronous Mealy machines

- · Finite state machine design procedure

- Deriving state diagram

- Deriving state transition table

- Determining next state and output functions

- Implementing combinational logic

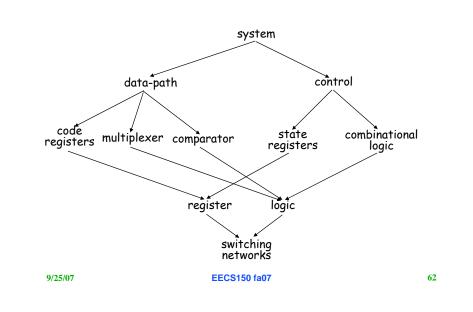

### **Design hierarchy**

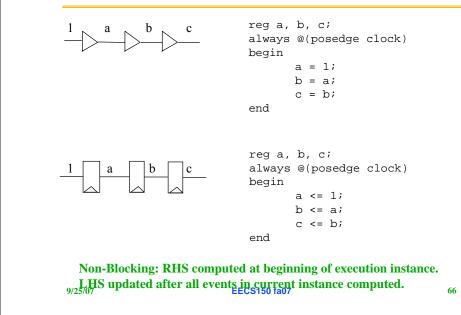

### **Final Word: Blocking Vs Non-Blocking**

- · Two types of procedural assignments

- Blocking

- Non-Blocking

- · Why do we need them

- Express parallelism (not straight line C)

- Synchronous system

- All flip-flops clock data simultaneously

- How do we express parallelism in this operation?

9/25/07

Good luck on the Midterm...

### A Simple Shift Register

reg a, b, c; reg a, b, c; always @(posedge clock) always @(posedge clock) begin a = 1; a = 1; always @(posedge clock) b = a;b = a;c = bialways @(posedge clock) end c = b; **Probably not what you want!** What order does this run? reg a, b, c; reg a, b, c; always @(posedge clock) always @(posedge clock) begin a <= 1; a <= 1; always @(posedge clock) b <= a; b <= a; c <= b; always @(posedge clock) c <= b; end This works too...<sub>65</sub> This works EECS150 fa07 9/25/07

### **The Circuit**